Finite State Machine - ECE Users Pages

advertisement

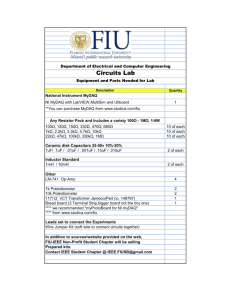

Finite State Machine Lab Finite State Machine Goal: The goal of this experiment is to reinforce state machine concepts by having students design and implement a state machine using simple chips and a protoboard. This experiment also introduces students to basic physical components. Contents: Background Experiment Appendix Page 1 Page 2 Page 10 Equipment Needed 74LS00: quad 2-input NAND (http://www.ti.com/lit/ds/symlink/sn7400.pdf) 74LS04: hex inverter (NOT) [14-pin] (http://www.ti.com/lit/ds/symlink/sn7404.pdf) 74LS74: dual D-flip flop [14-pin] (http://www.ti.com/lit/ds/symlink/sn74ls74a.pdf) 74LS138: 3-to-8 line decoder; (http://www.ti.com/lit/ds/symlink/sn74ls138.pdf) gate inverting [14-pin] [16-pin] Be aware that the decoder IC has 16 pins rather than 14. Therefore, be mindful of the pin locations especially for the 4 corner pins (1, 8, 9 and 16). For the 14-pin part, the corner pins would be (1, 7, 8 and 14) Logic gates used in your own design Jumper wires myDAQ Background Notation and Definitions: States: A = 00, B = 01, C = 10, D =11 where the states are defined by the values stored in the registers; for example, State B corresponds to S1S0 = 01 where S1 is the value of Register 1 and S0 is the value of Register 0. The next state for values of the registers is defined by NSi for Register i. For example, if the current state is B and the next state is C, then S1S0 = 01 and NS1 = 1 and NS0 = 0. External input: The external input in this circuit is denoted as “X.” 3 to 8 Decoder: In Figure 1 below, signals ~ represent the inputs and ~ represent the outputs. The cross bars over the outputs mean these outputs are negative low logic so the outputs are inverted. In this particular chip, represents the most significant bit (MSB) of a binary number and represents the least significant bit (LSB); for example, and input of 011 is Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 1 Finite State Machine Lab designated as in your design. = 011. The 74138 decoder has inverted outputs so take that into account 3:8 Encoder Figure 1 3:8 Encoder Pin Connection Diagram: It is critically important you label your diagram with pin and package numbers. You will have 3-5 ICs on the board, each needing power and ground, with multiple wires connecting each. Without labelling your pins ahead of time, it will be hard to construct and even harder to troubleshoot. Experiment The following information will make your progress through the lab much smoother if you can follow it. 1. In this lab write up, the signal names are writing in bold italic fonts for your convenience. 2. When you insert IC chips, do not bent pins. Always double check after you insert an IC. 3. Use consistent colors, especially for 5V and GND signals. For example: orange/red color for power and green colored wires for GND. 4. Utilize the Power and GND buses (red and blue lined) on the top and bottom of the breadboard. A) Initial steps a. It is helpful to make a habit of connecting your Vcc and ground to the buses of your breadboard. It’s HIGHLY recommended that you connect +5V and DGND to the + buses (red lined) and the – buses (blue lined) respectively on the breadboard. Since some of these chips have connections that have to be made on both sides, it is helpful to have both Vcc and ground on both the top and the bottom of the board. B) Setting up the decoder Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 2 Finite State Machine Lab a. Insert the decoder into your breadboard and connect the Vcc and GND pins to +5V and DGND buses respectively. Since this circuit has many connections, these “standard” connections should be as out of the way as possible. Use the smallest wires that will connect the pins. These wires should be nearly flush with the breadboard. Be sure that no pins are bent after insertion. You will need to use several chips in this project, so keep them at the same orientation when you plug them into the board. b. This decoder has 3 enable pins, two enable low, one enable high. The pins need to be connected to ground (enable low) and the E3 pin needs to be connected to Vcc. Since the decoder will always be enabled for this lab, use as short wires as possible to keep them out of your way. c. The decoder is now powered and enabled. You can test it by giving it a three-bit input to , , and observing the outputs ~ . Remember, the 74138 gives inverted outputs which mean that all outputs but the one selected will output a high voltage. This makes it easy to connect to NAND and NOR gates. d. For these state machines, we will be giving a single bit as input from the myDAQ. Connect the digital output pin of the myDAQ DIO0 to pin of the decoder. The other two inputs will come from the current state, outputs of the DFF (D flipflops). Table 1 summarizes the initial setup connections for the decoder in order for it to function properly. Table 1 Decoder Basic Setup Signal Name From Pin Number Signal Name To Pin Number Decoder MyDAQ/Board GND DGND Decoder MyDAQ/Board Vcc 5V Decoder Board DGND Decoder Board E3 5V Decoder MyDAQ DIO0 C) Set up other integrated circuit chips that contain the gates you would need to implement the state machines as in park B and D. Do not forget to connect power and ground pins. It’s recommended that you leave enough space for inserting at least 2 IC chips (such as a NAND gate chip and a NOT gate chip) between the Decoder chip and the D flip flop (DFF) chip. Come back to connect the chips in this section to DFF and Decoder after you finish part D below. D) Connecting the D flip flop a. Insert the D flip flop (7474) IC into the breadboard. In order to simply the wiring, it may be wise to leave room between the two for any logic chips you use in your design. b. Connect Vcc and ground. c. We will not be using the SET pins; 1 (refer to the pin assiment diagrams for the D flip flop in Appendix, so we will connect these to Vcc. If we Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 3 Finite State Machine Lab wanted the option to set the D-flip flops to 1, we could bring these pins of the Dflip flop low. d. We will be using digital I/O pins of the myDAQ to act as the clock and clear/reset. Connect the clock signals 1CP and 2CP (Pin 3 and 11) to DIO2 in the MyDAQ. Connect the reset signals 1 (pin 1 and 13) to unused DIO1. Remember, since the this is inverted clear, we need to keep those pins at logic High unless we want to reset both flip flops to zero, in which case we will change the input to 0. e. Connect the DFF outputs, 1Q and 2Q, to DIO6 and DIO7 of the MyDAQ respectively. f. Now the DFF is powered and functional. Table 2 summarizes the initial setup connections for the flip flops in order for them to function properly. Table 2 DFF Basic Setup Signal Name From Pin Number Signal Name To Pin Number DFF MyDAQ/Board GND DGND DFF MyDAQ/Board Vcc 5V DFF Board 5V 1 and 1CP and 2CP DFF MyDAQ DIO2 DFF MyDAQ DIO1 1 and DFF MyDAQ 1Q DIO6 MyDAQ 2Q DIO7 E) Building the Example State Machine (3 state) a. The state transition diagram for this state machine is shown below as Figure 1. X=1 A (00) X=0 X=1 X=1 C (10) X=0 B (01) X=0 Figure 2 State Transition Diagram Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 4 Finite State Machine Lab b. The truth table is shown below. Input X is that is controlled by DIO0. State S1 S0 X New State NS1 NS0 A 0 0 0 B 0 1 A 0 0 1 A 0 0 B 0 1 0 C 1 0 B 0 1 1 A 0 0 C 1 0 0 C 1 0 C 1 0 1 A 0 0 -- 1 1 0 -- -- -- -- 1 1 1 -- -- -- c. Label the pins you are going to use on the schematic below. Figure 3 Circuit Diagram for Example State Machine (note: Vcc, ground, etc. are not shown) d. e. f. g. h. i. Insert NAND IC (7400) Connect Vcc and ground. Using the pin diagram, make the needed connections. Don’t forget that the decoder is using inverted outputs! Test the state machine using the state transition diagram (Figure 1). Fill out the following table and test it out. Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 5 Finite State Machine Lab To test your circuit: set the input and then toggle the clock. 1. reset the DFF by setting DIO1 to Low which would set all outputs to logic 0. 2. set DIO1 to logic High again so the DFFs are ready to be used. 3. Set your input X which is currently connected to DIO0 to the correct level. For example, in Table 3 below, the input is zero. See Figure 4. Now the decoder’s inputs would be = 000. 4. Then toggle the Clock control bit which is DIO2. Toggle means set to low and then high or vise versa. In this case, we set the clock signal to logic Low and then push High 5. As soon as you push the Clock to High, pin DIO7 and DIO6 which are connected to S1 and S0, should change to the new state, B, per your implementation. 6. Use the same test procedure for the 2nd state machine implementation as well. 7. Remember by changing the input alone, the output should not change. You have to toggle the Clock signal so the new inputs can be clocked in. Figure 4 Initial User Interface Table 3 State Machine 1 Output State Input A 0 State Input 1 State Input State 1 Instructor/TA Initials: ______________ Input 0 State Input 0 State Input State 0 Date: ___________ Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 6 Input 1 State Finite State Machine Lab F) Designing and Building a State Machine a. The state machine will be based on the below state transition diagram X=0 A (00) X=1 B (01) X=0 X=1 X=1 X=0 X=0 D (11) X=1 C (10) Figure 5 State Transition Diagram 2 b. Fill out the truth table below. Input X is from your MyDAQ DIO0. NS1 represents the next state of S1. STATE S1 S0 X NEW STATE NS1 NS0 A 0 0 0 A 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 c. Design the state machine. Some tips for selecting the gates: i. Decoders using inverted outputs and NANDs are functionally the same as decoders using non-inverted outputs and ORs. ii. NANDs can be used as inverters. Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 7 Finite State Machine Lab d. Draw the circuit below (in the same manner as figure 2) and label the pins you are going to use. e. Insert the needed logic chips and connect Vcc and ground. f. Make the needed connections and test the circuit using the state transition diagram. g. Fill out the table below Table 4 State Machine 2 Output State Input A 0 State Input 1 State Input 1 State Input 1 State Input 0 State Input State 1 Instructor/TA Initials: ______________ Date: ___________ Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 8 Input 1 State Finite State Machine Lab Appendix Decoder IC (74HC138): Quad Dual-Input NAND Gate (7400) Register (D-FlipFlop) IC (74HC74): Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 9 Finite State Machine Lab NOT Gate IC (74HC04) or (SN74LS04N): Bonnie H. Ferri, School of Electrical and Computer Engineering, Georgia Tech (v1.1) 10