ISSN: 2277 – 9043

International Journal of Advanced Research in Computer Science and Electronics Engineering (IJARCSEE)

Volume 2, Issue 4, April 2013

DESIGNING OF CMOS OP-AMP USING REVERSE NESTED

MILLER COMPENSATION TECHNIQUE

TO IMPROVE GAINBANDWIDTH AND LOADING CAPACITY

Manorama Mishra1, Prof. Rajesh Nema2

Abstract – An Operational Amplifier is a direct-coupled

high-gain amplifier usually consisting of one or more differential

amplifiers followed by a level transistor and output stage. The

op-amp has become one of the most versatile and important

building blocks in analog circuit design. This paper proposed an

approach to design analog cmos op-amp using reverse nested

miller compensation technique to improve settling behaviour,

gain bandwidth and loading capacity. Settling performance of

operational amplifiers is of great importance in analog

signal-processing application.

.. (1)

Where the dc gain is given as AV=gm1R1gm2R2gm3R3 and the

dominant pole is

Index Terms – operational amplifier ,reverse nested miller

Compensation ,gain bandwidth.

..2

I. INTRODUCTION

The unity gain frequency is

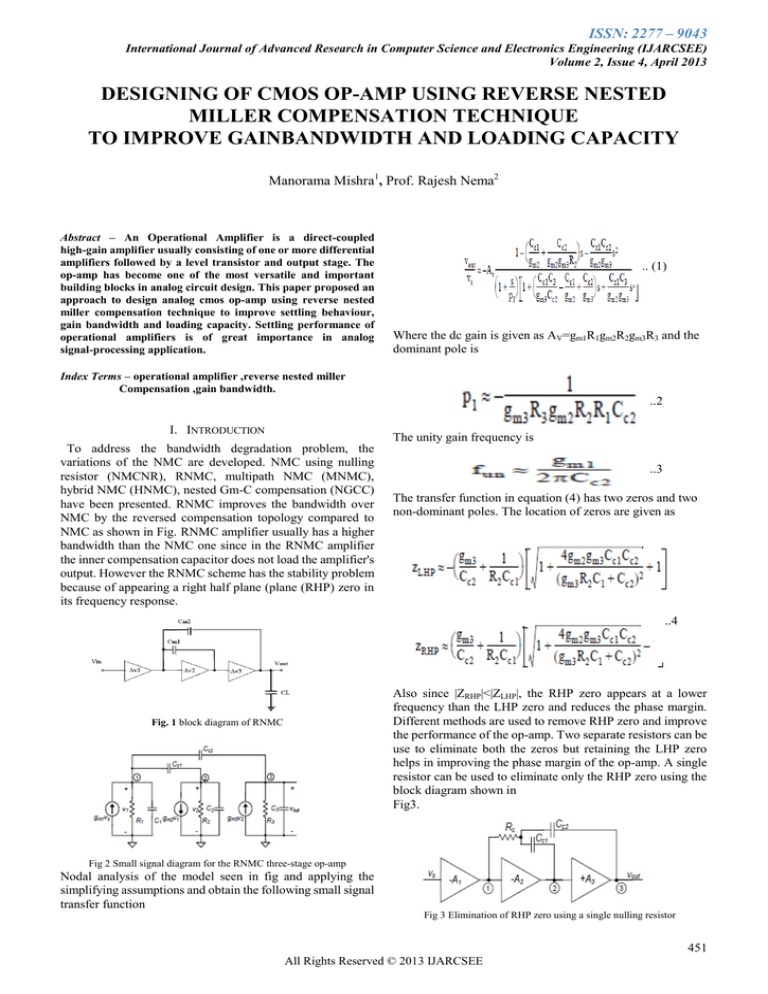

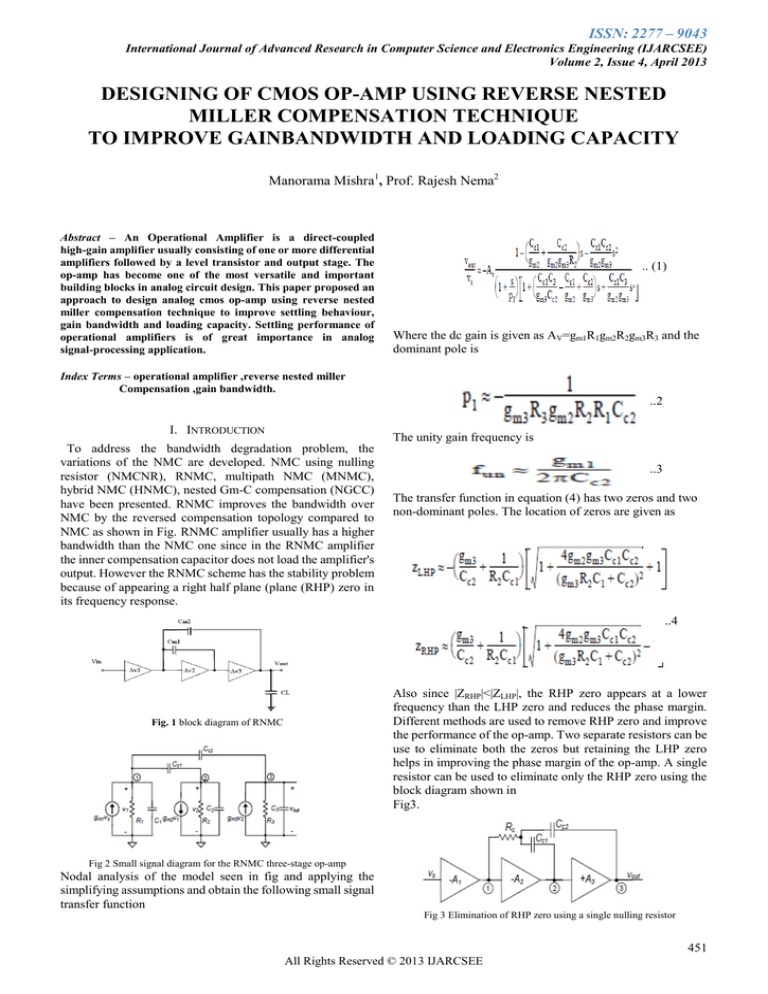

To address the bandwidth degradation problem, the

variations of the NMC are developed. NMC using nulling

resistor (NMCNR), RNMC, multipath NMC (MNMC),

hybrid NMC (HNMC), nested Gm-C compensation (NGCC)

have been presented. RNMC improves the bandwidth over

NMC by the reversed compensation topology compared to

NMC as shown in Fig. RNMC amplifier usually has a higher

bandwidth than the NMC one since in the RNMC amplifier

the inner compensation capacitor does not load the amplifier's

output. However the RNMC scheme has the stability problem

because of appearing a right half plane (plane (RHP) zero in

its frequency response.

..3

The transfer function in equation (4) has two zeros and two

non-dominant poles. The location of zeros are given as

..4

Also since |ZRHP|<|ZLHP|, the RHP zero appears at a lower

frequency than the LHP zero and reduces the phase margin.

Different methods are used to remove RHP zero and improve

the performance of the op-amp. Two separate resistors can be

use to eliminate both the zeros but retaining the LHP zero

helps in improving the phase margin of the op-amp. A single

resistor can be used to eliminate only the RHP zero using the

block diagram shown in

Fig3.

Fig. 1 block diagram of RNMC

Fig 2 Small signal diagram for the RNMC three-stage op-amp

Nodal analysis of the model seen in fig and applying the

simplifying assumptions and obtain the following small signal

transfer function

Fig 3 Elimination of RHP zero using a single nulling resistor

451

All Rights Reserved © 2013 IJARCSEE

ISSN: 2277 – 9043

International Journal of Advanced Research in Computer Science and Electronics Engineering (IJARCSEE)

Volume 2, Issue 4, April 2013

II. PROPOSED MODEL

In This paper we are comparing RNMC with previous

techniques of op-amp designing and in previous techniques

NMC was the best technique ,that’s why we are comparing

RNMC and NMC. we proposed an approach to design analog

cmos op-amp using reverse nested miller compensation

technique to improve settling behaviour, gain bandwidth and

loading capacity. settling performance of operational

amplifiers is of great importance in analog signal-processing

application.

Objective of this work to analysis different two stages and

multistage cmos op-amp topologies, to handel the higher

value of capacitive load with optimum value of settling time

and power consumption. To Designing CMOS Op-amps with

fast settling time and low power consumption with higher

value of capacitive load is a very challenging problem.

Power consumption can be reduced by scaling the supply

voltage, but the dynamic range and speed also decreases. The

design of a high drive buffer has different constrains from

those of low power or general purpose Op-Amps. A high

drive buffer is needed to drive capacitive loads up to 1nF or

higher.

Settling time‖ is defined as the duration from an ideal step

input until the output of the amplifier enters and remains

within a specified error band related to the amplitude of the

pulse and the expected final settling value.

It can be separated into three parts:

(1) The delay

(2) The slew, and recovery and

(3) Linear settling.

In this analysis, AC signal is applied at the one input

terminal and another input terminal is ground, schematic of

the op-amp for AC analysis shown in figure 5. Simulation is

done by tanner tool and LT-spice. After simulation of

schematic of op-amp, net-list is generated. In this net-list

include 0.35µ technology file and 0.5μ technology file, input

signal and output print command. The output results gain and

phase plot is shown in figure 5.

In transient analysis, op-amp is used as voltage follower. One

input terminal connected to the output and pulse signal

applied to another terminal, shown in figure. Simulation is

done by tanner tool and LT-spice. After simulation, net-list is

generated. In this net-list include 0.35µ technology file and

0.5μ technology file, input signal and output print command.

Output waveform is shown in figure 6. Settling time is defined

as the time taken by the output to settle 98% of its final value.

Parameters

Ahuja

design

NMC

RNMC

Gain margin

90dB

100dB

72dB

Phase margin

70dB

70dB

80dB

Power consumption

37.92mW

2.16mW

178.5μW

Gain bandwidth

4.5Mhz

3.8Mhz

4.8Mhz

Settling time for 30pf

617,7n

888.35n

3.02u

Fig 5. Comparisons b/w different technique for different parameter

Fig 6. gain and phase plot of RNMC

Fig .4 Three stage op-amp with RNMC

III.

RESULT AND DISCUSSION

Different types of configurations are used to simulate the

Operational Amplifier. At the input of the Op-amp different

signals are applies to simulate and get the output results. In

the spice net-list model file of 0.35µ technology is to be

included.

452

All Rights Reserved © 2013 IJARCSEE

ISSN: 2277 – 9043

International Journal of Advanced Research in Computer Science and Electronics Engineering (IJARCSEE)

Volume 2, Issue 4, April 2013

[6] F. C. Nunes and J. E. Franca, ―Successive-approximation

tuning of monolithic continuous-time filters,‖ Electron. Lett.,

vol. 28, no. 18, pp.1696–1697, Aug. 1992.

[7] H. Yamazaki, K. Oishi, and K. Gotoh, ―An accurate center

frequency tuning-scheme for 450-kHz CMOS G � C

bandpass filter,‖ IEEE J. Solid-State Circuits, vol. 34, pp.

1691–1967, Dec. 1999.

[8] W. H. Press, S. A. Teukolsky, W. T. Vetterling, and B. P.

Flannery, Numerical Recipes in C. New York: Cambridge

Univ. Press, 1992.

[9] P. E. Allen and D. R. Holberg, CMOS Analog Circuit

Design. New York: Oxford Univ. Press, 1987.

[10] R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit

Design, Layout, and Simulation. Piscataway, NJ: IEEE Press,

1998.

Mishra1,

Department of Electronics &

Communication Engg,, M.Tech NRI Institute of Information

Science & Technology, Bhopal, India,

Manorama

Fig7. Step response of RNMC

IV. CONCLUSION

The NMC and RNMC amplifiers are simulated by

referring to a standard 0.35μm cmos technology. In NMC

typical load capacitance CL=30pf has been considered.

Settling time at the 30pf is 888.35n which is three times more

than conventional three stage op-amp and GBW is 3.8 MHz.

But as the load increases negative peaks are more as shown

figure .Power consumption will also increase as. We can use

NMC for high value of capacitive load but settling time and

power consumption will be more as compared to convention

three stage op-amps. RNMC improves the bandwidth over

NMC by the reversed compensation topology compared to

NMC.

Prof.

Rajesh

Nema2, Department of Electronics &

Engg,, H.O.D NRI Institute of Information

Communication

Science & Technology,

Bhopal, India,

After simulation it is concluded that RNMC is more stable for

high value of load capacitance than all other design and power

consumption is also reduced. But this two topology have more

settling time as compared to two stage op-amp with buffered

version.

REFERENCES-:

[1] Rosario Mita, Gaetano Palumbo and Salvatore Pennisi,

―Design Guidelines for Reversed Nested Miller

Compensation in Three-Stage Amplifiers,‖ IEEE

TRANSACTIONS ON CIRCUITS AND SYSTEMS—II:

ANALOG AND DIGITAL SIGNAL PROCESSING, VOL.

50, NO. 5, pp.227-233,MAY 2003..

[2] C. S. Park and R. Schaumann, ―Design of a 4-MHz analog

integrated CMOS transconductance-C bandpass filter,‖ IEEE

J. Solid-State Circuits,vol. 23, pp. 987–996, Aug. 1988.

[3] P. M. VanPeterghem and R. Song, ―Tuning strategies in

high-frequency integrated continuous-time filters,‖ IEEE

Trans. Circuits Syst., vol. 36,pp. 136–139, Jan. 1989.

[4] R. Sadkowski, ―Tuning monolithic continuous-time

leapfrog filter structures,‖Master thesis, Texas A&M Univ.,

Dallas, Dec. 1992.

[5] F. C. Nunes and J. E. Franca, ―Continuous-time leapfrog

filter with precise successive-approximation tuning,‖ in IEEE

Int. Symp. on Circuits and Systems, vol. 2, 1993, pp.

1271–1273.

453

All Rights Reserved © 2013 IJARCSEE