Practice Questions for Exam 2 in CSCI 320

advertisement

Practice Questions for Exam 2 in CSCI 320

Overview

The focus of this portion of the class has been on understanding the hardware components of a

simple processor. We have expressed that understanding largely by building Verilog models of

these components beginning with a binary counter and ending with a control unit. We will

finish this effort with a complete model of the Smotherman machine but that won’t occur until

after this exam.

Much of the material covered in this test was not taken from our textbook. That material can

be found in the lecture slides and in the Smotherman paper. You are also responsible for Ch 4

of your textbook.

Verilog

1. What is the difference between these two operators = and <=?

2. Explain the difference between behavioral and structural modeling in Verilog.

3. Identify at least 3 errors in the Verilog modules below.

module simpleALU(input [31:0] A, B, input [2:0] F,

output reg [31:0] Y);

…

endmodule

module alu_simpleTestbench();

wire [10:0] inA, inB;

wire

[2:0] sel;

reg

[31:0] outY;

simpleALU dut(sel, outY, inA, inB);

initial

{sel, inA, inB} = 0;

$monitor("sel=%h, inA=%h, inB=%h outY=%h", sel, inA);

#10 sel = 3'b010;

{inA, inB} = 16'h0000_0000_0000_0000;

#10 sel = 3'b110;

{inA, inB} = 16'h0000_0000_FFFF_FFFF;

endmodule

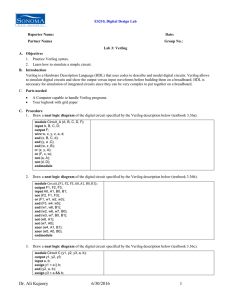

Verilog Modeling

1. Draw a schematic of the circuit defined in each Verilog module below.

1. module mystery1(input a, b, c,

output

y);

assign y = ~a & ~b | ~a & ~c | ~b & ~c;

endmodule

2.

module mystery2(input [3:0] a,

output [3:0] y);

assign y =

endmodule

3.

~a;

module mystery3(input [3:0] d0, d1,

input

s,

output [3:0] y);

assign y = s ? d1 : d0;

endmodule

4. module mystery4(

output co, s,

input ci, a, b);

wire a_xor_b;

wire a_and_b;

wire ci_and_a_xor_b;

xor u1(

and u2(

and u3(

or u4(

xor u5(

endmodule

a_xor_b, a, b );

a_and_b, a, b );

ci_and_a_xor_b, ci, a_xor_b );

co, a_and_b, ci_and_a_xor_b );

s, ci, a_xor_b );

5. module mystery5(input clk,

input reset,

input [3:0] d,

output reg [3:0] q);

always @ (posedge clk, posedge reset)

if (reset) q <= 4'b0;

else

q <= d;

endmodule

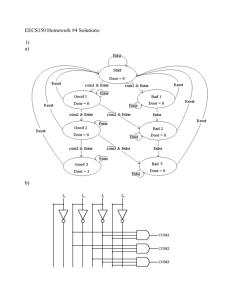

2. Sketch the state transition diagram for the FSM described by the Verilog code below.

module fsm (input clk, reset,

input a, b,

output y);

reg [1:0] state, nextstate;

parameter

parameter

parameter

parameter

S0

S1

S2

S3

=

=

=

=

2’b00;

2’b01;

2’b10;

2’b11;

always @ (posedge clk, posedge reset)

if (reset) state <= S0;

else

state <= nextstate;

always @ (*)

case (state)

S0: if(a ^

else

S1: if(a &

else

S2: if(a |

else

S3: if(a |

else

endcase

b) nextstate

nextstate

b) nextstate

nextstate

b) nextstate

nextstate

b) nextstate

nextstate

=

=

=

=

=

=

=

=

S1;

S0;

S2;

S0;

S3;

S0;

S3;

S0;

assign y = (state==S1) | (state == S2);

endmodule

3. Implement a JK flip-flop in Verilog.

Memory

1. Define and contrast ROM and RAM.

2. Does the following Verilog module represent RAM or ROM? What is the size of this

memory?

module memory (input [1:0] a, output reg [2:0] b);

always @ (a)

case (a)

2’b00 b <= 3’b011;

2’b01 b <= 3’b000;

2’b10 b <= 3’b011;

2’b11 b <= 3’b111;

endcase

endmodule

4. A memory has 1k words. Each word contains 16 bits. How many bytes are contained in this

memory?

5. A computer has 64K bytes of main memory addressable as 8 bit words. How many bits wide

is the Program Counter?

6. What is the name and function of the component below.

7. A digital computer has a memory unit with 32 bits per word. The instruction set consists of

110 different operations. All instructions have an operation code part and two address fields:

one for a memory address and one for a register address. This machine has eight generalpurpose, user-addressable registers. Registers may be loaded directly from memory, and

memory may be updated directly from the registers. Direct memory-to-memory data

movement operations are not supported. Each instruction is stored in one word of memory.

a. How many bits are needed for the opcode?

b. How many bits are needed to specify the register?

c. How many bits are left for the memory address part of the instruction?

d. What is the maximum allowable size for memory (assuming all of memory is addressable in

an instruction)?

e. What is the largest unsigned binary number that can be accommodated in one word of

memory?

8. How many bits are required to address a 4M x 16 main memory if:

a. main memory is byte addressable?

b. main memory is word addressable?

FSM

1. Design a FSM to recognize the sequence: 1011. Represent your design as both a FSM

diagram and in Verilog.

Hardware

1. Explain the difference between a D flip-flop and a JK flip-flop.

2. Explain the difference between a flip-flop and a latch.

3. Explain how the select signals are used in the ALU diagrammed below. What 2-bit select

signal would produce an output of A AND B?

4. For the adder/subtractor shown below, explain how the subtraction mode works.

Chapter 4 and Smotherman paper

1. Explain the fetch-decode-execute cycle for either the Smotherman machine or MARIE. Your

explanation should include what is happening in the various registers.

2. In the Smotherman machine or MARIE, explain why the MAR is a different width (stores a

different number of bits) than the ACC.

3. If the Smotherman machine runs at 1MHz, how long does it take for the load instruction to

execute.

4. Explain and contrast a hardwired control unit and a microprogrammed control unit.

Mention advantages and disadvantages of each.

5. Define the following:

• Register transfer notation (or language)

• Control signal

• Microoperation

• Control store

• Microprogram

• Opcode

• CPU

• Datapath

• Control unit

• ALU

• firmware

6. There may be questions similar to those on the Takehome quiz assigned on 3/14/12.

7. There will be one or two bonus questions taken from the History of Microprogramming

section of the Smotherman paper.