A Power Efficient Wide Band Trans-Impedance Amplifier in

advertisement

A Power Efficient Wide Band Trans-Impedance Amplifier in sub-micron CMOS

Integrated Circuit Technology

RABIN RAUT

Department of Electrical and Computer Engineering

Concordia University

Montreal, Canada

e-mail:rabinr@ece.concordia.ca

OMIDREZA GHASEMI

Department of Electrical and Computer Engineering

Concordia University

Montreal, Canada

e-mail:o_ghasem@ece.concordia.ca

It is easily recognized that for a practical TIA to conform to

the basic model (Fig.1(a)), one must ensure Z11ÆRin, Z21ÆRm,

Z22ÆRout , and Z12Æ0. For a terminated model of a TIA, shown

in figure 2, we can derive that:

Abstarct-This article proposes a simple trans-impedance

amplifier (TIA) using a given (i.e. 0.18 micron CMOS) VLSI

technological process. The TIA offers a very wide band-width of

operation with very small power consumption. Compared with

several TIA reported in the past, our TIA is more competitive

when band-width (more than 4 GHz) versus power consumption

(less than 3.5 mW) criterion is used as a metric for the merit of

the structure. Analytical optimization of the terminal

characteristics of the TIA are presented. Results of simulation

are reported , together with a comparison with TIA structures

reported in the recent past.

i1 →

iin →

is

II. TIA and two-port Z-parameters

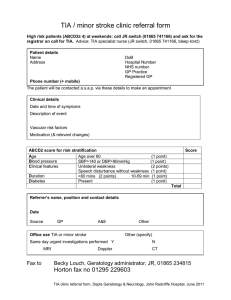

Figure 1(a) shows the basic equivalent circuit model of a

TIA [4]. Figure 1(b) shows the impedance (i.e., z-parameter)

model of a two port network. Any practical TIA system can be

easily related to the model of figure 1(b).

Zs

+

vi

z11

z22

← iout

ZL

z21iin

z12iout

+

vo

−

−

Zin

Z out

Figure 2: Z-parameter model of a TIA with terminations

Z in =

vi

z z

= z11 − 12 21

iin

z22 + z L

…(1)

Z out =

vo

z z

= z22 − 12 21

iout

z11 + z s

…(2)

… (3)

vo

z21

=

z

z

z

z

is (1 + 11 )(1 + 22 ) − 12 21

zs

zL

zs z L

The reverse trans-impedance parameter z12 provides a

feedback effect. If this can be eliminated, the two-port model

will conform closer with the basic CCVS model as in Figure

1(a). When this is not possible, we can try to adjust this

parameter to make the TIA offer an improved performance in

several respects. These considerations are discussed below.

ZT =

A. Input impedance matching

← iout

We shall assume that zero reflection condition ensures

impedance match at the input port. It is welknown that for high

frequency system, zero reflection is necessary for maximizing

power transfer at the input. This is possible by having Zin=zs.

This leads to (using eq.1)

Rout

Rm iin

z12 =

Figure 1(a): Equivalent circuit of a basic TIA

978-1-4244-2332-3/08/$25.00 © 2008 IEEE

z21i1

Figure 1(b) Z-parameters model of a TIA

Trans-impedance amplifier (TIA) networks implemented using

CMOS VLSI technology are being utilized as the front end in

various wide band communication systems [1] -[5]. The principal

motivations are realization of very high gain-bandwidth with low

input and output impedances. We have introduced an approach

using the two-port Z parameters for the realization of a TIA

[6].This provides guidance towards judicial choice of the circuit

parameters to arrive at an optimum design of the system.

Towards this, section 2 of this article we briefly review

several characteristics of a TIA based on the elements of its

associated Z-matrix parameters. In section 3, we introduce a new

TIA circuit, which performs very well when the gain-bandwidth

product per unit power consumption is considered as a figure of

merit of the system. We present some analytical and discuss the

possibilities for obtaining optimum performance characteristics.

Section 4 provides results of simulation followed by concluding

remarks in section5.

Rin

← i2

z22

z12i2

I. Introduction

iin →

z11

113

( z11 − z s )( z22 + z L )

z21

… (4)

Thus making Z11=zs facilitates achieving input matching

condition. This also renders z12 =0.

III. New TIA Circuit and Optimum Performance

characteristic

B. Output impedance matching

Figure 3 below presents the new TIA circuit. The operation of

the circuit is very straightforward. The gate-drain connected

CMOS input stages provide a very low input resistance to the

input signal (current) source. The current mirroring arrangement

transfers the signal current to the output. High output impedance

then provides a high signal voltage thereby contributing to a high

trans-impedance gain relative to the input signal (current) source.

For zero reflection at the output port, we should have Zout=zL.

This leads to (using eq.2)

z12 =

( z22 − RL )( z11 + z s ) … (5)

z21

As before, making Z22=RL will provide matching at the output,

together with z12=0. Alternatively, we can say that z12=0 opens

up the possibility of achieving input and output matching

indpendently.

C. Gain-bandwidth of the system

If we assume that the frequency response of the two port network

is determined only by the capacitive loading at the two terminals,

and that Cs and CL are these capacitors, we could write

1

1

= g L + sCL . If we assume that all the

= g s + sCs , and

zL

zs

two-port impedance parameters are resistive only. Then we have

(from eq.3)

ZT =

r21

{[1 + r11 ( g s + sCs )][1 + r22 ( g L + sCL )]

… (6)

−r12 r21 ( g s + sCs )( g L + sCL )}

Figure 3: New TIA circuit

If the two capacitors have widely different values, the one with

higher values will affect the band-width of the system. The

denominator of eq.6 can be expanded into a second degree

polynomial in s and is given by:

The terminal and transfer parameters of the TIA at low

frequency and GBW based on dominant pole approximation are

given by:

D( s) = −Cs CL (r11r22 − r12 r21 ) s 2 + (r11Cs + r11 g s r22CL

+r22CL + r11Cs r22 g L − r12 r21 g L Cs − r12 r21 g s CL ) s +

Rm =

1 + r22 g L − r12 r21 g s g L + r11 g s + r11r22 g s g L

The

dominant

pole

of

the

system

is

given

by:

1 + r22 g L − r12 r21 g s g L + r11 g s + r11r22 g s g L

ωp =

r11Cs + r11 g s r22CL + r22 CL + r11C s r22 g L − r12 r21 g L C s − r12 r21 g s CL

…(7)

r21

… (8)

(r11Cs + r11 g s r22C L + r22C L + r11C s r22 g L

ro (1 − Gm z )

ro zc2 ( g m + Gm ) + z (c1 + c2 ) + ro c1

…(11)

…

(12)

… (13)

Gm = g m 3 + g m 4

ro = rds 3 || rds 4

The above equation reveals a potential to make GBWÆ

infinity by arranging

r11Cs + r22 CL + r11r22 (Cs g L + CL g s )

r21 ( g L Cs + g s CL )

ro (1 + g m z )

1 + g m z + ro ( g m + Gm )

… (10)

g m = g m1 + g m 2

−r12 r21 g LC s − r12 r21 g s C L )

r12 =

Ro =

ro + z

1 + g m z + ro ( gm + Gm )

GBW =

The gain-bandwidth of the system can be expressed as

ZT(0).ωp. This is (from eqs. 6,7)

GBW =

Rin =

ro (1 − Gm z )

1 + gm z + ro ( g m + Gm )

c1 = cgs1 + cgs 2 + cgs 3 + cgs 4

c2 = cgd 3 + cgd 4

… (9)

In the above, we can clearly see that absence of the feedback

element ( zÆ infinity) will make Rin= 1/gm, Ro =ro , and Rm=

ro(Gm/gm). Clearly, Rout is a high value and is not desirable. On

the other hand, if zÆ zero, Rm becomes equal to (gm+Gm)-1,

However, one has to carefully evaluate the situation in a

practical system for physical realizability of this solution. One

can note that all the two-port parameters may not turn out to be

resistive only, as assumed in connectiion with eq.(6).

114

Clearly, by manipulating k , we can get desirable values for Rin

and Ro, while maitaining an expected high value for Rm.

which is a low value. Thus, it appears that a judicial choice of the

feedback element z need be made for optimum performance

characteristics of the TIA. It may be noted that the element z

presents a non-zero value for the reverse trans-impedance

parameter z12,, as discussed in section 2 of this article.

IV. Results

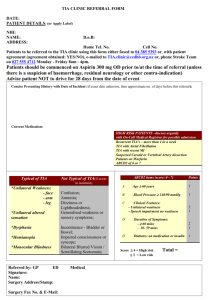

Simulation results for the TIAs using 0.18um CMOS

technology and the comparison with the other works [7]-[10] is

provided in the table 1(results in these references are

measurement results).The reader can see that the new TIA

proposed in this article has superior performance characteristics.

A novel idea that we wish to present in this article is to force z12

=0, while still keeping the element z to afford to flexible control

over the Rin and Ro parameters. This is done by introducing a

unidirectional (i.e., active) device in the feedback path as shown

in figure 4 below.

V. Conclusion

We have briefly reviwed the two-port impedance matrix

parameters of a TIA, and shown that important design guidelines

can be obtained from such analysis. We have introduced a new

TIA circuit that provides similar or better performance

characteristics for substantially lower power consumption

compared with several TIA circuits proposed in the recent past.

We intend to exploit the novel idea regarding the amplifier of

gain k (see Fig.4), and continue further studies.

Acknowledgement

The research was supported by a grant awarded to Dr. R. Raut

by the Natural Science and Research Council (NSERC) of

Canada, and a grant by Concordia University, Montreal, Canada.

Figure 4: New TIA circuit with z12 =0.

With the amplifier of voltage gain k, the Rin, Ro , and Rm

expressions become respectively:

Rm =

ro ( k − Gm z )

g m ( ro + z)

,

Rin =

1

gm

,

Ro ≅ z …(14)

Table I

Simulation results and comparison with other works

Technology

(CMOS)

This work,

Fig[4]

This work,

Fig[3]

Design[7]

0.18um

TIA

Gain

(dBOhm)

54.3

-3dB

BW

(GHz)

Power

(mW)

Input referred

Noise(pA/ Hz )

VDD

(v)

PD

Cap

(fF)

GBWP/Power

4.92

3.48

6.89

1.8

50

733.4

0.18um

53.4

5.35

3.48

8.15

1.8

50

719.2

0.18um

9.2

137.5

17.0

Design[8]

Design[9]

0.18um

0.18um

54

61

62.3

7.2

9.0

70.2

108.0

500

250

150

33.5

115.1

108.6

Design[10]

0.18um

51

30.5

60.1

8.2

34.3

2.5

1.8

1.8

1.8

50

180.1

115

[5] M. Ingels, G. Van Der Plas, J. Crols and M. Steyaert,

"A CMOS 18-THz 240-Mb/s transimpedance amplifier and

155-Mb/s LED driver for low-cost optical fiber links”,

IEEE J. Solid-State Circuits, vol. 29, 1994, pp.1552-1558

[6] R. Raut, "Some Insight into the Implementation of a TransImpedance Amplifier in CMOS Technology Using Two-Port

Network Parameters", WSEAS Transactions on Circuits and

Systems, Issue 7, Vol.5, July 2006 (ISSN 1109-2734

http://www.wseas.org), pp.1067-1074.

[7] B. Analui and A. Hajimiri “Bandwidth enhancement for

transimpedance amplifier” IEEE

J. of Solid-state

Circuits,vol.39,pp. 2334-2340,Dec 2003

[8] C.-H. Wu,C.-H.Lee,W.-S. Chen,and S.-I. Liu,”CMOS

wideband amplifiers using multiple inductive-series peaking

technique” IEEE J. of Solid-State Circuits,vol 40,pp.548-552

,Feb2005

[9]A.K. Peterson,K.Kiziloglu,T.Yoon,F. Williams,Jr., M.R.

Sander,”Front-end CMOS chipset for 10 Gb/s communication”

in IEEE RFIC Sym. Dig,June 2003

[10] Jun-De Jin and Shawn S.H.Hsu “ 40-Gb/s Transimpedance

Amplifier in 0.18-um CMOS Technology” European solid state

circuits conference,2006 pp.520-523

References

[1] N. Haralabidis, S. Katsafouros, and G. Halkias, “A 1 GHz

CMOS transimpedance amplifier for chip- to- chip optical

interconnects”, Proc. IEEE Intenational Symposium in Circuits

and Systems, Geneva, Switzerland, vol.5, May 2000, pp.421424.

[2] T. Yoon and B. Jalali, “1 Gbit/s fiber channel CMOS

transimpedance amplifier”, Electronics letters, vol.33, no.7,

March 1997 pp.588-589.

[3] C. Toumazou and S.M. Park, "Wideband low noise CMOS

transimpedance amplifier for gigahertz operation”, Electronics

Letters, vol.32, no.13, Jume 1996, pp.1194-1196.

[4] S.M.Park and H.J.Yoo, “1.25-Gb/s regulated cascode

CMOS transimpedance amplifier for gigabit Ethernet

applications” , IEEE J. of Solid State Circuits, vol.39, no.1,

January 2004, pp.112-121.

116