Scaling of SiGe Heterojunction Bipolar Transistors

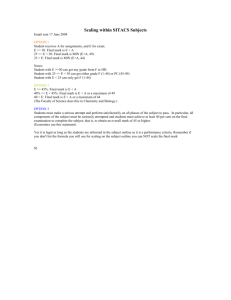

advertisement