Lecture 14 - Linear Equivalent Circuits

advertisement

6.012 - Electronic Devices and Circuits

Lecture 14 - Linear Equivalent Circuits - Outline

• Announcements

Handout - Lecture Outline and Summary

• Review - Adding refinements to large signal models

Charge stores: depletion regions, excess carriers, gate charge

Active-length modulation: the Early effect

Extrinsic parasitics: Lead resistances, capacitances, and inductances

• Small signal models

What are they good for?

• Linear equivalent circuits

pn diodes:

linearizing the exponential diode

incorporating the charge stores

BJTs:

linearizing the Ebers-Moll model

incorporating the charge stores

adding the Early effect and possible parasitics

MOSFETs: linearizing the Gradual-Channel model

incorporating the charge stores

adding the Early effect and possible parasitics

Clif Fonstad, 10/03

Lecture 14 - Slide 1

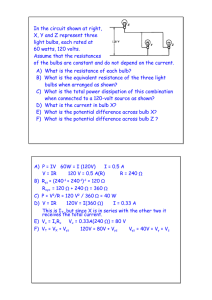

Circuit symbols:

C

BJT:

C

B

B

E

B

E

C

E

npn

pnp as frequently

pnp

oriented in circuits

MOSFET:

D

G

D

B G

B

S

Linear schematics

S

Digital schematics

n-channel

Clif Fonstad, 10/03

S

G

S

B G

D

Linear schematics

B

D

Digital schematics

p-channel (usual circuit orientation)

Lecture 14 - Slide 2

Output

Characteristics

BJT:

Saturation

iC

Forward Active Region

iC ≈ bF iB

npn

iC ≈ bF(1 + lvCE)iB

0.2 V

MOSFET:

Linear

iD or

Triode

n-channel

iD ≈ K[vGS - VT(vBS) - vDS/2]vDS

Cutoff

Saturation (FAR)

iD ≈ K [vGS - V T(vBS )]2/2a

2

iD ≈ K[vGS - VT(vBS)] [1 + lvDS]/2

Cutoff

Clif Fonstad, 10/03

vCE

vDS

Lecture 14 - Slide 3

• Creating a linear equivalent circuit, LEC:

Suppose we have a device with three

qX(vXZ , vXY)

qY(vYZ, vYX)

terminals, X, Y, and Z, and that

we have expressions for the currents into terminals X and Y in

X

Y

terms of the voltages vXZ and vYZ:

iY(vXZ , vYZ)

iX (v XZ ,vYZ ) and iY (v XZ ,vYZ )

iX(vXZ , vYZ)

Suppose we also have expressions for

the charge stores associated with

Z

terminals X†and Y: qX (v XZ ,vYZ ) and qY (v XZ ,vYZ )

We begin with the static model for the terminal characteristics, and

linearize them about an bias point, Q, defined as a specific set of

vXZ and vYZ that we write, using†our notation, as VXZ and VYZ

For example, for the current into terminal X we have:

∂i

∂i

iX (v XZ ,vYZ ) = iX (VXZ ,VYZ ) + X (v XZ - VXZ ) + X (vYZ - VYZ ) + higher order terms

∂v XZ Q

∂vYZ Q

For sufficiently small (vXZ-VXZ) and (vYZ-VYZ), we have:

∂i

∂i

iX (v XZ ,vYZ ) ª iX (VXZ ,VYZ ) + X (v XZ - VXZ ) + X (vYZ - VYZ )

∂v XZ Q

∂vYZ Q

†

Clif Fonstad, 10/03

continued on the next page

Lecture 14 - Slide 4

• Creating a linear equivalent circuit, LEC, cont.:

Using our notation, we recognize that:

I X ≡ iX (VXZ ,VYZ ), ix ≡ [iX - IX ], v xz ≡ [v XZ - VXZ ], v yz ≡ [vYZ - VYZ ]

We identify the partial derivatives as conductances, and name them as:

∂iX

∂iX

≡ gi

≡ gr

†

∂v XZ Q

∂vYZ Q

Applying these to our earlier result we have, first:

∂i

∂i

iX (v XZ ,vYZ ) ª IX + X v xz + X v yz

∂v XZ Q

∂vYZ Q

†

and finally:

ix (v xz ,v yz ) ª giv xz + grv yz

Doing the same for iY, we arrive†at

where:

Clif Fonstad, 10/03

iy (v xz ,v yz ) ª g f v xz + gov yz

†

∂i

∂i

gf ≡ Y

go ≡ Y

∂v XZ Q

∂vYZ

†

Q

continued on the next page

†

Lecture 14 - Slide 5

• Creating a linear equivalent circuit, LEC, cont.:

A circuit showing relating the incremental currents and voltages is

shown below:

x

y

+

v xz

z

gi

gr v yz

gfv xz

go v yz

z

Next, to handle high frequency signals, we linearize the charge stores'

dependencies on voltage. Their LECs, which are linear capacitors:

Ê ∂q ˆ

∂qX

∂qY

∂qX

≡ Cxz

≡ Cyz

≡ Cxy ÁÁ = Y ˜˜

∂v XZ Q

∂vYZ Q

∂v XY Q

Ë ∂vYX Q ¯

Adding these to the model gives us:

x

+

v xz gi

z

Clif Fonstad, 10/03

Cxy

†

gr v yz

Cxz

Cyz

y

gfv xz

go

v yz

z

Lecture 14 - Slide 6

• Linear equivalent circuit (LEC) for the p-n junction diode:

We begin with the static model for the terminal

characteristics:

qv

kT

iD (v AB ) = IBS [e

AB

-1]

iD

L!inearizing iD about VAB, which we will

denote by Q (for quiescent bias point):

∂i

†

iD (v AB ) ª iD (VAB ) + D [v AB - VAB ]

∂v AB Q

A

+

vAB

IBS

–

B

We define the equivalent incremental conductance

of the diode,gd, as:

∂i

q

q ID

gd ≡ D =

IBS e qV / kT ª

∂v AB Q kT

kT

†

AB

a

and we use our notation to write:

ID = iD (VAB ),

ending up with

id = [iD - ID ],

†

v ab = [v AB - VAB ]

gd

+

vab

id = gd v ab

†

The !corresponding

LEC is shown at right:

Clif Fonstad, 10/03

id

qI

gd ª D

kT

b

†

–

Lecture 14 - Slide 7

†

• LEC for the p-n junction diode, cont.:

A

At high frequencies we must include the charge store , qAB,

and linearize its two components:

qAB = qDP + qQNR, p-side

Cd = Cdp + Cdf

qAB

IBS

Depletion layer charge store, qDP, and its

linear equivalent capacitance, Cdp:

B

†

qDP (v AB ) = -AqN Ap x p (v AB ) ª -A 2qeSi N Ap (f b - v AB )

∂qDP

∂v AB

Cdp (VAB ) ≡

qeSi N Ap

2 (f b - VAB )

=A

Q

a

Diffusion charge store, qQNR,p-side, and its linear

equivalent capacitance, Cdf:

†

qQNR, p-side (v AB ) =

Cdf (VAB ) ≡

iD [ w p - x p ]

†

Cd

2

b

2De

∂qQNR , p-side

∂v AB

2

=

Q

q ID [ w p - x p ]

= gd t d

kT

2De

(Note: All of this is for an n+-p diode)

Clif Fonstad, 10/03

gd

with t d ≡

[w

p

- xp]

2

2De

Lecture 14 - Slide 8

• Linear equivalent circuit for the BJT (static):

In the forward active region, our static model says:

iB (v BE ,vCE ) = IBS [e qv BE

kT

-1]

iC (v BE ,vCE ) = b o [1+ lvCE ] iB (v BE ,vCE ) = b o IBS [e qv BE

kT

-1][1+ lvCE ]

We begin by l!inearizing iC about Q:

† ,v ) = ∂iC v + ∂iC v = g v + g v

ic (v

be ce

be

ce

m be

o ce

∂v BE Q

∂vCE Q

We introduced the transconductance, gm, and the output conductance,

go, defined as:

∂iC

∂iC

g†

≡

g

≡

m

o

∂v BE Q

∂vCE Q

Evaluating these partial derivatives using our expression for iC, we find:

gm =

q

b o IBS e qV†BE

kT

go = b o IBS [e qVBE

Clif Fonstad, 10/03

kT

kT

[1+ lVCE ]

+ 1] l ª l IC

(Continued on next foil.)

ª

q IC

kT

Ê

IC ˆ

Á or ª

˜

VA ¯

Ë

Lecture 14 - Slide 9

• LEC for the BJT (static), cont.:

Turning next to iB, we note it only depens on vBE so we have:

∂iB

ib (v be ) =

v be = gp v be

∂v BE Q

The input conductance, gp, is defined as:

∂i

gp ≡ B

† ∂v BE

Q

To evaluate gp we do not use our expression for iB, but instead use

iB = iC/bo:

∂i

1 ∂iB

g

q IC

gp ≡ B =

= m =

∂v BE Q b o ∂v BE Q † b o

b o kT

(Notice that we do

not define gp as qIB/kT)

Representing this as a circuit we have:

b

gp

e

Clif Fonstad, 10/03

+†

vp

-

(Notice that vbe has been renamed vp)

c

gmv p

go

e

Lecture 14 - Slide 10

• Linear equivalent circuit for the BJT (dynamic):

To complete the model we next linearize and add the charge stores

associated with the two junctions.

qBC

C

The base-collector junction is reverse biased

so the charge associated with it, qBC, is the

depletion region charge. The correspond

-ing capacitance is labeled Cm.

bFiB’

iB’

B

IBS

The base-emitter junction is forward biased

as has the excess charge injected into the

E

qBE

base as well as the base-emitter depletion

charge store associated with it. The linear equivalent capacitance

is labeled Cp. The part of Cp due to the excess charge turns out to

be q|IC|wB2/2DekT, which can also be written gmtb with tb = wB2/2De

Summarizing: Cp = gmtb + B-E depletion cap., Cm : B-C depletion cap.

Adding these

C's to our

model:

b

gp

e

Clif Fonstad, 10/03

Cm

+

vp

-

Cp

c

gmv p

go

e

Lecture 14 - Slide 11

• Linear equivalent circuit for the MOSFET (static):

In saturation, our static model is:

(We've said a = 1)

iG (vGS ,v DS ,v BS ) = 0

iB (vGS ,v DS ,v BS ) ª 0

2

K

iD (vGS ,v DS ,v BS ) = [vGS - VT (v BS )] [1+ lv DS ]

2

W

1

*

with K ≡ me Cox

and VT (v BS ) ≡ VFB - 2f p-Si + * 2eSiqN A 2f p-Si - v BS

L

Cox

{

[

]}

1/ 2

Note that because iG and iB are zero they are already linear, and

we can focus on iD. L!inearizing iD about Q we have:

†

∂iD

∂i

∂i

id (v gs,v ds,v bs ) =

v gs + D v ds + D v bs

∂vGS Q

∂v DS Q

∂v bS Q

= gm v gs + gov ds + gmb v bs

We have introduced the transconductance, gm, output conductance,

go, and !substrate transconductance, gmb:

†

∂i

gm ≡ D

∂vGS

go ≡

Q

∂iD

∂v DS

gmb ≡

Q

(Continued on next foil.)

Clif Fonstad, 10/03

†

∂iD

∂v BS

Q

Lecture 14 - Slide 12

• LEC for the MOSFET (static), cont.:

Evaluating the conductances using our expression for iD, we find:

∂i

gm ≡ D = K [VGS - VT (VBS )] [1+ lVDS ] ª 2K ID

∂vGS Q

∂i

go ≡ D

∂v DS

gmb ≡

Q

∂iD

∂v BS

= -K [VGS - VT (VBS )] [1+ lVDS ]

Q

with

Representing

g

this as a

+

circuit

v gs

we have: †

s-

Clif Fonstad, 10/03

Ê

ID ˆ

Á or ª

˜

V

Ë

A¯

K

2

= [VGS - VT (VBS )] l ª l ID

2

v bs

b+

h≡-

∂VT

∂v BS

∂VT

∂v BS

=

Q

= h gm = h 2K ID

Q

1

*

Cox

eSiqN A

qf p - VBS

d

gmv gs

gmb v bs

go

s

Lecture 14 - Slide 13

• Linear equivalent circuit for the MOSFET (dynamic):

To complete the model we next linearize and add the charge stores

associated with each pair of terminals.

D

In saturation qG is a function

only of vGS and vGB, so our

model only accounts for Cgs

and Cgb. Cgd is a parasitic

element.

qDB

qG

iD

G

B

qSB

S

We have: Cgs = (2/3) WL Cox*

Cgd: sum of G-D fringing and overlap capacitances (all parasitics)

Csb, Cgb, Cdb: depletion capacitances

Adding these C's

to our model:

Clif Fonstad, 10/03

Cgd

g

+

v gs

s -v bs

b+

d

gmv gs

Cgs

gmb v bs

go

s

Csb

Cgb

Cdb

Lecture 14

Slide 14

6.012 - Electronic Devices and Circuits

Lecture 14 - Linear Equivalent Circuits - Summary

• Analog circuit design; small signal models

Linear amplification and processing of signals

Digital circuits are ultimately analog

• Linear equivalent circuits: it all depends on the bias point

a

pn diodes:

gd

Cd

BJTs: (in FAR) b

b

+

vp

-

gp

e

MOSFETs:

g

Clif

Fonstad

10/03

+

v gs

s -v bs

b+

Cm

Cp

gmv p

go

gm = q|IC|/kT

c gp = gm/bF

go = |IC/VA| [or l |IC|]

Cp = gmtb + Cdp,be(VBE)

Cm = Cdp,bc(VBC)

e

Cgd (in saturation)

gmv gs

Cgs

Csb

gd = q|ID|/kT

Cd = gdtd + Cdp(VAB)

Cgb

gmb v bs

Cdb

go

gm = K(VGS - VT) = (2K|ID|)1/2

d gmb = hgm

[h = {eSiqNA/2(|2fp| - VBS)}1/2/Cox*]

go = |ID/VA| [or l |ID|]

*

s Cgs = (2/3) WL Cox

Cgd: G-D fringing and overlap

capacitance, all parasitic

Csb, Cgb, Cdb: depletion capacitances

Lecture 14 - Slide 15