Lecture 25 - Beyond Si; Beyond 6.012 - Outline Announcements

advertisement

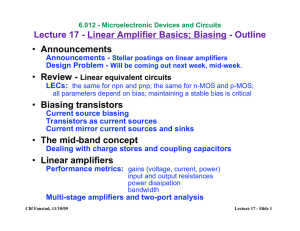

6.012 - Microelectronic Devices and Circuits

Lecture 25 - Beyond Si; Beyond 6.012 - Outline

• Announcements

HKN Evaluation - Do before final so you're still in a good mood.

Final - Tuesday, Dec 15, 9:00 am to Noon

Covering all the course; closed book; 4 problems

• Sub-threshold Circuit - What, Why, How

Applications: medical implants, remote sensors, portable devices

Digital design: choosing VDD for minimum energy per operation

• Devices we have known - Where are they now:

MOSFETs: 5 nm Si, III-V high electron mobility transistors

BJTs: InP based double heterojunction bipolar transistors

LEDs: white lighting; laser diodes

Solar cells: multi-junction, multi-material concentrator cells

• Life after 6.012

Is it possible? ("Where does one head after taking the header?")

Clif Fonstad, 12/10/09

Lecture 25 - Slide 1

Sub-threshold Circuit Design: The need for low energy

Emerging applications require

ultra-low energy:

µ-sensors, medical devices

Images removed due to copyright restrictions:

cartoons and figures illustrating microsensors, medical devices,

ambient intelligence, and portable devices.

Ambient intelligence, portable

devices

Sub-threshold operation:

Slow, lower power, minimum

energy operation becomes

possible

Sub-VT benefits:

Power

Energy

Concerns:

Increased sensitivity to noise

and to variations in VT and T.

Clif Fonstad, 12/10/09

Research at M.I.T. under Prof. Anantha Chandrakasan.

Lecture 25 - Slide 2

Sub-threshold Circuit Design: Digital Inverters, cont.

VDD = 0.3V

ID = IS,s"t e

ID

in

vGS "VT

nVt

out

with

v

#

" DS &

%1" e Vt (

%

(

$

'

IS,s"t = K Vt2 (n "1)

!

Clif Fonstad, 12/10/09

Work of Benton H. Calhoun at M.I.T. under

Prof. Anantha Chandrakasan's supervision.

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

Lecture 25 - Slide 3

Sub-threshold Circuit Design: Digital Inverters

Operation of standard CMOS gate with VDD < VT

CMOS Inverter Voltage Transfer Curves |VT| = 0.5 V

Clif Fonstad, 12/10/09

Work of Benton H. Calhoun at M.I.T. under

Prof. Anantha Chandrakasan's supervision.

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

Lecture 25 - Slide 4

Sub-threshold Circuit Design: CMOS Inverters, cont.

In low-power applications an important metric the energy per operation,

Epop. There is an optimum supply voltage that minimizes Epop.

Operating in strong inversion, Epop = CLVDD2 , and reducing VDD clearly

reduces Epop. As VDD approaches VT, however, the contribution of subthreshold leakage becomes important, especially because the gate

delay, τGD (time per operation) increases as charging current decreases.

In general:

" GD = 2CLVDD ID,sat

Only ID,sat is different depending on the region of operation.

ID,sat = K (VDD " VT ) 2

In strong inversion:

2

!

Sub-threshold:

ID,sat = K Vt2 (n "1)e(VDD "VT ) nVt

Just above threshold:

!

[

]

ID,sat = K Vt2 (n "1) + (VDD " VT ) 2

!

2

Thanks to Naveen Verma for discussions on sub-threshold circuits.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 5

Sub-threshold Circuit Design: CMOS Inverters, cont.

The energy per operation, Epop, including energy dissipated by the subthreshold leakage current, Ileakage x τGD x # of idle gates is:

2

2

E pop = CLVDD

+ A IleakageVDD " GD = CLVDD

[1+ 2 A Ileakage ID,sat ]

A is the average number of idle gates per active gate, and the leakage

current is:

2

"VT nVt

Ileakage = KVt ( n "1)e

! Evaluating E

pop

E pop

in each region of operation we find:

)C V 2 [1 + 2 Ae"VDD nVt ]

Sub-threshold

L DD

+!

+

"VDD nVt

#

&

+

2

Ae

2

= *CL VDD

%1 +

( Just above threshold

2

2

%$ 1+ (VDD " VT ) 2Vt ( n "1) ('

+

+

+

2

In strong inversion

, CL VDD

These expressions are plotted on the next slide.

Thanks to Naveen Verma for discussions on sub-threshold circuits.

!

Clif Fonstad, 12/10/09

Lecture 25 - Slide 6

Sub-threshold Circuit Design: Minimizing Energy per

Operation in CMOS Logic

The energy per operation, Epop, assuming |VT| = 0.4 V, n = 2, and A = 50

and 100 is plotted below. Note the minimum for VDD a bit below VT**:

** The results are quite sensitive in detail to the values of n, A, and VT.

Thanks to Naveen Verma for sub-threshold circuit discussions.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 7

Sub-threshold Circuit Design: Minimizing Energy per

Operation, cont.

Reducing VDD reduces the charging/discharging currents rapidly and

increases the cycle time significantly, so Emin operation is low speed.

For many remote and monitoring sensor application this is just fine.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 8

Sub-threshold Circuit Design: CMOS Inverters, cont.

11 stages

330kHz

300mV

•

29kHz

200mV

•

Simple ring oscillator shows

functionality in deep sub VT

Delay increases exponentially in

sub VT

3kHz

100mV

Work of Benton H. Calhoun at M.I.T. under

Prof. Anantha Chandrakasan's supervision.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 9

Courtesy of Benton Calhoun and Anantha Chandrakasan. Used with permission.

Sub-threshold Circuit Design: Linear circuits

Conventional stages and designs can be operated in subthreshold, just as was done with CMOS gates. They are

slow, but if power is a concern and high speed isn't (i.e,

under 10 MHz is OK), they are worth considering.

V+

New types of MOS circuits are also

possible: Translinear circuits.*

Consider first, for example, the

sub-threshold current mirror on

the right:

VREF

!

I2

I1

" VT = "nVt ln

W1IS,s"t

I2 = W 2 IS,s"t e

!

I1

"(V REF "VT ) nVt

W

= 2 I1

W1

Note the exp to ln and ln to exp

conversions.

Q1

Q2

+

V REF

-

V-

* Translinear circuits were invented by Barrie Gilbert of Analog Devcies working with BJTs

(IEEE JSSC, Vol SC-3, No. 4, Dec. 1968, pp. 353-373).

Clif Fonstad, 12/10/09

Lecture 25 - Slide 11

Sub-threshold Circuit Design: Translinear circuits, cont.

Now consider using this log function and its inversion to do

multiplication. Consider the following circuit:

V+

To begin note that:

vGS1 + vGS 2 = vGS 3 + vGS 4

and:

Ii

vGSi " VT = "nVt ln

W i IS,s"t

I2

Q1

V GS1

V GS3

-

-

Q2

+

I1

Q3

+

+

!

V GS2

I3

-

V-

I4

Isolating vGS4:

vGS 4 = vGS1 + vGS 2 " vGS 3

and substituting , we find:

!

Q4

+

V GS4

-

I4 =

!

I1 " I2 W 3 " W 4

"

I3 W1 " W 2

Circuits like this can be used

to do analog multiplication.

!the same width:

If the FETs are all

I4 =

I1 " I2

I3

* After 6.376 notes via Naveen Verma.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 12

High frequency metric, fT: unity gain point of the short-

circuit current gain, βsc(jω)

log |" sc |

βF

Low frequency value:

= infinity for MOSFET

= βF for BJT

Unity gain point, ωt

!z

log !

!t

) g C = 3µ (V $ V ) 2L2 = 3s 2L

Ch

GS

T

Ch

+ m gs

*

*

" t # * gm Cgs = W ssat Cox

W LCox

= ssat L

+ g C + C & lim

2

µ)

Ic '( # 2Dmin,B w B

, m ( %

Clif Fonstad, 12/10/09

!

MOSFET, no vel. sat.+

1

MOSFET, w. vel. sat.. =

0 tr

+

BJT, large I C

/

Lecture 25 - Slide 14

Bipolar Junction Transistors: basic operation and modeling…

… how the base-emitter voltage, vBE, controls the collector current, iC

vCE

- iE

n

NDE

E

-

vBE

p

NAB

+B

-wE

n

NDC

wB

0

Electron

flux

C

−

iC

Hole flux

+

Clif Fonstad, 5/15/08

x

wB + wC

vBE

Clif Fonstad, 12/10/09

iC

+

E

C

iB

−

iE

+

B

iB

Why HBTs?: high speed,

current, and efficiency.

Lecture 25 - Slide 20

Lecture 26 - Slide 9

Heterojunction BipolarTransistors: higher mobility materials,

graded base to create drift field, different Eg to tailor injection

1.5

Graded base

1.0

GaAs0.5Sb0.5 - In0.2 Ga0.8As0.7Sb0.3

Energy (eV)

0.5

-1.0

InGaAs contact InP emitter

InP collector

-0.5

-1.0

-1.5

0

0.05

0.10

0.15

0.20

Position from surface (µm)

Figure by MIT OpenCourseWare.

Work of Prof. Milton Feng and students at University of Illinois

Source: Compound Semiconductor, March 2008

Clif Fonstad, 5/15/08

Lecture 26 - Slide 21

Heterojunction BipolarTransistors, cont: fT = 685 GHz @ R.T.

40

Gain (dB)

30

20

fT

fmax

10

0

1

10

100

1000

Frequency (GHz)

Figure by MIT OpenCourseWare.

Notice that performance above 50-100 GHz is extrapolated using

the theoretical frequency dependence to get fT and fmax values.

This is accepted practice because the instrumentation needed

does not exist.

Source: Compound Semiconductor, March 2008

Clif Fonstad, 5/15/08

Lecture 26 - Slide 22

Mixing technologies and materials on a Si platform: other routes

to keeping performance on the Si roadmap; optoelectronic integration

Coaxial coupling:

Optical waveguide

Laser

research at MIT

Si CMOS IC substrate

p contact

Evanescent vertical

coupling:

work at UCSB and Intel

III-V Region

n contact

H+

H+

III-V Mesa

n- InP

Optical mode

Buried oxide

SOI Region

Si Substrate

Not to scale

Figure by MIT OpenCourseWare.

Grating coupling:

specific to VCSELs

Source: Dirk Taillaert, INTEC,

University of Gent

Clif Fonstad, 12/10/09

Lecture 25 - Slide 28

Courtesy of Dirk Taillaert. Used with permission.

Solar Cells: Illumination shifts diode curve downward

Electrical power is produced in 4th quadrant

The total current:

iD (v AB , M) = iD (v AB ,0) + iD (0, M)

= IS (e qv AB

kT

"1) " AqM (1" a)

Illumination shifts the ideal diode curve down vertically:

iD

!

iD(vAB,0)

iD(0,M) = -AqM(1-a)

Light detection

in this quadrant

Clif Fonstad, 12/10/09

iD(vAB,M)

vAB

Power conversion

in this quadrant

Lecture 25 - Slide 29

Solar Cells: A single band-gap diode misses much of the

solar energy spectrum

Photons with energy, hν, less

than Eg are not absorbed, and

that part of the spectrum is

lost.

Photons with energy, hν, more

than Eg are absorbed but all

their energy above Eg is lost to

the crystal lattice as the

electrons and holes "relax" to

the bottom of their the lowest

energy states. This limits Si

solar cell efficiency to ~ 20%.

The solution: Stack (layer)

several solar cells with

differing band-gaps so each

optimally absorbs the

optimum range of photons.

Clif Fonstad, 12/10/09

Electron

energy

Conducting

states

Eg

Eg,Si ≈ 1.1 eV

Bonding

states

Density of electron

energy states

Lecture 25 - Slide 30

Solar Cells: Multi-junction solar cells InGaP/GaAs/Ge

p-InGaP

n-InGaP

p-GaAs

n-GaAs

GaP

p-Ge

InGaP

n-Ge

GaAs

InP

Multi-junction cells

exceed 50% conversion efficiency.

They are costly so are

used in sun tracking

concentrator systems.

Clif Fonstad, 12/10/09

Ge

Lecture 25 - Slide 31

Solar Cells: Multi-junction solar cells InGaP/GaAs/Ge, cont.

2.5

UV Visible

Spectral lrradiance (W/m2/nm)

2

Infrared

Sunlight at top of the atmosphere

1.5

5250o C Blackbody spectrum

1

H2O

Radiation at sea level

0.5

H2O

Absorption bands

O2

H2O

O3

0

250

CO2

H2O

H2O

500

750

1000

1250

1500

1750

2000

2250

2500

Wavelength (nm)

InGaP

GaAs

Ge

Lost

Figure by MIT OpenCourseWare.

Clif Fonstad, 12/10/09

Lecture 25 - Slide 32

Life after 6.012 - "I've taken the header, so…where can I head?"

6.012

Physics

Digital ckts

Devices

Analog ckts

Fabrication

• Physics

6.719:

6.728:

6.729:

6.730:

6.732:

6.763:

Nano electronics (see also 6.701; similar but "U")

Applied quantum and statistical physics

Molecular electronics

Physics for solid-state applications

Physics of solids

Applied superconductivity

H

H

H

H

H

H

G(S)

G(F)

G(S)

G(S)

G(F)

G(F*)

H

H

H

H

H

G(F)

G(F*)

G(S*)

G(S)

G(S*)

• Devices

6.720J:

6.731:

6.772:

6.777J:

6.789:

Clif Fonstad, 12/10/09

Integrated microelectronic devices

Semiconductor optoelectronics

Compound semiconductor devices

Design and fabrication of MEMS

Organic optoelectronics

* alternate years

Lecture 25 - Slide 33

Life after 6.012 - cont.

• Processing

6.152J: Microelectronics processing technology

U(F,S)

--------------------

6.774:

6.778J:

6.780J:

6.781J:

Physics of fabrication: front-end proc.

Materials and processes for MEMS

Control of manufacturing processes

Sub-micron and nanometer technology

H

H

H

H

G(F*)

G(S)

G(S*)

G(S)

Solid-state circuits

Feedback systems

Advanced circuit techniques

Power electronics

Low power analog VLSI

H

H

H

G(F)

G(S)

G(F*)

G(S)

G(F)

6.775: Design of analog MOS LSI

6.776: High speed communications circuits

H

H

G(S)

G(S*)

H

H

G(F)

G(S)

• Analog circuits

6.301:

6.302:

6.331:

6.334:

6.376:

--------------------

• Digital circuits

--------------------

6.374: Analysis and design of digital ICs

6.375: Complex Digital Systems Design

Clif Fonstad, 12/10/09

* alternate years

Lecture 25 - Slide 34

6.012 - Microelectronic Devices and Circuits

Lecture 25 - Beyond Si; Beyond 6.012 - Summary

• The current state-of-the-art

Very small and blazingly fast

(and getting smaller and going faster every day)

Lmin = 1.0 µm

→ 0.75 µm

→ 0.5 µm

→ 0.35 µm

→ 0.25 µm

→ 0.18 µm

→ 0.13 µm

→ 90 nm

→

The world of semiconductor

electronics encompasses far

more than Si µP's and RAM,

but it all benefits from the

technology advances these

major Si applications fund.

We're in this region now.

45 nm

We're in this region now.

→ 32 nm We're in this region now.

65 nm

→

→

• Life after 6.012

Yes, there is life after 6.012.

→ Physics

→ Devices

→ Processing

→ Analog circuits

→ Digital circuits

Clif Fonstad, 12/10/09

22nm

→

15 nm

→

11 nm

→

8 nm

→

5 nm

Lecture 25 - Slide 35

MIT OpenCourseWare

http://ocw.mit.edu

6.012 Microelectronic Devices and Circuits

Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.