1. logic gates

advertisement

TABLE OF CONTENTS

Acknowledgments

Introduction

Objectives

The Digital Kit

1. Prototyping board

2. Power Supply

3. LEDs

4. Switches

5. 7-Segment Display

6. Digital Clocks

Laboratory Exercises

0. Discrete Gates

1. Logic Gates

a. Basic Logic Gates

b. Logic Gates Applications

2. Digital Meets Analog Lab Exercise

3. Full-Adder & Full-Subtractor

a. Construction of Full-Adder

b. Construction of Full-Subtractor

4. Decoders

a. Basic Decoders

b. Decoder Applications

5. Multiplexer

6. PLD

7. Sequential Circuit

8. Counters

9. Shift Registers

10. Mini-Projects

a. Thunderbird Taillights

b. Lamp Ping-Pong

c. Other Proposal

11. IC Symbols & Pin-outs

ACKNOWLEDGMENTS

The laboratory exercises contained within this document have evolved from a set of

exercises that have been taken from the Digital Design System Laboratory Manual 2005.

Helpful comments have been made by Mr. Jose Claro Monje and Dr. Rosula Reyes who have

used the experiments in their teaching of Digital Logic Design and Switching Theory.

INTRODUCTION

The goal of this experiment manual is to introduce the fundamentals of digital electronic

components (basic gates, decoders, multiplexers, flip-flops, counters, shift registers) in a

manner suitable for Engineering students. Breadboard prototyping will be performed to

actualize digital circuits. Hopefully, this manual can serve as a systematic guide to “handson” experience with digital electronic concepts and devices taught in the lecture course.

OBJECTIVES

The course will provide the student with a firm foundation of the principles of digital design

by building a working knowledge of digital electronics and its applications.

By the end of the semester, the student shall have acquired the basic skill in using the digital

design kit;

● Use of prototyping board.

● Use of basic gates, decoders and multiplexers.

● Use of PLDs

● Use of flip-flops, counters and shift registers.

● Use of logic probe.

The Digital Kit

1. Prototyping/ B readboard

The breadboard is used to create a circuit without the need for soldering circuit

elements together. The upper and lower halves of the breadboard contain 63 vertical rows

of 5 interconnected contacts. There are also 4 long horizontal rows of connectors (10

groups of 5 contacts each) along the upper and lower edges. These long rows of

connectors are referred to as power bus strips because they will be connected to the

power supplies to provide power connections over the entirety of the breadboard. This

breadboard socket is designed to accept integrated circuits, most common wire terminal

components, and wire interconnections.

2. POWER SUPPLY

This segme nt of the board can prov i d e a voltage of +5 V and a max i m u m current of 1

A m p e re. The 220 mains voltage is stepped do w n, rectif ie d, filtered and regulated by a +12 V

regulat o r that suppl ies the po we r t o the short circuit protect i o n branc h of this segme nt. The

+12 V is further regulated to prov i d e the +5 V that is availab le for use in whatev er circu i t that

is to be tested. Po wer is turned on by first mo v i n g the swit c h to the 'O N' positi o n and pressing

the 'RES E T / PUS H O N' button. This button is used for turni n g on the board after a short

circ ui t has happened.

3. LEDs

There are eight LE D s availab le. These are activated by suppl y i n g a T T L high to each of the

correspo n d i n g term i n a l bloc k pins.

4. SWITCHES

There are eight available switc hes in the kit, six (Sw5 to Sw0) of wh ic h are ordinar y toggle

switc hes whi le the two others are debou nc e d switc hes (Sw6 & Sw7). The com m o n node of

the single pole doub le thro w switc hes is connected to the wire holder wh i le the other two

nodes to groun d and Vc c.

5. 7-SEGMENT DISPLAY

The two seven segment displays are driven by 7447 B C D- to-seven- segme nt display

decoder/dri v ers. The said driver has 4 inputs correspo n d i n g to the binary code of the desired

deci m a l output on the seven segme nt display. Inputs not connected to any value are

considered as 'floati n g' HI G H , thus causing the display to turn off when not in use.

6. DIGITAL CLOCKS

T w o fixed cloc ks are prov i d e d by the board, one havin g a frequenc y of 100 H z and the

other 1 k H z. The frequen c y of cloc k 1 (CL K 1) can be changed by putti n g across capacit ors

in C1 and – . A capacit or value of 47 uF wil l decrease the frequenc y to aroun d 2 Hz. The

frequenc y of cloc k 2 (CL K 2) can be changed by puttin g across capacit o rs in C2 and – .

Laboratory Exercises

0. Discrete Gates

This laboratory exercise aims to relate logic gates with discrete electronic elements

such as diodes and transistors. By using a truth table, determine the logic function performed

by the circuits below. Assume that a voltage of 0 to 0.8V is a logic LOW and a voltage of

2.4V to 5V is a logic HIGH. Explain why you are getting the output voltage levels for each

circuit. Are these the expected values for the given circuit?

1. LOGIC GATES

Objective

To fam i l i a r i z e the students wit h the use of T T L (transistor- transistor logic) G A T E S and the

truth table.

Logic Gates

A logic gate perf or m s a logical operati o n on one or more logic inputs and prod uc es a single

logi c output. Since the output is also a logic- level value, an output of one logic gate can be

connected to the input of one or more other logic gates. The logic nor m a l l y perfor m e d is

Boo l ean logic and is most com m o n l y foun d in digital circu its

The most com m o n logic operatio ns are N O T, O R and A N D .

NOT

This logic operati o n outputs the com p l i m e n t of the operand. For exam p l e, N O T 1 = 0 and

N O T 0 = 1. The sym b o ls used to represent the N O T operati o n are the tilde “~” before the

operand ( ), a min us sign “ “ before the operand ( ), a pri m e sym b o l “ “ ( ) after the

operand or a bar over the operand ( )

Exa m p l es:

or

or

OR

This logic operat io n outputs 1 if at least one operand is equal to 1. For exa m p l e, 1

O R 0 O R 1 O R 0 = 1. The sym b o l used to represent the O R operat io n is a plus sign “ ”

bet ween operands (

).

Exa m p l e:

1

AND

This logic operati o n outputs 1 if and only if all operands are equal to 1. For exam p l e, 1 A N D

0 A N D 1 A N D 1 = 0. The sym b o ls used to represent the A N D operatio n are the ampersan d “

” or the dot prod uc t “٠” bet wee n operands (

).

Exa m p l e:

or

Truth tables

A truth table is a table that describes the behav i o r of a logic gate. It lists the value of the

output for every possible com b i n a t i o n of the inputs. Table 1 sho ws the truth table for a N O T

operati o n, Table 2 sho ws the truth table for a two- input A N D operatio n and table 3 sho ws the

truth table for a two- input OR operati o n.

Table 1. NOT, AN D and OR Truth Tables

A

NOT (A)

0

1

1

0

A

B

A AND B

0

0

0

0

1

0

1

0

0

1

1

1

A

B

A OR B

0

0

0

0

1

1

1

0

1

1

1

1

Logic Symbol

a. Basic Logic Gate Exercise

The logic gates that we will use are integrated chips (ICs) that use transistors to perform

logical operations, thus they are called transistor-transistor logic (TTL) ICs. The ICs that you

will be using are quad 2-input logic gates; there are four logic gate units in each IC taking in

two separate inputs each.

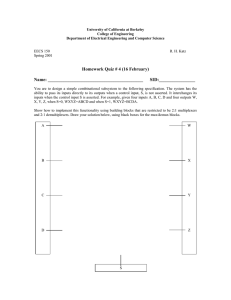

Each group will be provided with two of the following ICs: 74LS00, 74LS02, 74LS08,

and 74LS32. These are the AND, OR, NAND (NOT AND) and NOR (NOT OR) quad gates

(not respectively or not necessarily in that order). The pin assignments are shown below:

Note:

1A, 1B are the inputs and 1Y is the output for the first logic gate in the IC;

2A, 2B are the inputs and 2Y is the output for the second logic gate in the IC;

and so on...

Vcc is the supply voltage of the IC.

For TTL, Vcc should be +5V ± 5% ,i.e., 4.75V to 5.25V.

GND is the ground pin or 0V.

Two volts (2V) to five volts (5V) applied to an input of the IC is considered a high signal

(logic 1). While 0V to 0.8V is considered a low signal (logic 0). Greater than 0.8V and

lower than 2V is considered undefined. This voltage requirement is for TTL but for other

low-powered ICs like LVTTL, LVCMOS, the voltage requirements for a high signal is lower.

You can use logic switches SW0 and SW1 as your inputs. Use the logic probe or LED0 for

the output, construct the truth table for each of the ICs as shown below:

Exhaust all possible combinations of inputs and check the outputs of each.

SW0 = 1A

SW1 = 1B

0

0

0

1

1

0

1

1

1Y of 7400

Based on your truth table, the logic function of 7400 is ________________

SW0 = 1A

SW1 = 1B

0

0

0

1

1

0

1

1

1Y of 7402

Based on your truth table, the logic function of 7402 is ________________

SW0 = 1A

SW1 = 1B

0

0

0

1

1

0

1

1

1Y of 7408

Based on your truth table, the logic function of 7408 is ________________

SW0 = 1A

SW1 = 1B

0

0

0

1

1

0

1

1

1Y of 7432

Based on your truth table, the logic function of 7432 is ________________

b. Application

1.

The truth table below implements a 3-bit majority one circuit i.e. the output is 1 when

the number of 1s in the input is a majority ( 2 or more 1s). Implement the truth table given

below.

A

B

C

OUT

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

Write the equation for the 3-bit majority one circuit (OUT). Draw the circuit

diagram. Construct the circuit using AND-OR-NOT gates.

FYI, The NOT gate or inverter IC is 74LS04, shown below.

2.

A house alarm system has three inputs – alarm enable (E), door intruder (D) sensor

and window intruder (W) sensor. The alarm (A) will turn on if the alarm is enabled (E) and

the door intruder sensor (D) or window intruder sensor (W) is activated. The alarm will not

be activated, if the alarm is not enabled even if there is an intruder coming from the door or

the window. Alarm enable is ON when E = 1. The door intruder sensor is ACTIVATED

when D = 0. The window intruder sensor is ACTIVATED when W = 0.

Construct a truth table for the house alarm system. Using the ICs provided, construct

such an alarm system. Write the equation for the alarm system (A). Draw the circuit or

schematic diagram of your designed alarm system. You may ask for additional ICs from your

instructor like the 74LS04, which is a NOT gate or an inverter.

3. Basic Combinational Circuit Lab. Exercise

AND-OR-NOT. This laboratory exercise requires the design of a simple combinational

circuits using AND-OR-NOT gates (i.e. 74xx08, 74xx32 & 74xx04). This exercise aims to

familiarize the students in the use of logic gates as well as implementing circuits from a truth

table.

Group 1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

1

1

1

1

0

1

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

0

0

0

0

0

1

1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

1

0

1

1

0

0

0

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

1

1

1

0

0

0

1

Group 2

Group 3

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

0

0

1

0

0

0

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

1

1

1

0

0

1

1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

1

0

1

0

0

1

0

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

0

1

1

0

1

1

1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

1

0

0

0

1

1

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

0

0

0

1

1

0

0

Group 4

Group 5

Group 6

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

1

1

1

1

0

0

0

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

0

0

1

1

1

1

1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

0

1

0

0

1

1

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

1

0

0

0

1

0

1

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

0

1

0

1

1

0

1

0

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

1

1

1

1

0

1

1

Group 7

Group 8

4. NAND Gates. This laboratory exercise requires the design of a simple combinational

circuits using NAND gates (i.e. 74xx00, 74xx10 or 74xx20). This exercise provides some

insight into intuitive minimization at the package level (number of ICs used) rather than the

gate level.

set A

(assigned to groups 1 & 8)

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

0

0

0

1

1

1

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

0

0

1

0

0

1

1

f

0

0

0

1

0

0

1

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

1

1

1

0

0

1

1

set B

(assigned to groups 2 & 7)

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

set C

(assigned to groups 3 & 7)

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

f

0

1

0

1

0

1

0

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

0

0

0

1

1

1

1

1

f

0

0

0

1

0

0

0

1

wxyz

1000

1001

1010

1011

1100

1101

1110

1111

f

1

1

1

1

0

1

0

1

set B

(assigned to groups 4 & 5)

wxyz

0000

0001

0010

0011

0100

0101

0110

0111

Paper Design (to be included in the lab report). Design and implement a 4-bit

majority-1 circuit using NAND gates (i.e. 74xx00, 74xx10 or 74xx20). A majority-1 circuit

is a circuit that outputs a 1 when three or four of the inputs are1.

2. Digital Meets Analog Lab Exercise

Seat Belt Warning System. In a certain seat belt warning system, a warning indicator is

activated (turned on, high logic or logic 1) when at least one of the car passenger is not

wearing the seat belt. Design a circuit (no need to simplify, use AND-OR-NOT gates) that

will show the seat belt warning system output. Use this digital seat belt warning system

output to control a buzzer. Note that the digital output might not be able to drive the buzzer

so you have to use a transistor driver or an amplifier circuit. The system will work regardless

of the number of passengers inside the car.

Assume: car is 4-seater, each seat has a sensor (S1, S2, S3, S4) and each seat belt has a

sensor (B1, B2, B3, B4 corresponding to each seat sensor). Seat sensor is high (1) when it is

occupied else low (0). Seat belt sensor is high when it is being used else it is low.

Light Sensor with Motor Control. You are to design a light sensor input system and motor

control circuit. It consists of three input variables and two output variables. The variables

are described as follows: (3) selectors and (2) controls. The selectors (S2, S1 and S0) are

input signals coming from the light sensors (L1 and L0) and a switch, S1 = 1 when L1 is

activated (light sensor ON) and S0 = 1 when L0 is activated (light sensor ON), S2 = 1 when

the switch is ON. The control variables (C1 and C0) are output signals to the analog circuit

that controls the DC motors (M1 and M0). The selector inputs (S2, S1 and S0) determine the

motor functions (C1, C0) as follows:

S2 S1 S0

C1C0

function description

0 0 0

1 1

forward

: both motors are ON

0 0 1

0 1

turn right

: M1 is ON, M0 is OFF

0 1 0

1 0

turn left

: M1 is OFF, M0 is ON

0 1 1

1 1

forward

: both motors are ON

1 X X

0 0

stop

: both motors are OFF

Note: In the absence of DC motors, a tungsten lamp maybe used to simulate the

activation of the motor.

3. Full-adder & full-subtractor

Objective:

To fam i l ia r i z e the students wit h the construc t i o n and vario us imp le m e n t at i o n s of A d de r and

Subtract o r circ uits.

Half-Adder

A half-Adder is a com b i n at i o n a l logic circuit that is able to perf or m the addit i o n of two bits.

It takes two input signals, X and Y, adds them and outputs a sum (S) and carry (C). This ad diti o n consists of four possible com b i n a t i o ns of inputs and outputs, namel y, 0+0=0, 0+1 = 1,

1+0= 1 and 1+ 1 = 1 0. The first three operatio ns have a sum whose lengt h is only 1 bit but the

fourt h, has a sum that consists of two digits. The carry is the higher signi f i c a n t bit of the two

digits in the fourt h possible com b i n at i o n.

The truth table belo w is deri ve d fro m this descript i o n.

INPUT

OUTPUT

X

Y

C(Carry)

0

0

0

0

1

0

1

0

0

1

1

1

S(Sum)

0

1

1

0

The Boo lean expressio n for each output can be deri ve d fro m the truth table:

The two im p le m e n t a t i o n s sho w n belo w of the half- adder circ uit are the sum of produ c ts and

produ c t of sums notatio n taken fro m the truth table above.

Sum of Produ c ts

Produ c t of Sums

Note that S is the exclus i v e- O R of X and Y. The com p le m e n t of S is the equiv ale n c e (exclu sive-N O R) of x and y.

Sum of Produ c ts

Produc t of Sums

The half- adder belo w is im p le m e n t e d using an exclusi v e- O R (XO R) and an A N D gate.

a. Construct a Full-Adder Circuit.

A full-adder is a combinational circuit that forms the arithmetic sum of three input

bits. It consists of three inputs and two outputs. Two of the input variables denoted by x and

y, represent the two significant bits to be added. The third input, z, represents the carry from

the previous lower significant position. Two outputs are necessary because the arithmetic

sum of three binary digits ranges in value from 0 to 3, and binary 2 or 3 needs two digits.

The two outputs are designated by the symbols S for sum and C for carry. The binary

variable S gives the value of the least significant bit of the sum. The binary variable C gives

the output carry. (C,S = X + Y + Z). The partial truth table of the full-adder is given below.

Kindly complete the table then implement the circuit. If you can, implement S and C using

only XOR, OR and AND gates.

X

Y

Z

C

S

0

0

0

0

0

0

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

1

0

1

1

1

0

1

1

1

1

1

Note: Don’t dismantle the circuit, you might need it in the succeeding exercise.

Shown below is an XOR gate IC, 74LS86.

b. Construction of a Full-Subtractor Circuit

A full-subtractor is a combinational circuit that performs a subtraction between two

bits, taking into consideration that a 1 may have been borrowed by a lower significant stage.

This circuit has three inputs and two outputs. The three inputs, x, y and z, denote the

minuend, subtrahend and previous borrow, respectively. The two outputs, D and B, represent

the difference and the output borrow, respectively. (B,D = X - Y - Z). The partial truth table

of the full-subtractor is given below. Kindly complete the table then implement the circuit.

If you can, implement D and B using the circuit constructed above and an INVERTER.

X

Y

Z

B

D

0

0

0

0

0

0

0

1

1

1

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1

1

0

1

1

1

1

1

4. Decoders

Objective

To fam i l ia r i z e the students wit h the use and applicat i o n of decoders in digital circ uits.

Decoders

A decoder is a mult i p l e- input, mult i p l e- output logic circu it that converts coded inputs into

coded outputs, where the input and output codes are dif fere nt such as n-to-2 n Binar y Coded

Deci m a l (BC D) decoders. Dec o ders have an enable pin, wh ic h needs to be turned on for the

decoder to funct i o n, other w i s e its outputs assume a single "disabled" output code wor d.

Deco d i n g is necessary in applicat i o ns such as data mult i p l e x i n g, 7 segment display and

me m o r y address decod i n g.

Let us consider n-to-2 n type binary decoders. These decoders are com b i n a t i o n a l circ ui ts that

convert binary inf or m a t i o n fro m 'n' nu m be r of coded inputs to a max i m u m nu m be r of 2 n

uniq ue outputs. We say a maximum number of 2 n outputs because if the 'n' bit coded

info r m a t i o n has unused bit com b i n at i o n s, the decoder wou l d have less than 2 n outputs.

A v a i l a b le decoders are the 2-to-4 decoder (74xx 1 3 9), 3-to-8 decoder (74xx 1 3 8) and 4-to-16

decoder (74xx 1 54). W e can for m a 3-to-8 decoder fro m two 2-to-4 decoders (with enable

signals). W e can for m a 4-to-16 decoder fro m two 3-to-8 decoders (with enable signals).

Exa m p l e: A 2-to-4 Line Dec o der (without an enable line)

Exa m p l e of T T L ICs (a) dual 2-to-4 decoders with enable (74LS139);

(b) 3-to-8 decoder with enable lines (74LS138)

Lab Exercise: a. For the 3-to-8 decoder IC (74LS138) verify that it does the following

function as shown in the table below:

IN

IN

G2B' G2A'

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

G1

C

B

A

Y0'

Y1'

Y2'

Y3'

Y4'

Y5'

Y6'

Y7'

X

X

0

X

X

X

1

1

1

1

1

1

1

1

X

1

X

X

X

X

1

1

1

1

1

1

1

1

1

X

X

X

X

X

1

1

1

1

1

1

1

1

0

0

1

0

0

0

0

1

1

1

1

1

1

1

0

0

1

0

0

1

1

0

1

1

1

1

1

1

0

0

1

0

1

0

1

1

0

1

1

1

1

1

0

0

1

0

1

1

1

1

1

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

0

1

1

1

1

1

1

0

1

0

0

1

1

1

1

1

1

1

1

1

1

1

0

Note: “X” means “don’t care”,i.e., may take the values of 0 or 1.

Connect inputs G2B', G2A', G1, C, B and A to switches sw5, sw4, sw3, sw2, sw1 and sw0

respectively. Connect the outputs Y0', Y1', Y2', Y3', Y4', Y5', Y6' and Y7' to LED0 to LED7

respectively.

IN

IN

G2B' G2A'

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

G1

C

B

A

Y0'

Y1'

Y2'

Y3'

Y4'

Y5'

Y6'

Y7'

X

X

0

X

X

X

X

1

X

X

X

X

1

X

X

X

X

X

0

0

1

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

0

0

1

0

1

1

0

0

1

1

0

0

0

0

1

1

0

1

0

0

1

1

1

0

0

0

1

1

1

1

b. Application:

4-to-16 decoder. Implement the following truth table using 3-to-8 decoders

(74xx138) and a 4-input NAND gate (74xx20). The inputs d, c, b and a are to be connected

to sw3, sw2, sw1 and sw0 respectively. Output f is to be connected to LED0.

set A (groups 1, 5 & 9)

dcba

0000

0001

0010

0011

0100

0101

0110

0111

f

1

0

0

0

1

0

0

1

Cont. dcba

1000

1001

1010

1011

1100

1101

1110

1111

Cont. f

0

0

0

0

0

0

1

0

set B (groups 2, 6 & 10)

dcba

0000

0001

0010

0011

0100

0101

0110

0111

set C (groups 3 & 7)

dcba

0000

0001

0010

0011

0100

0101

0110

0111

f

0

1

0

0

0

0

1

0

Cont. dcba

1000

1001

1010

1011

1100

1101

1110

1111

Cont. f

f

1

0

0

0

0

1

0

0

Cont. dcba

1000

1001

1010

1011

1100

1101

1110

1111

Cont. f

f

0

0

1

0

0

0

1

0

Cont. dcba

1000

1001

1010

1011

1100

1101

1110

1111

Cont. f

0

0

1

0

0

0

0

1

1

0

0

0

1

0

0

0

set D (groups 4 & 8)

dcba

0000

0001

0010

0011

0100

0101

0110

0111

0

0

0

0

1

0

0

1

Hint: Construct a 4-to-16 decoder with two 3-to-8 decoders (74LS138).

5. Multiplexers

A digital multiplexer or mux is a device that performs multiplexing; it selects one of many

digital input signals and outputs that into a single line.

Example of 2-to-1 Multiplexer (symbol shown above) without an enable signal.

Example of TTL ICs: (a) dual 4-to-1 multiplexer with enable (74LS153) and

(b) 8-to-1 multiplexer with enable line (74LS151).

Truth table for a 4-to-1 multiplexer:

Selector

Selector

Strobe/Enab

le

Output

Inverted Output

C

B

G'

Y

W

X

X

1

0

1

0

0

0

C0

C0'

0

1

0

C1

C1'

1

0

0

C2

C2'

1

1

0

C3

C3'

Application:

Tail Lights. You are to configure two multiplexers (74xx151 or equivalent) into a tail light

system. It consists of four input variables and two output variables. The four input variables

are describe as follows: (1) blinker and (3) selectors. The blinker input is connected to the

CLOCK output of the digital kit. Use an appropriate frequency setting (one where blinking

of LEDs can be observed) for the CLOCK output. The blinker is used to make the outputs

turn on and off (LEDs blink). The selector inputs (S2 = sw2, S1 = sw1 and S0 = sw0)

determine the tail light functions as follows:

S2

0

0

S1

0

0

S0

0

1

0

1

0

0

1

1

x

1

x

function description

do nothing

: the output LEDs are at logic low

turn right

: the right output LED is blinking while

the left output LED is at logic low.

turn left

: the left output LED is blinking while

the right output LED is at logic low

emergency

: all output LEDs are blinking

brake

: all output LEDs are at logic high

Where x means “don’t care” i.e. may take the values of 0 or 1.

Note: For better output display, connect two LEDs per output i.e. two LEDs for left signal

and two LEDs for right signal.

6. PL D

We will be using a PAL/PALCE/GAL16V8A (PLD with 16 programmable pins, 8 of

which are inputs and the other 8 as input/output). We will be using a PLD compiler. A

sample template accepted by the compiler is as follows:

Any line that starts with a bar ( | ) is considered as a compiler statement and any line

that does not start with a bar ( | ) is considered as a remark or a comment.

PLD Compiler Template

A.

Using Boolean equations

| Device_name in: (input_variable_declaration), io: (i/o_var_declaration)

| Boolean_equation

B.

Using Tables (Truth)

| Device_name in: (input_variable_declaration), io: (i/o_var_declaration)

| Table: input_var_list -> output_var_list

| { all_possible_input_combination -> output }

C.

Example

Implement using PLD.

xyz

000

001

010

011

100

101

110

111

f

0

1

1

1

0

0

1

0

using K-map: f = yz' + x'z

Using PAL/PALCE/GAL16V8A (say saved in file example.pld)

sol'n #1

| GAL16V8A in: (x,y,z), io: (f)

| f = (y & z' ) # (x' & z)

sol'n #2

| GAL16V8A in: (x,y,z), io: (f)

| table: x, y, z -> f

| { 000b -> 0

| 001b -> 1

| 010b -> 1

| 011b -> 1

| 100b -> 0

| 101b -> 0

| 110b -> 1

| 111b -> 0 }

sol'n #3

| GAL16V8A in: (x,y,z), io: (f)

| table: x, y, z -> f

| { 0 -> 0

| 1 -> 1

| 2 -> 1

| 3 -> 1

| 4 -> 0

| 5 -> 0

| 6 -> 1

| 7 -> 0 }

D.

Use of Compiler/Programmer

The compiler and programmer is located in c:\pld. So, from drive c, do the following

commands.

c:\> cd pld

c:\pld> pld example.pld

The pld.exe compiler, if no errors are encountered, will generate three (3) other files

namely *.lst, *.jed and *.vec files. These files are described as follows:

example.lst

-- contains the following

original file

the sum of product form of the equation or truth table

pin assignments *

fuse file (JEDEC format)

example.jed

-- contains the fuse file in JEDEC format that will be the input file

of the PLD programmer

example.vec -- the vector file containing the check vectors

If there is an error the .lst file will tell you where the error occurred.

* The pin assignment by default is as follows

pin 1 is reserved for the clock pulse

pin 2-9 for the inputs respectively

pin 10 is ground (gnd)

pin 11 is for flip-flop enable (not used at the moment)

pin 19-12 for outputs respectively

pin 20 is for Vcc (+5 V)

After generating the .jed file, run the PLD programmer (wpld.exe).

load the JEDEC file

check whether the PLD is blank

if not then bulk erase it

then program the PLD

You are all set (the default pin assignment will be 10 for gnd, 20 for Vcc, 2 for X, 3

for Y, 4 for Z and 19 for f).

The Lab. Exercise

1.

Binary-to-seven-segment decoder. You are to program your PLD into a

binary to 7-segment decoder. The decoder is a combinational circuit that accepts 4-bit input

and generates the appropriate outputs for selection of segments in a display indicator used for

displaying the decimal digit or letter (we'll be using hexadecimal representation). The seven

outputs of the decoder (a, b, c, d, e, f and g) select the corresponding segments in the display

as shown below (a).

(a)

As a preliminary exercise, you are to find the pin assignment for the seven-segment

LED display using only a +5V supply and a 1k ohm resistor. Have a nice day!

2.

Tail Lights. You are to program a PLD into a tail light system. It consists of four

input variables and two output variables. The four input variables are describe as follows: (1)

blinker and (3) selectors. The blinker input is connected to the TTL output of the function

generator. Use an appropriate frequency setting (one where blinking of LEDS can be

observed) for the TTL output. The blinker is used to make the outputs turn on and off (LEDS

blink). The selector inputs (S2, S1 and S0) determine the tail light functions as follows:

S2

0

0

S1

0

0

S0

0

1

function description

do nothing

: the output LEDs are at logic low

turn right

: the right output LED is blinking while

the left output LED is at logic

0

1

0

turn left

0

1

1

x

1

x

brake

emergency

low.

3.

: the left output LED is blinking while

the right output LED is at logic low

: all output LEDs are at logic high

: all output LEDs are blinking

Optional. To be assigned by your lab. instructor.

7. FLIP-FLOPS and

SEQUENTIAL CIRCUIT

Objective

To fam i l ia r i z e the students wit h the construc t i o n and use of dif ferent types of flip- flops in

digital circ uits.

Flip-Flops

A flip-flop maintai ns a binary state indef i n i t e l y (as long as the circuit is po were d) until it

recei v es an input signal to switc h states. There are vario us types of flip flops that dif fer in the

nu m b er of inputs they possess and ho w the inputs affect the binary state.

Basic Flip-Flop/SR Latch

The basic flip-flop or the SR latch has two inputs, the set(S) and reset(R). The sche mat i c for

a basic flip- flop is sho w n belo w. A N O R gate outputs a logic lo w when there is at least one

logi c high input. It only outputs logic high when all inputs are zero.

W he n logic high is applied to the set(S) input and a logic lo w is fed to the reset(R) input, the

botto m N O R gate outputs a logic lo w due to the logic high of the S input regardless of what

is the value of the other input. The logic lo w output of the botto m N O R gate is then fed to the

upper N O R gate, together wit h the logic lo w of the R input. The result i n g output fro m the

S=1, R=0 input com b i n at i o n is Q= 1, Q’=0. The oppos ite happens when R= 1 and S=0, the

result i n g output is Q=0 and Q’= 1. W he n Q= 1 and Q’=0, it is said to be in the set state and

when Q=0 and Q’= 1, it is in the clear state.

N A N D gates can also be used to construc t a basic flip- flop. Its dif f eren ce is that to acti vate

the set mode, a 0 must be fed to the input S whi le input t i n g a 1 to the input R, oppos ite of the

N O R im p le m e n t at i o n.

Exercise

For the N O R im p le m e n t at i o n of the basic flip- flop, do the com b i n at i o n of inputs S and R

belo w, in order and record the output into the truth table. Con nec t inputs S and R to switc hes

sw 1 and sw0 respect i v e l y. Con nec t outputs Q and Q’ to LE D 1 and LE D 0 respecti v e l y.

Deter m i n e wh ic h com b i n at i o n of inputs should be avoided because of its outputs.

S

1

0

0

0

1

R

0

0

1

0

1

Q

1

1

0

0

0

Q’

0

0

1

1

0

RS Flip- Flop

The RS flip-flop is a mod i f i e d basic flip- flop where an addit i o na l input contro ls when the

states of the flip- flop change. The basic flip- flop changes states as soon as the inputs change

wh i l e an RS flip- flop changes states at the next cloc k pulse. The truth table for the changi n g

state of the Q output of the RS flip- flop is sho w n belo w.

Q

S

R

Q(t+1)

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

Indeter m i n a t e

1

0

0

1

1

0

1

0

1

1

0

1

1

1

1

Indeter m i n a t e

W he re Q is the present state and Q(t+1) is the next state of the output. Note that whene v er S

and R are both high, the next state is indeter m i n a t e because it places zeroes into the inputs of

the basic flip- flop used and makes outputs Q and Q’ both high, whi c h is avoided because

both must be com p le m e n t s of each other.

Exercise

Constr uc t an RS Flip- flop by addin g two more N A N D gates to the N A N D imp le m e n t a t i o n of

the basic flip- flop circ uit. Con nec t the three input elements, CP(cloc k pulse), S(set) and

R(reset) to the pulser, sw 1 and sw0 of the digital kit respecti v e l y. Con nec t outputs Q and Q’

to LE D 1 and LE D 0 respect i v e l y. Ma k e the pulser’s speed lo w enoug h to observe the cloc k

pulse. The mo m e n t the cloc k pulse goes high, the logic high of either the S or R input shoul d

be fed into the inputs of the basic flip- flop. Ver i f y that the cloc k contro ls the state change by

observ i n g when the outputs change state.

D Flip-Flop

The D flip-flop addresses the proble m of the RS flip- flop about both inputs being 1 at the

same time. The sole input, D is connected to the S input wh i le its inverted value is fed into

the reset input of the RS flip- flop to ensure that only one input is high and the other, lo w at a

ti me. If D is 1, the next state of the output Q goes to 1 and when D is 0, the next state of the

output Q beco m es 0.

Exercise

Constr uc t the D flip- flop fro m the N A N D imp le m e n t a t i o n of the RS flip- flop. Co m p l e t e the

truth table of the D flip- flop belo w.

Q

D

Q(t+1)

0

0

0

1

0

1

0

1

0

1

1

1

JK Flip-Flop

The JK flip- flop is another mod i f i c a t i o n of the RS flip- flop whi c h has its ow n way of deali ng

wit h the RS flip- flop’s undesirab le input com b i n at i o n (when S= 1 and R= 1). The JK flip- flop

has 2 inputs J and K, each A N D e d wit h the cloc k pulse and its correspo n d i n g N O R output.

The sche m at i c for the JK flip- flop is sho w n belo w.

Exercise

Constr uc t the JK flip- flop circ uit. Observ e what happen when the inputs are J=1 and K = 1 .

Co m p l e t e the truth table for the next state output belo w.

Q

J

K

Q(t+1)

0

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

0

1

1

1

T Flip-Flop

The T flip- flop is a mod i f i c a t i o n of the JK flip- flop but it has only one input instead of two

inputs that the JK flip- flop has. The next state is depende nt on the value of the input T. W h e n

T=0, the next state output is retained but when T= 1, the next state output is the oppos ite of

the present state.

Q

T

Q(t+1)

0

0

0

0

1

1

1

0

1

1

1

0

Exercise

Dra w and construc t the sche m at i c for the T flip- flop based on the infor m a t i o n you have

gathered fro m the JK flip- flop and the descript i o n of the T flip- flop. Ver i f y your circu it using

the T flip- flop’s truth table.

SEQU E N T I A L CI R C U I T E X E R C I S E S

Set 1/5/9

A.

Design a counter using D flip-flops. The circuit counts 0-1-3-7-15-7-3-1-0-1-3-etc.

a.

give the state diagram & the transition table

b.

the expressions for the D inputs

c.

the expression for the output if any

d.

the logic diagram

e.

do the actual circuit implementation

-------------------------------------------------------------------------------------------------------------Set 2/6/10

C.

Design a counter using D flip-flops. The circuit counts 0-8-12-14-15-14-12-8-0-8-12etc.

a.

give the state diagram & the transition table

b.

the expressions for the D inputs

c.

the expression for the output if any

d.

the logic diagram

e.

do the actual circuit implementation

-------------------------------------------------------------------------------------------------------------Set 3/7/11

E. Design a counter using D flip-flops. The circuit counts 0-1-3-7-15-0-1-3-7-15-0-1-etc.

a.

give the state diagram & the transition table

b.

the expressions for the D inputs

c.

the expression for the output if any

d.

the logic diagram

e.

do the actual circuit implementation

-------------------------------------------------------------------------------------------------------------Set 4/8/12

F. Design a counter using D flip-flops. The circuit counts 0-8-12-14-15-0-8-12-14-15-0-8etc.

a.

give the state diagram & the transition table

b.

the expressions for the D inputs

c.

the expression for the output if any

d.

the logic diagram

e.

do the actual circuit implementation

FYI, The D-flip-flop IC is 74LS74, shown below.

PRE'

CLR'

CLK

D

Q

Q'

0

1

X

X

1

0

1

0

X

X

0

1

0

0

X

X

1

1

1

1

POS

0

0

1

1

1

POS

1

1

0

1

1

0

X

Q0

Q'0

LEGEND:

0 = logic low

1 = logic high

X = don't care

POS = positive edge of clock, low to high transition.

Q0, Q'0, means previous values of Q i.e. retain old value (HOLD)

8. COUNTERS

Construct a digital circuit that counts from 00 to 99 using two BCD counters (2 x 74LS190)

and necessary gates. Use the 7-segment display of the digital design kit to show the counter

output. Use the digital kit variable clock for the clock input of the counter. Use an

appropriate frequency. You can connect CTEN' input to sw0 to make it an up or down

counter.

CTEN'

D/U'

CLK

LOAD'

A B C D

QA

QB

QC

QD

RCO' MAX/

MIN

0

X

X

0

a b c d

a

b

c

d

*

**

0

1

POS

1

X X X X

Count

down

Count

down

Count

down

Count

down

*

**

0

0

POS

1

X X X X

Count

up

Count

up

Count

up

Count

up

*

**

1

X

X

X

X X X X

QA0

QB0

QC0

QD0

*

**

LEGEND:

0 = logic low

1 = logic high

X = don't care

POS = positive edge of clock, low to high transition.

QA0, QB0, QC0, QD0 means previous values of Q i.e. retain old value

Count down means if previous count is 7, new count is 6

Count up means if previous count is 7, new count is 8

* = during the UP count MAX/MIN goes HIGH at count 9, during the DOWN count

MAX/MIN goes HIGH at count 0.

** = during the UP count RCO goes LOW at count 9, during the DOWN count RCO

goes LOW at count 0.

9. SHIFT REGISTER

Construct a digital circuit that counts 0,1,3,7,15,31,63,127,255 then back to zero using two

universal shift registers (2 x 74LS194) and necessary gates. Use the 8 LEDs to display

output. Use the digital kit variable clock for the clock input. Use an appropriate frequency.

MODE

INPUTS

CLR'

S1 S0

CLK

0

X X

1

OUT- PUTS

SL SR

A B C D

QA

QB

QC

QD

X

X

X

X X X X

0

0

0

0

X X

0

X

X

X X X X

QA0

QB0

QC0

QD0

1

1 1

POS

X

X

a b c d

a

b

c

d

1

0 1

POS

X

1

X X X X

1

Qan

Qbn

QCn

1

0 1

POS

X

0

X X X X

0

Qan

Qbn

QCn

1

1 0

POS

1

X

X X X X

Qbn

Qcn

Qdn

1

1

1 0

POS

0

X

X X X X

QBn

QCn

Qdn

0

1

0 0

X

X

X

X X X X

QA0

QB0

QC0

QD0

LEGEND:

0 = logic low

1 = logic high

X = don't care

POS = positive edge of clock, low to high transition.

QA0, QB0, QC0, QD0 means previous values of Q i.e. retain old value

10. Mini-PROJECTS :-)

Possible Projects:

a. T-BIRD TAILIGHTS

The design of a circuit that emulates the operation of the taillights of a Thunderbird is

carried out in this project.

Lab. Exercise

You are to design and build a circuit that controls the eight taillights on a

Thunderbird. Use eight LEDs to simulate the eight taillights (four on each side of the car),

and use two toggle switches (L & R) for the turn signals and another for brake (B).

The turn signals and brake (L, R and B) determine the tail light functions as follows:

B

0

0

L

0

0

R

0

1

function

do nothing

turn right

0

1

0

turn left

0

1

1

1

0

0

1

0

1

emergency

brake

brake + right

turn

1

1

0

brake + left turn

1

1

1

parked light

description

the output LEDs are at logic low

the 4 rightmost output LEDs should

cycle as shown in figure 1 while the

4 leftmost output LEDs are at logic

low.

the 4 leftmost output LEDs should

cycle as shown below while the 4

rightmost output LEDs are at logic

low.

all output LEDs are blinking

all output LEDs are at logic high

the 4 rightmost output LEDs should

cycle as shown below while the 4

leftmost output LEDs are at logic

high.

the 4 leftmost output LEDs should

cycle as shown below while the 4

rightmost output LEDs are at logic

high.

all output LEDs are on

LED Pattern:

Left turn: 0000 -> 0001 -> 0011 -> 0111 -> 1111 -> 0000 and so on

Right turn: 0000 -> 1000 -> 1100 -> 1110 -> 1111 -> 0000 and so on

0 = LED off

1 = LED on

b. LAMP PING- PONG

The design of the Ping-Pong machine for two human players is carried out in this

project. The machine is an amusing application of shift registers as well as an exposure to

control logic.

Design and construct a circuit that allows two people to play Ping-Pong using eight

indicator lamps in a row to display the moving ball and using two push button (or toggle

switches) for paddles.

Use two cascaded 4-bit shift registers containing a single turned on LED to represent

the ball. Use one push button (toggle switch) for the right-hand user, one for the left-hand

user. The ball should be moved by a clock source that causes a shift once every quarter

second or so. When the ball is moving to the right, the right-hand player must depress his

push button (toggle switch) at the time the ball is in its rightmost position. (The circuit

should be sensitive only to the leading edge of the push button signal or toggle switch). If the

player pushes at the correct time, the direction of the shift should be reversed and the ball

should move toward to the left. The left-hand player must then the volley by pressing his

button (toggle switch) when the ball is in its leftmost position. If a player presses his push

button (toggle switch) too soon or too late, the ball should disappear at the end. When this

happens, the player who has scored should be able to restart the game (serve) by pressing his

push button (toggle switch).

OPTIONS

A number of options can be provided to make the game more interesting.

First of all, provide a number of different rates at which the ball can move. The rate

of ball movement should be selected automatically as each player return a volley. The rate

selected should be a function of how the volley is returned, perhaps with the fastest rate

selected when the volley is returned at the last possible moment. To implement this feature

you will need control circuitry to select a rate, a register to store the rate, and a counter to

generate the different rates.

A second option is to keep score. Each player’s score should be kept in a 4-bit

counter. The 4-bit scores should be displayed in the lights whenever the ball is out of play.

c. Student Proposal :-)

11. IC Symbol & Pin-Outs