Corfin TMTI Report - Corfin Industries, LLC Component

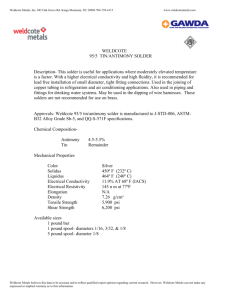

advertisement