Thin gate oxide damage due to plasma processing

advertisement

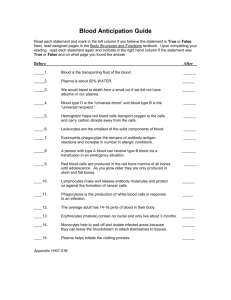

Semicond. Sci. Technol. 11 (1996) 463–473. Printed in the UK TOPICAL REVIEW Thin gate oxide damage due to plasma processing H C Shin† and Chenming Hu Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720, USA Received 9 May 1995, in final form 22 September 1995, accepted for publication 18 October 1995 Abstract. Plasma processes cause current to flow through the thin oxide and the resultant plasma-induced damage can be simulated and modelled as damage produced by constant-current (or voltage) electrical stress. Plasma processing causes MOSFET parameter degradation, from which one can deduce the plasma charging current. Since the scattering of post-damage device parameters is due to a reproducible variation of stress current across the wafer, one can easily analyse the effect of device geometry on damage by comparing test structures in the same die rather than the averages over a wafer. We have developed a quantitative model for thin oxide plasma charging damage by examining the oxide thickness dependence of the charging current. The model successfully predicts the oxide thickness dependence of plasma charging. It is shown that plasma acting on a very thin oxide during processing may be modelled essentially as a current source. Thus the damage will not be greatly exacerbated as the oxide thickness is further reduced in the future. Although annealing in forming gas can passivate the traps generated during plasma etching, subsequent Fowler–Nordheim stressing causes more traps to be generated in these devices than in devices that have not been through plasma etching. The protection diode should be forward biased during processing to safely protect the gate oxide. In CMOS circuits, the drains of the driver circuit can generally act as adequate protection diodes for the oxide regardless of N or P substrate and the polarity of the plasma charging current. The plasma stress current can be reduced by reducing the ion density, which is unfortunately linked to the etch rate or directionality, or by reducing the electron temperature. Maintaining a very uniform plasma over the surface of the wafer, reducing the plasma charging current during the over-etch time and judicious use of protection diode and antenna design rules will reduce plasma damage to an acceptable level for ULSI production even for very thin gate oxides. 1. Introduction Plasma processes are widely used in the manufacturing of VLSI devices for etching of polysilicon, oxide and metal films, oxide deposition, sputter pre-clean prior to PVD (physical vapour deposition), photoresist stripping and even ion implantation. During plasma processing, devices fabricated on silicon wafers are usually directly exposed to plasma. In the plasma ambient, ions and electrons are generated in the discharge. The ions are accelerated by the bias or self-bias voltage toward the surface of the wafer. The accelerated ions either physically sputter substrate materials or help chemical reactions to occur on the surface. Since the ion flux mainly bombards the wafer † Present address: Motorola Inc., Advanced Custom Technologies, Mesa, AZ 85202, USA. c 1996 IOP Publishing Ltd 0268-1242/96/040463+11$19.50 surface in the perpendicular direction, plasma etching can be directional (anisotropic). However, degradation of gate oxides in MOS devices due to plasma processing has been observed and attributed to electrical charging during the process [1–23]. In the plasma ambient, ions and electrons are collected by metal or polysilicon electrodes, which serve as ‘antennas’. A steady-state voltage appears on the electrode due to charge collection and the resulting electrical stress can destroy the underlying gate oxide by oxide breakdown or weaken it by causing charge trapping in the oxide as well as interface trap generation at the SiO2 –Si interface. Since the damaged oxide may cause IC yield loss or become more vulnerable to hot-carrier induced degradation and time-dependent dielectric breakdown (TDDB), plasma-induced gate oxide degradation is a serious problem in VLSI technology. Interface traps and charge trapping can be determined from 463 H C Shin and C Hu Figure 1. Conduction current during a 13.56 MHz rf plasma discharge [25]. There would be no or little damage if the areas under the ion current and the electron current are the same. MOSFET characteristics such as the subthreshold swing, threshold voltage or mobility. Quantitative monitoring of the interface traps and charge trapping is important since they are problems in the degradation of MOSFET performance and reliability [24]. This review describes the quantitative characterization of charging damage due to plasma processing. After the plasma damage model is presented, the determination of the oxide charging current using various MOSFET characteristics is explained. Using this technique, the effect of oxide thickness scaling on damage could be characterized. Also, the effect of a protection diode for wafer charging is discussed. Finally, we discuss several ways of reducing the plasma damage. 2. Plasma damage model During rf (radio frequency) plasma processes, the surface of the wafer collects conduction current Jp from the plasma which is composed of an ion current Ji and an electron current Je according to the well-known Langmuir theory [25] e(vp (t) − Vg ) Jp = Ji + Je = 0.6eni uB − 14 ene ue exp − kTe (1) is the ion density, u = where e is electronic charge, n i B √ eTe /M is the Bohm velocity, M is the ion mass, ue is the electron mean thermal velocity, ne is the electron density, vp (t) = V0 +VI sin(wt) is the self-generated plasma potential typically with frequency of 13.56 MHz, Te is the electron temperature and Vg is the gate (antenna) potential. Figure 1 shows the ion current and electron current as a function of time. The ion current Ji is almost constant with time and is determined by the ion density ni and the Bohm velocity uB . Since the plasma potential vp (t) is higher than the gate potential Vg for most of the time, the electron current flows only during the short periods when the plasma potential is near its minimum. If the ion and electron currents collected by an electrode balance each other perfectly over the rf cycle, plasma charging would not be a problem. Assuming a typical ion current density, Ji , of 10 pA µm−2 [10], an oxide thickness 464 Figure 2. The calculated transient behaviour of gate voltage on a 100 Å capacitor. The magnitude of the ripples is exaggerated in this figure. of 100 Å, an rf frequency, f , of 13.56 MHz and an antenna to oxide ratio of 1000, the maximum gate voltage rise over half of the rf period due to Ji is Ji × 1000 10 pA µm−2 × 1000 = 2f Cox 2 × 13.56 MHz × 345 nF cm−2 = 0.11 V. 1Vg = (2) This voltage excursion is reversed by the following Je pulse and the process starts again. The average Vg is close to zero and 1Vg is too small to cause significant electrical stress to the oxide. In equation (2), Cox represents the oxide capacitance per unit area. Charging occurs when the ion and electron currents do not balance each other through each rf cycle [12]. After averaging equation (1) over one cycle, the net average plasma charging current involves a modified Bessel function but can be approximated as eVg hJp i = Ji − Je0 exp (3) kTe where Je0 = 14 ene ue exp[−e(V0 − V1 )/kTe ] √ 2π(eV1 /kTe ) (4) is the magnitude of the electron current at Vg = 0 V [26, 27]. After the plasma is turned on, the gate voltage Vg increases or decreases over many rf cycles, depending on which component of the currents is larger, until a steadystate oxide voltage is reached when the Fowler–Nordheim (FN) tunnelling current through the oxide balances the net current collected by the antenna, hJp i. This tunnelling current degrades the oxide. The tunnelling current is always carried by electrons. For positive charging, when the ion current is larger than the average electron current, injection of electrons from the substrate occurs; and for negative charging, gate electron injection occurs. Electrons in transit in the oxide will gain kinetic energy by the electric field under FN tunnelling conditions and may gain still more energy as they arrive at the anode [28]. These ‘hot’ electrons are quite efficient in generating traps and interface Thin gate oxide damage due to plasma processing Figure 3. An equivalent circuit for oxide charging. At steady state, the plasma current Ip is equal to the oxide current IFN . states. Assuming a net current density hJp i of 2 pA µm−2 and an antenna ratio of 1000, the time to reach the steady state at Vg = 10 V is approximately Cox Vg 345 nF cm−2 × 10 V = 17.3µs = hJp i × 1000 2 pA µm−2 × 1000 (5) which is about 200 rf cycles long but very short compared with the typical plasma processing time of seconds or minutes. At steady state, the gate voltage is basically d.c. only with small 13.56 MHz ripples having amplitudes similar to that calculated from equation (2) as shown in figure 2. Therefore, the plasma charging can be modelled as a d.c. stress to the oxides (see section 3.3 for a discussion of the effect of a low-frequency rotating magnetic field.) Since this current flows through the oxide as a Fowler– Nordheim tunnelling current, the oxide voltage and hence the current is determined by equating hJp i of equation (3) and the FN current: hJp i × exposed antenna area = JFN thin oxide area 2 Vg BTox =A exp − (6) Tox Vg Tcharging = Figure 4. Id –Vg plots of a 10 nm oxide MOSFET for different antenna sizes after plasma ashing. Curve A is the I –V of a control device. The Id –Vg plots of MOSFETs with larger antennas show more degradation. 3.1. Effect of plasma charging on MOSFETs and capacitors oxide. Figure 4 shows the Id –Vg plot of MOSFETs with different aluminium antenna sizes after plasma ashing of photoresist without subsequent annealing. The photoresist stripping was done in a barrel-type stripper under normal conditions. The ashing gas was oxygen at 280 mTorr, the gas flow was 50 sccm and the power was 400 W. Control wafers receiving only wet processing were also fabricated. The size of the gate oxide is 50 × 1.4 µm2 with identical layouts except for the size of the aluminium antenna ranging from (80 µm)2 to (640 µm)2 . The Id –Vg for a wet-processed control device is also shown as curve A. We clearly observed the drift of threshold voltage Vt , which is due to the generation of interface traps and oxide trapping. Because a larger aluminium pad collects more charging current during ashing, the I –V curves of MOSFETs with larger pads show a higher degree of degradation. One can easily obtain threshold voltages of MOSFETs from figure 4. Since each gate oxide is covered with a polysilicon gate during plasma processing, the oxide damage through UV radiation is negligible. Moreover, the observed antenna effect (the dependence of damage on antenna size) also suggests that ionizing radiation due to UV or x-rays in the oxide is not the main source of damage. Rather, the charging mechanism described in section 2 is the cause of damage. The subthreshold swing (S) of plasma-damaged MOSFETs can be used to extract the interface trap density distribution. The subthreshold slope is given by Cit + Cd kT log 1 + S= q Cox Any device parameter that is sensitive to interface traps and oxide charge trapping may be used to monitor the plasma charging current. This section presents a quantitative method for characterizing plasma damage. The methodology can be applied to any specific equipment and process. Plasma processing degrades the MOSFET characteristics simply through Fowler–Nordheim electrical stress of where Cit = qDit and Cd are the capacitance due to interface traps and the depletion layer respectively. Figure 5, which compares the interface state distribution for different areas of aluminium antenna also indicates that devices with a larger aluminium pad size have a higher Dit . We can only obtain a small energy range of the Dit distribution for figure 5. When the Fermi level is near the midgap, the subthreshold current level is comparable to the where Tox is the oxide thickness and A = 20 µA V−2 , B = 250 MV cm−1 are known constants. Again, equation (6) determines the oxide stress voltage, Vg . Figure 3 shows a device during plasma processing and its equivalent circuit for oxide charging. At steady state, the plasma charging current Ip is equal to the oxide tunnelling current IFN . 3. Determination of the plasma charging damage and oxide stress current 465 H C Shin and C Hu Figure 6. Noise power density spectra for MOSFET saturation drain current. Figure 5. Energy distribution of interface states after plasma ashing for different aluminium antenna sizes. instrument sensitivity limit. This leads to an uncertainty in the extracted Dit . When the surface is near strong inversion there is no simple relationship between swing and Dit . Figure 6 shows the measured saturation draincurrent noise power as a function of frequency in the plasma-damaged MOSFETs with different antenna areas. Obviously, the larger the antenna size, the higher is the drain noise power. This confirms that plasma charging increases the density of interface traps, since the drain noise arises from charging and discharging of the traps through modulating both channel carrier number and surface mobility [29]. The drain 1/f noise of MOSFETs can be interpreted with a unified flicker noise model [29], which considers both the channel carrier fluctuation and the correlated surface mobility fluctuation. In the linear region (Vd = 0.05 V), the carrier density is uniform along the channel and is given by N = Cox (Vg − Vt )/q, and the drain-current noise power can be expressed as [29] SId (f ) = kT Id2 1 (1 + αµN )2 Nt∗ (x, E). γf W L N 2 (7) Nt∗ is the relevant near-interface oxide trap density, N is the area density of channel electrons, α ≈ 10−15 V s [30]. All the other parameters have their usual meanings. The oxide trap density Nt∗ can be extracted from the measured drain noise spectra. The extracted Nt∗ are 7.0 × 1016 , 1.4 × 1017 , 5.0 × 1017 , and 9.25 × 1017 cm−3 eV−1 for plasma-damaged devices with antenna areas of (80 µm)2 , (160 µm)2 , (320 µm)2 and (640 µm)2 respectively. These Nt∗ are 1.2–15 times higher than the 6.04×1016 cm−3 eV−1 of the control devices. Process-induced oxide charging can also be detected sensitively using a differential pair circuit shown in figure 7(a). This structure has the advantage over a singletransistor test structure of minimizing the variations of MOSFET parameters due to factors other than antenna size such as layout and location. The size of gate antenna A1 is fixed at (80 µm)2 whereas that of A2 is varied from (80 µm)2 to (640 µm)2 . The degradation of input transistor 466 Figure 7. (a ) Circuit diagram of a differential pair. The size of gate antenna A1 is (80 µm)2 , that of A2 is varied. The size of the input transistor is W /Leff = 50/1.4. (b ) The input offset voltage before and after ashing as a function of size of antenna A2 . M2 is larger than that of the M1 transistor, resulting in threshold and transconductance mismatches. Therefore, the input offset voltage of the circuit increases with larger size of antenna A2 whereas that of the wet-processed control circuit is almost independent of the size of A2 (figure 7(b)). Thin gate oxide damage due to plasma processing Figure 8. Shift in subthreshold swing (1S ), threshold voltage (1Vt ) and oxide trap density near the interface (1Nt∗ ) versus interface traps (1Dit ) for different antenna sizes. 1Nt∗ was calculated from noise. The relationships between all the parameters are linear. Figure 8 shows the subthreshold swing (S), threshold voltage (Vt ) and oxide trap density near interface (Nt∗ ) as a function of interface trap generation (determined from charge pump current) for devices with different antenna area. Since all the MOSFET parameters are correlated with each other through interface traps, any parameter can be used in quantifying the plasma charging stress. In our experience Vt shift as well as the differential pair mismatch are found to be more convenient to use than the other parameters as monitors of charging damage. 3.2. How to quantify the plasma antenna current Since the plasma-induced damage is primarily due to electrical charging, the damage to the gate oxide should be identical to that produced by applying a constant current to the gate electrode of a control unstressed device for a duration equal to the process time. The current necessary to reproduce the plasma-charging damage would correspond to that collected by the antenna during plasma processing. Control MOSFETs may be obtained by using minimum conductor (polysilicon or metal or via, etc) size and by perhaps using a protection diode where appropriate. Control devices may also be obtained by using a known benign process or equipment. Control MOSFETs were probe-stressed by passing different levels of current through the gate oxide for the same length as time as the plasma ashing (or over-ashing) time. Before stressing, MOSFETs on control wafers had identical I –V (curve A in figure 4) independent of the antenna geometry and a location across the wafer as expected. A series of control devices were stressed with varying levels of current to generate a series of reference curves, as shown in figure 9. Also shown in the figure is the I –V curve of a MOSFET having a (160 µm)2 aluminium pad with photoresist ashed in plasma. This curve lies between the reference curves of 500 pA and 1 nA stressing, indicating that the (160 µm)2 Al pad (curve C in figure 4) collected about 700 pA of oxide charging current during the ashing process. By using the same method, the plasma charging current for each MOSFET can be extracted Figure 9. Id –Vg plots of control MOSFETs after different FN current stressing under positive and negative gate stress for 20 min. Plasma-ash-induced damage can be closely reproduced with a constant-current stress. with a high resolution. Using an antenna ratio of 100, one can detect the plasma charge flux with a sensitivity of 1 mC cm−2 (of antenna area), sufficient for characterizing a typical plasma process charging of 10–1000 mC cm−2 . Even higher resolution may be obtained by using a larger antenna ratio. 3.3. Spatial distribution of oxide charging current across the wafer Using the technique described in the previous section, the oxide charging current distribution across the wafer can be characterized for a given set-up. Magnetized plasma etchers such as magnetically enhanced reactive ion etch (MERIE) reactors have been introduced as alternatives to conventional reactive ion etchers (RIE). To investigate the charging distribution in a MERIE etcher, Al was etched with a static magnetic field. Due to the static magnetic field perpendicular to the electric field inside the sheath region, secondary electrons emitted from the wafer surface drift with a cycloid motion toward one side of the wafer, enhancing the ionization process and increasing the plasma density there. Figure 10(a) shows the current path model for a static magnetic field MERIE. Current flows from the dense plasma region into the antennas, down through the oxide into the silicon substrate, and up into the weak plasma regions. For RIE etching, the wafer centre received more charging than the wafer edge (figure 10(b)). The distribution of the stress current during etching results from the radial distribution of the plasma density and etch rate in this etcher. Since oxide stressing effectively occurs after the Al has been etched into individual patterns (until then, the Al is likely to be shorted to the substrate through one defect), the devices near the wafer edge not only experience a lower charging current because of the lower plasma density but also spend little time in the plasma after the Al patterns are separated due to the slower etch rate. Figure 11(a) compares the statistical distributions of the threshold voltage before and after photoresist ashing. 467 H C Shin and C Hu Figure 10. A plasma charging current path model for RIE and MERIE etchers. Eighty devices were measured. Plasma ashing causes a shift in the mean as well as a broader spread in MOSFET threshold voltages. However, if we plot Vt after ashing for four different dies individually (figure 11(b)), the spread is not broader after ashing. The scattering of Vt values in figure 11(a) is not random but due to the spatial variation of the plasma stress across the wafer. Therefore, one can analyse the effect of device or antenna geometry on oxide damage more easily and accurately by comparing different test structures in the same die rather than the average over a wafer. 4. Oxide thickness scaling and charging damage There is an urgent concern about the effect of plasma processes on future thinner oxides. If today’s equipment and processes already cause damage in 15 nm gate oxide, would they not be totally unacceptable to future 8 nm or 6 nm oxides? In this section, a quantitative model to explain the oxide thickness dependence of plasma charging is presented. With this model one can predict the effect of plasma processes on future thinner oxides. The test structures used are fabricated on n-type (100) silicon substrate with 6.4 nm, 11.6 nm and 18.0 nm gate oxides. Al was etched using a parallel plate system at 250 W for 100 s. The photoresist was removed by a wet process. It is useful to understand why the charging current has a thickness dependence. Figure 12 compares the intersections (solutions) of equations (3) and (6) with experimentally deduced current and voltage for two antennas. Two sets of curves are shown. The first set is three curves of IFN (equation (6)) for the three oxide thicknesses. The second 468 Figure 11. (a ) Statistical distribution of threshold voltages before and after ashing. The standard deviation increased after ashing. (b ) Vt plots of devices in four different dies after ashing. The increase in standard deviation simply reflects the systematic radial position dependence of Vt shift. set is two curves of hJp i (equation (3)) for two antenna sizes. hIp i (equation (3)) is proportional to the exposed antenna area. Ji = 1.0 mA cm−2 can be calculated from the plasma d.c. voltage and sheath thickness (2 mm). Je0 = 60 µA cm−2 (or Ie0 = 8 nA) and Te = 4 eV (see equation (3)) can be found from a plot of ln(Ii − Ip ) versus Vg with Ip and Vg determined from the technique described in the section 3.2. Since the gate antenna voltage is smaller for a thinner oxide, the plasma charging current Ip is larger. Figure 12 shows that the charging current in a very thin oxide (Vg → 0 V) remains finite and approaches the ion current (equation (3)). Therefore, for thin oxides, it is better to think of the plasma as an imperfect current source with the current somewhat modified by the gate electrode voltage. The Dit generation in 6.4 nm oxide was less than in 11.6 nm oxide. It is due to the well known greater tolerance of thinner oxides to FN current stress and the fact that the plasma stress current does not increase very much with reducing oxide thickness. According to figure 12, an oxide of zero thickness will be stressed with only 20% more current than the 6.4 nm oxide in this etcher. Thin gate oxide damage due to plasma processing Figure 14. An equivalent circuit of gate oxide in parallel with (a ) a forward-biased protection diode and (b ) a reverse-biased protection diode. Figure 12. Plots of ‘Langmuir probe’ I –V (equation (3)) and oxide Fowler–Nordheim I –V (equation (6)). The oxide charging current Ip decreases with increasing oxide (gate) voltage since the electron current component in equation (3) is exponentially dependent on gate voltage Vg . Intersections of the two sets of I –V curves determine the oxide stress currents and voltages. Elongated aluminium antennas with the same area but different peripheral lengths were used. The area of Al antennas is 80 000 µm2 . Figure 13. (a) The density of interface traps generated during the Al etching is larger at the wafer centre. (b) The interface traps can be completely passivated with forming gas annealing. (c) The density of interface traps generated by subsequent FN stressing after plasma etching and forming gas anneal. Even though the traps were passivated with annealing, subsequent stress can regenerate 60% of the passivated traps. Figure 13(a) shows the increase of interface trap density after plasma etching. After the plasma-etched devices were annealed in forming gas, the interface traps generated during etching were completely passivated, presumably through the creation of Si–H bonds (curve b). To see whether or not the forming gas anneal provides a permanent cure for the traps generated during the etching, subsequent FN stressing was done to the annealed devices and compared with control devices. Figure 13 also compares the Dit of plasma-etched and annealed devices (curve c) and wet-etched devices after subsequent FN stressing. The devices were stressed by passing a constant current of 430 µA cm−2 through the gate oxide for 60 s. The Dit generated in control capacitors are independent of the position of the Al antenna size, as expected. The extra Dit in devices that had been plasma etched and annealed over the Dit in control devices are quite evident—note the similarity between curves a and c. The wafer position dependence of the extra Dit suggests that they are related to the traps which were previously generated during Al etching and subsequently passivated by annealing. Even though the interface states were passivated by forming gas anneal (curve b), about 60% of the traps reappeared after subsequent stress (curve c). Since the bonding between hydrogen and silicon formed during the anneal is not strong, with a 0.3 eV bonding energy, it can be broken during the FN stress resulting in higher Dit . This mechanism is probably the explanation for the reported deleterious effect of metal etching on MOSFET hot-carrier lifetime [35]. 6. Protection diode for wafer charging 5. Plasma etching antenna effect on oxide–silicon interface reliability Doubts have been raised about whether plasma etchinginduced interface trap generation can be cured by annealing. If such damage is eliminated in the annealing that usually follows metal etching, then perhaps it is of no practical significance except for the oxide shorts which are believed to be incurable. To pursue this issue, we study the effect of a forming gas anneal and the effect of subsequent electrical stress on oxides that have been damaged by plasma etching. Protection diodes have been used as a means of protection against wafer charging [4]. The protection can be obtained through forward-biased diodes or reverse-biased diodes during processing. Since the forward-biased diode can shunt a very large current density, the protection of oxides by even a very small forward-biased diode is very effective (figure 14(a)). However, the current through a reversebiased diode is a leakage current (under plasma illumination and high temperature) (figure 14(b)), and the effectiveness of protection depends on the relative magnitudes of plasma charging current and diode current. 469 H C Shin and C Hu Figure 15. Maximum voltage which can be sustained before breakdown of the gate oxide in 10 min and ground-gate junction breakdown. Oxides thinner than 11 nm are hardly protected by Zener protection diodes. Figure 17. Cross sections of CMOS with gate protection diodes connected: (a ) positive charging, (b ) negative charging. Figure 16. Reverse leakage current of the protection diode under the same light intensity as in a plasma ashing chamber. The current density of diodes shielded by metal was 6 µA cm−2 . If the protection diode is reverse biased and the diode leakage current is lower than the plasma charging current, the oxide may be stressed by the breakdown (Zener) voltage of the protection diode, i.e. MOSFET gated diode, which has the lowest breakdown voltage. Figure 15 shows the grounded-gate drain breakdown voltage and gate oxide breakdown voltage. The total plasma processing time was assumed to be 10 min. Gated diode breakdown provides little or no protection for oxide thinner than 11 nm. The reverse diode current density in a plasma ashing chamber, when not obstructed by a light-blocking metal, is found to be 75 µA cm−2 (figure 16) which is about 23 times larger than the plasma charging current density of 3.3 µA cm−2 for this ashing condition. The reverse leakage current of a 4 × 4 µm2 diode shielded by 80 × 80 µm2 aluminium was 6 µA cm−2 . Therefore the diode is effective only when the antenna to diode area ratio is less than 23, or less than 2 if the diode is shielded by metal from plasma illumination. Introducing strong illumination onto the wafer surface during processing can increase the effectiveness of protection by a reverse diode but may not be practical. As a rule of thumb, a simple small reverse protection 470 diode may be assumed to be non-conducting and ineffective in protection against plasma charging damage for an oxide thinner than 11 nm. On the other hand, a CMOS well junction typically has sufficient area relative to antenna size to be assumed to be conducting (see next paragraph). These assumptions may not apply to specific equipment or a particular test pattern. For example, a large capacitor may collect more antenna current than can a reverse well junction underneath. Figure 17 shows examples of forward and reverse diodes for protection in a CMOS circuit. Simple cross sections of typical CMOS circuits fabricated in twin-tub technology are shown in the figure. The output of a CMOS driver is connected to the gate oxide being considered for damage. Since the output signal is from the node which is simultaneously connected to the drains of an NMOSFET and a PMOSFET, drain-to-well junction diodes of the driver circuit act as the protection diodes for the oxide. For each polarity of charging, one of the protection diodes is forward biased and adequate protection can be always obtained. For example, if the polarity of charging is positive, the drain-to-well junction of the PMOSFET is forward biased (figure 17(a)). For P-substrate technology, the reverse biased well-to-substrate diode is in series with the forward biased p+ drain-to-well diode. The size of the well is usually big enough such that the well-to-substrate junction leakage current can drain away the antenna current. If the well-to-substrate reverse diode leakage is smaller than the current collected by the antenna, the oxide stress current is still reduced by the well leakage current. Thin gate oxide damage due to plasma processing Figure 18. Oxide charging current distribution perpendicular to the magnetic field during static-field MERIE etching. The charging current increases with B -field due to increasing plasma non-uniformity. Figure 19. Oxide charging current distribution across the wafer in a MERIE system with a rotating field. A rotating magnetic field of 75 G was used during etching. The plasma non-uniformity charging currents are larger for lower pressures. 7. How to reduce plasma charging damage Figure 18 shows the oxide charging current distribution in the direction perpendicular to the static magnetic field during poly etch in a MERIE etcher for three different magnetic fields. In this experiment, the magnetic field was either rotated at the normal 0.5 Hz or stationary. With a high magnetic field, the local imbalance between ion current and electron current is large, resulting in more charging to oxide. The breakdown rate of oxides also increases with magnetic field. Figure 19 shows the charging current distribution for three different pressures with rotating magnetic fields. The charging current for lower pressure is higher, owing to a more non-uniform plasma density. At the lower pressure electrons have a longer mean free path and magnetic field confinement is better, resulting in a higher plasma density gradient across the wafer. Plasma equipment which generates sufficiently uniform plasma across the wafer tends to reduce the damage. To investigate when the damage is done during plasma Figure 20. Dit generation versus total etching time. Most of the damage is done during over-etching. It took 41 s to completely etch through the Al film. Before that, Dit generation was negligible. process, the Dit generated in the devices during plasma etching of Al were measured after three different times of etching (figure 20). The endpoint of the etching was detected about 41 s after the plasma was on. Before reaching the endpoint, the Dit generation rate is negligible, probably because the stress current is shunted by some short from Al to ground. Dit is generated only during the overetch time, i.e. after the Al pad is isolated, and Dit increases with the over-etch time. To reduce the damage, one can decrease the rf power of the machine, or in the MERIE case decrease the magnetic field during the over-etch time or, better, before reaching the endpoint. Reliable and accurate endpoint detection is important. If the plasma is more uniform across the wafer, one can have a shorter over-etch time and further reduce the plasma damage. A dielectric layer can block the plasma charging, and this concept may be actively used to reduce charging damage. For example, during LDD (lightly doped drain) spacer oxide etching, the gate oxide damage is negligible if sufficient oxide remains over the top of polysilicon after etching [37]. The top oxide can block the charges. However, if the oxide remaining over the antenna has been sufficiently thinned, damage is observed to the gate oxide. The ‘hard mask’ oxide which is deposited over the antenna before spacer oxide deposition reduces oxide damage or increases tolerance for over-etching compared with the case without a TEOS cap oxide. Protection diodes are only effective on or after metal-1 etch. For antennas which cannot be protected by diodes (for example, during poly etch), design rules for antenna area and edge length to oxide area ratio should be established accordingly such that the charging current and time product should be less than 10 mC cm−2 so that the impact on oxide yield and the latent damage on hot-carrier lifetime and interface stability are tolerable. 8. Conclusions Plasma-induced oxide damage can be modelled as damage produced by electrical current or voltage stress. Plasma 471 H C Shin and C Hu processing causes MOSFET parameter degradation, from which one can deduce the plasma charging current. Since the scattering of post-damage device parameters is due to a reproducible variation of stress current across the wafer, one can easily analyse the effect of device geometry on damage by comparing the test structures in the same die rather than the averages over a wafer. For very thin oxides the plasma acts not as a fixed voltage source but rather as an imperfect current source. This is fortunate for future oxide scaling. The stress on the oxide is equivalent to applying a nearly fixed electric field which is weakly dependent on the gate oxide thickness. The effect of plasma etching on silicon–oxide interface reliability is also presented. The interface traps generated by plasma processing can be passivated with a forming gas anneal. However, subsequent FN stressing or hot-carrier stress, and probably temperature-bias stress, causes more damage in these devices than in the devices that have not been through plasma etching. This is the likely cause of the enhanced hot-carrier degradation in plasma-etched devices. This latent damage may be used to deduce the plasma stress current that the oxide has experienced, even if tests could not be performed before the damage is passivated by annealing. The protection diode should be forward biased during processing to safely protect the gate oxide. In CMOS circuits, the drains of the driver circuit can generally act as adequate protection diodes for the oxide regardless of the substrate being N or P and the polarity of plasma charging current. The plasma stress current can be reduced by reducing the ion density, which is unfortunately linked to etch rate or directionality, or by reducing the electron temperature. Maintaining a very uniform plasma over the surface of the wafer, reducing the plasma charging current during the over-etch time, judicious use of protection diodes and the antenna design rule will reduce plasma damage to acceptable level for ULSI production even for very thin gate oxide. Acknowledgments This research is sponsored by SRC, Signetics, TI, Rockwell International and AMD under MICRO program and ISTO/SDIO administered by ONR under contract N0001492-J-1757. References [1] Gabriel C and McVittie J 1992 How plasma etching damages thin gate oxides Solid State Technol. 35 June 81–7 [2] Shin H, Jha N, Qian X Y, Hills G W and Hu C 1993 Plasma etching charge-up damage to thin oxides Solid State Technol. 36 August 29 [3] Gabriel C 1991 Gate oxide damage from polysilicon etching J. Vac. Sci. Technol. B 9 370–3 [4] Shone F, Wu K, Shaw J, Hokelet E, Mittal S and Haranahalli A 1989 Gate oxide charging and its elimination for metal antenna capacitor and transistor in VLSI CMOS double layer metal technology Symp. VLSI Tech. Digest Papers 73–4 472 [5] Kawamoto Y 1985 Proc. 1985 Dry Process Symp (Japan: IEE) pp 132–7 [6] Tsunokuni K, Nojiri K, Kuboshima S and Hirobe K 1987 JSAP Extended Abstracts of the 19th Conf. on Solid State Devices and Materials pp 195–8 [7] Wu I-W, Bruce R H, Anderson G B, Koyanagi M and Huang T Y 1989 Damage to gate oxides in reactive ion etching Proc. SPIE 1185 284–95 [8] Brozek T, Chan Y and Viswanathan C 1995 Role of temperature in process-induced charging damage in sub-micron CMOS transistors IEDM Tech. Digest 311–14 [9] Wadanabe T and Yoshida Y 1984 Dielectric breakdown of gate insulator due to reactive ion etching Solid State Technol. April 263–6 [10] Shin H, King C-C and Hu C 1992 Thin oxide damage by plasma etching and ashing processes Proc. IEEE Int. Reliability Physics Symp. pp 37–41 [11] Fang S and McVittie J 1992 Thin-oxide damage from gate charging during plasma processing IEEE Electron Device Lett. 13 288–90 [12] Fang S and McVittie J 1992 A model and experiments for thin oxide damage from wafer charging in magnetron plasmas IEEE Electron Device Lett. 13 347–9 [13] Samukawa S 1990 Damage caused by stored charge during ECR plasma etching Japan. J. Appl. Phys. 29 980–5 [14] Samukawa S 1991 Dependence of gate oxide breakdown frequency on ion current density distributions during electron cyclotron resonance plasma etching Japan. J. Appl. Phys. 30 1902–4 [15] Sekine M, Horioka K, Matsushita T, Hishioka K, Matsunaga Y, Yoshida Y and Okano H 1991 Gate oxide breakdown phenomena in magnetized plasma Dry Process Symp. (Japan: IEE) pp 99–103 [16] Greene W, Kruger J and Kooi G 1991 Magnetron etching of polysilicon: electrical damage J. Vac. Sci. Technol. B 9 366–9 [17] Fang S, Murakawa S and McVittie J 1992 A new model for thin oxide degradation from wafer charging in plasma etching IEDM Tech. Digest 61–4 [18] Hashimoto K, Matsunaga D and Kanazawa M 1991 Quantitative evaluation of charge-up damage by using current sensitive MOS diodes Dry Process Symp. (Japan: IEE) pp 93–7 [19] Shin H, King C-C, Horiuchi T and Hu C 1991 Thin oxide charging current during plasma etching of aluminium IEEE Electron Device Lett. 12 404–6 [20] Shin H and Hu C 1992 Dependence of plasma-induced oxide charging current on Al antenna geometry IEEE Electron Device Lett. 13 600 [21] Shin H, Noguchi K, Qian X Y, Jha N, Hills G W and Hu C 1993 Spatial distribution of thin oxide charging in reactive ion etcher and MERIE etcher IEEE Electron Device Lett. 14 88 [22] Namura T, Uchida H, Okada H, Koshio A, Nakagawa S, Todokoro Y and Inoue M 1991 Wafer charging in different types of plasma etchers Proc. SPIE 1593 11–22 [23] Lukaszek W, Quek E and Dixon W 1992 CHARM2: towards an industry-standard wafer surface-charge monitor IEEE/SEMI Advanced Semiconductor Manufacturing Conf. pp 148–52 [24] Liang M, Chang C, Yeow Y, Hu C and Brodersen R 1984 MOSFET degradation due to stressing of thin oxide IEEE Trans. Electron Devices 31 1238–44 [25] Graves D and Surendra M 1991 Modeling and simulation of plasma processes IEDM Tech. Digest 887 [26] Garscadden A and Emeleus K G 1962 Notes on the effect of noise on Langmuir probe characteristics Proc. Phys. Soc. 79 535–41 [27] Gary A and Mathews G B 1931 A Treatise on Bessel Functions and their Applications to Physics (London: Macmillan) Thin gate oxide damage due to plasma processing [28] Schuegraf K F and Hu C 1993 Hole injection oxide breakdown model for very low voltage lifetime extrapolation Proc. IEEE Int. Reliability Physics Symp. pp 7–12 [29] Hung K K, Ko P K, Hu C and Cheng Y C 1990 A physical-based MOSFET noise model for circuit simulators IEEE Trans. Electron Devices 37 1323 [30] Hung K K, Ko P K, Hu C and Cheng Y C 1990 Random telegraph noise of deep-submicrometer MOSFETs IEEE Electron Device Lett. 11 90 [31] Moazzami R and Hu C 1990 Projecting gate oxide reliability and optimizing reliability screens IEEE Trans. Electron Devices 37 1643 [32] Krishnan S, Aur S, Wilhite G and Rajgopal R 1995 High density plasma etch induced damage to thin gate oxide IEDM Tec. Digest 315–18 [33] Namura T, Okada H, Naitoh Y, Todokoro Y and Inoue M 1991 Charge buildup in magnetized process plasma Japan. J. Appl. Phys. 30 1576–80 [34] Chen I C, Holland S and Hu C 1986 Oxide breakdown dependence on thickness and hole current-enhanced reliability of ultra thin oxide IEDM Tech. Digest 660 [35] Chen M, Leung C, Cochran W, Jain S, Hey H, Chew H and Dziuba C 1987 Hot carrier aging in two-level metal processing IEDM Tech. Digest 55 [36] Manos D and Flamm D 1988 Plasma Etching an Introduction (New York: Academic) [37] Gabriel C and Weling M 1993 Damage to thin gate oxide during LDD spacer oxide etching Am. Vac. Soc. National Symp. 473