www.rfconsult.com

PLLs and their application in wireless

communication systems

PLL synthesisers are part of almost any modern wireless communication device. While most of their

components are usually integrated in an IC, the designer can strongly influence the performance by the

design of the loop filter and the VCO.

This course enables engineers to understand the principles of PLL circuits and to design and

characterise PLL synthesizers optimized for a given application.

Particular attention is paid to practical issues, such as:

•

•

•

•

Loop filter design based on lock time and spurious requirements

Modulation concepts and their characteristics

The impact of phase noise on the system performance

Measurement of PLL parameters

The Course Schedule:

Day One

Control Loop Basics

•

•

•

•

Open and closed loop gain and transfer functions

Bode plot, phase margin, amplitude margin

Poles and zeros, characteristic function

Closed loop transfer function, bandwidth, dynamical

control behaviour

Stability

y(t)

Stable

−1 ⎛ G ( s ) ⎞

⎟ = const.

lim L ⎜

t →∞

⎝ s ⎠

−1

lim L (G ( s ) ) = 0

u(t)

t

G(s)

t →∞

t

y(t)

Unstable

PLL Components

•

•

•

•

•

t

VCOs

Phase noise in VCOs

Phase detector types

Charge pumps, speed-up

Dividers and Mixers in a PLL

www.rfconsult.com

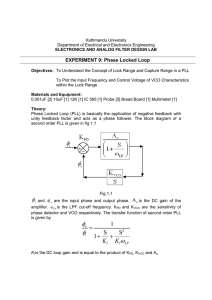

PLL Basics

Frequency step response

Δf

f Step

•

•

•

•

•

1.5

1.4

ζ = 0.5

ζ =1

1.2

1

Re f_out1N

Re f_out2N

Re f_out3N

ζ = 2

m

0.8

m

m

0.6

0.4

•

0.2

0

0

0

0

0.2

0.4

0.6

0.8

ωn

.t

2 .π m

1

1.2

1.4

1.5

The phase transfer function

Transfer functions for noise and spurious signals

Lock time, ωn, ξ and phase margin

Typical loop filters

Correlation between phase comparison frequency

and loop bandwidth requirement

Phase and frequency modulation of a PLL

ωn

⋅t

2π

www.rfconsult.com

www.rfconsult.com

www.rfconsult.com

Day Two

The PLL in a wireless system

•

•

•

Correlation between phase and frequency error and

SSB phase noise

Effect of the phase noise on blocking and adjacent

channel power performance

Sources of phase noise in a PLL and its simulation

Phase noise and blocking performance

S(f)

Interferer

ideal:

wanted

Signal

Interferer

IF

wanted

Signal

LO

f

S(f)

Interferer

with phase

noise:

The Integer-N-PLL in a wireless system

•

•

•

•

•

wanted

Signal

Loop filter calculation from lock time requirements

Trade-off between spurs, noise and lock time

Sources of PFD spurs

The use of charge pumps, charge pump issues

Problems linked to speed-up circuits

Interferer

wanted

Signal

LO

f

www.rfconsult.com

The Fractional-N-PLL in a wireless system

Fractional N PLL with analogue compensation

fRef

Phase

detector

+

Loop

filter

fOUT

VCO

1/N or 1/(N+1)

D/A

CLK

Increment K

Basics of operation

Spurs due to the fractional concept

Analogue and digital fractional compensation

Limits of fractional compensation circuits

The impact of phase detector linearity

A

AC

content

Accumulator

(Size F)

•

•

•

•

•

The direct digital synthesiser DDS

Overflow

www.rfconsult.com

•

•

Concept, advantages and limitations

System example: Combination with an integer-NPLL

Measurement of PLL parameters

•

•

•

•

•

•

Phase noise measurement with a spectrum analyser

Phase noise measurement by down conversion

Delayed self homodyne phase noise measurement

Simple lock time measurement

High precision lock time measurement

Measuring the PLL phase transfer function

High precision lock time measurement

LPF

DUT

Oscilloscope

Δφ

Common

reference

ftarget

www.rfconsult.com

The participants will be provided with an extensive set of lecture notes.

For more information please contact:

RF Consult GmbH

Am Gasteig 3

D-83737 Irschenberg

E-Mail: contact@rfconsult.com

Tel: +49 8025 99 5000

www.rfconsult.com

0

0