The abnormal electrostatic discharge of a no

advertisement

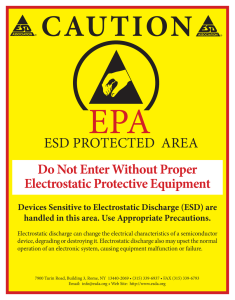

Vol. 34, No. 8 Journal of Semiconductors August 2013 The abnormal electrostatic discharge of a no-connect metal cover in a ceramic packaging device Li Song(李松) , Zeng Chuanbin(曾传滨), Luo Jiajun(罗家俊), and Han Zhengsheng(韩郑生) Institute of Microeletronics, Chinese Academy of Sciences, Beijing 100029, China Abstract: The human body model (HBM) stress of a no-connect metal cover is tested to obtain the characteristics of abnormal electrostatic discharge, including current waveforms and peak current under varied stress voltage and device failure voltage. A new discharge model called the “sparkover-induced model” is proposed based on the results. Then, failure mechanism analysis and model simulation are performed to prove that the transient peak current caused by a sparkover of low arc impedance will result in the devices’ premature damage when the potential difference between the no-connect metal cover and the chip exceeds the threshold voltage of sparkover. Key words: electrostatic discharge; human body model; no-connect metal cover; sparkover DOI: 10.1088/1674-4926/34/8/084007 PACC: 5280M 1. Introduction A ceramic package, usually made of aluminum oxide, is a kind of hermetic package used to achieve high reliability. Having excellent properties of high thermal conductivity, multilayer routing, high mechanical strength, and a small coefficient of thermal expansion, ceramic packaging technology has been applied to aerospace and military fieldsŒ1 . In the JEDEC standard of inspection criteria for microelectronic packages and coversŒ2 and MIL-STD-883HŒ3 , the specification for a metal cover only details the component’s appearance, such as nicks, pits, voids and scratches, instead of electric connection requirements. So some products, like those made by KYOCERA, use a ceramic package with a no-connect metal cover for reducing parasitic capacitance and ESD risk because of a metal cover’s large contact surface. While some other products, like those made by Honeywell, connect the cover to a ground pin. Whether the cover should be connected to ground pin or not has been a controversial issue in the domestic academic field. The concept of a no-connect cover comes from the noconnect pins mentioned in the ESDA/JEDEC Joint StandardŒ4 and MIL-STD-883H, which remain floating all the time and must not be stressed. However several research groups have studied how the HBM stress of no-connect pins affects the ESD immunity of a device in a real-world situation, and similar premature damage was found. Applying ESD pulse on the nonconnected (NC) balls of ball grid array (BGA) packaged integrated circuits (ICs) resulted in below HBM 2 kV but above HBM 3 kV without stressing the NC balls in Lo’s researchŒ5 . The researchers at Texas Instruments Inc. represented three failure cases all involving HBM stress of no-connect pins and then corrected the failure analysis about capacitive coupling causing premature damage proposed by Lo for an arc-over eventŒ6 , which agreed with the conclusion of the Atmel Corporation’s research group; particularly when analyzing the discharge procedure, peak current composition and sources for sparkoversŒ7 . Furthermore, all of these studies have found that the damaged pins and balls either were adjacent to stressed noconnect pins and balls or had traces neighboring the traces of stressed no-connect pins and balls, which is a different part from the HBM stress of a no-connect metal cover. This paper will demonstrate the HBM stress of a noconnect metal cover, which would cause similar failure and current waveforms to stressed no-connect pins. In addition, the failure mechanism is analyzed and stated to be related to a sparkover between the no-connect metal cover and the chip based on experiment details and results. Then a simulation of discharge process has been done to prove the failure analysis. Finally, a conclusion is made that the HBM stress of a noconnect metal cover will cause a sparkover leading to devastatingly large current and premature damage so therefore a noconnect metal cover should be connected to a ground pin. 2. Experiment and results To obtain a universal conclusion, different kinds of devices in the form of a CDIP with a no-connect metal cover have been used. A device using a ceramic dual-in-line package (CDIP) mainly consists of a ceramic substrate, a chip, and a cover, as shown in Fig. 1. Also, all samples, including Sample 1 (14 pins), Sample 2 (16 pins) and Sample 3 (20 pins), were fabricated with a 2.0 m PDSOI process developed by the Institute of Microelectronics of the Chinese Academy of Sciences (IMECAS). Two groups of HBM ESD test have been carried out, which were Condition 1: stressing on pin combinations requested by ESDA/JEDEC Joint Standard and Condition 2: stressing on a no-connect metal cover while the ground pin is grounded. When the no-connect cover was zapped by a positive HBM pulse with a short wire linking the cover to one terminal of the ESD tester, the device’s ground pin was connected to another terminal through a CT2 current probe to capture the discharge current waveform by a 1 GHz bandwidth oscilloscope. Note, all pins except the ground pin are kept floating in Condition 2. * Project supported by the National Natural Science Foundation of China (No. 60927006). † Corresponding author. Email: lisong@ime.ac.cn Received 7 January 2013, revised manuscript received 22 March 2013 084007-1 © 2013 Chinese Institute of Electronics J. Semicond. 2013, 34(8) Li Song et al. Fig. 1. A device using a CDIP with 20 pins and a no-connect metal cover. Table 1. Partial test results. Parameter Sample 1 Sample 2 Ccover (pF) 6.80 7.04 Failure voltage of 5 5.5 Condition 1 (kV) Failure pins of 1, 2, 7, 14 7, 8, 9, 16 Condition 1 Failure voltage of 3.5/3.6 2.9/3.0 Condition 2 (kV) Failure pins of 1, 2, 8, 9/9 12/4, 14 Condition 2 Ipeak of Condition 10.87/11.23 9.88/10.20 2 (A) Sample 3 8.24 4.5 1 2.5/2.7 4/7, 11 8.00/8.72 Fig. 2. Current waveforms with varied HBM stress on the no-connect metal cover. Condition 1: stressing on pin combinations; Condition 2: stressing on no-connect cover. (Note: some data are separated because more than one sample was tested.) IC tests were executed both before and after stressing to make sure that the chosen samples could work properly and be used to estimate accurate failure voltage as well as failure pins. In addition, the parasitic capacitance Ccover between the cover and the ground pin was measured by an LCR meter and recorded for failure analysis. Ccover , failure voltage, failure pins and peak current Ipeak when damaged are listed in Table 1. Also, Figure 2 shows some current waveforms when the noconnect metal cover of Sample 1 was stressed with an HBM pulse of varied voltage. A few observations could be made from Table 1 and Fig. 2. (1) There was a peak current of approximately 8–10 A accompanying the abnormal electrostatic discharge, which would be able to cause device failure. (2) The device in Condition 2 presented a much lower failure voltage than Condition 1 as the papers give similar premature damage. (3) The value of Ipeak rose with increasing HBM pulse voltage, namely the applied stress level. (4) The failure pins of Condition 2 not only differed from those of Condition1, but also varied among devices of the same type. (5) There was a threshold voltage for Condition 2. For example, it was not until an HBM pulse of 2.5 kV was zapped on the cover that the current waveform was captured for Sample 1, likewise 2.7 kV for Sample 2 and 2.5 kV for Sample 3. 3. Failure mechanism and simulation Although an HBM pulse was applied in Condition 2, the captured discharge current waveform is clearly different from the standard HBM current waveform defined in the ESDA/JEDEC Joint StandardŒ4 . The premature damage indicates that a new ESD failure mechanism, rather than HBM, must have happened. In some papers, the captured current waveform was described like a human metal model (HMM)Œ8 under real circumstances without a tester effect. However IEC 61000-4-2Œ9 relating to a real HBM, namely an HMM, targets system level tests not IC level ones and is not supposed to apply to this particular case. A sparkover has been proven by monitoring light emission with emission microscopy (EMMI)Œ6 when zapping an HBM pulse on a no-connect pin, which was the most possible cause of this abnormal electrostatic discharge when stressing a noconnect cover. Also, it was the large capacitance of the tester’s discharge wire and test board that determined the rise time and full width at half height instead of the small Ccover . This could explain why the rise time and full width at half height of waveform barely changed even when stressing devices with varied Ccover and dimensions shown in Fig. 3. Also, Sample 4 using CDIP and Sample 5 using flat package (FP) have been added to the experiment for further investigation. In order to exhibit the procedure of this abnormal electro- 084007-2 J. Semicond. 2013, 34(8) Li Song et al. Fig. 3. Peak current through devices with varied Ccover and dimensions when stressed with a 3 kV HBM pulse. (The first spike was zoomed in for waveform details.) Fig. 5. Simulation compared to the captured current waveform when stressed by a 3 kV HBM pulse. analysis above are correct. In addition, current monitors at Ccover and Rarc in simulation record a current waveform in Fig. 6 that is different from the oscilloscope, which captures the current outside the sample. Since Rarc is the only current path, there is a third current individual inside the sample which cannot be measured by the test method in this paper. Furthermore, this third current individual is clearly formed by discharge of Ccover and identified as the charged device model (CDM)Œ10; 11 , judging by the current waveform in Fig. 6. 4. Discussion Fig. 4. “Sparkover-induced model” for failure analysis and simulation. static discharge, a model is demonstrated in Fig. 4. The first 100 pF capacitor is charged to trigger an HBM pulse. When relay switch S is closed, charge in the 100 pF capacitor transfers to the capacitance Cout of the open-circuit device under test (DUT) comprised of a discharge wire and test board, which leads to a rise of voltage VDUT at the no-connect cover. If VDUT reaches the threshold voltage, a sparkover happens from the cover to the chip where Ccover and arc impedance Rarc form the current path. The current displayed in the oscilloscope contains two individuals: one is regular HBM current formed by 100 pF capacitor and 1.5 k human body resistance; the other is formed by CDUT and low Rarc . As a result, a transient peak current 8–10 A higher than initial HBM current flows through the chip, which may be designed to be resistant only to 2 A HBM current (3 kV HBM) at most, leading to premature damage. Because of the relatively large area of cover and chip, the sparkover point can be anywhere in ICs, such as IOs, core circuits, and power/ground rings, meaning the peak current randomly destroys any part of ICs, which was confirmed by the above experimental results. At this point, we can call this model the “sparkover-induced model”. Based on the proposed model, a simulation carried out by advanced design system software has been done to determine its accuracy. The results of simulation and zapping a 3 kV HBM pulse on the cover of Sample 1 are compared in Fig. 5, in which two almost overlapped curves prove that the model and failure The proposed “sparkover-induced model” has explained the procedure of this abnormal electrostatic discharge by simulation whereas HBM or HMM cannot. Despite that, this abnormal electrostatic discharge in experiment is a tester effect, what is certain is that a no-connect metal cover still suffers a severe ESD risk in real situations, including not only through touching the cover but also by manufacture and transport because a sparkover will be triggered to destroy ICs once the potential difference between a no-connect metal cover and chip exceeds the threshold voltage. For instance, friction of devices in packing bag can cause quite a high potential difference between a no-connect metal cover and a chip, leading to sparkover inside devices. A few more discussions are as follows. First, an extra inductance Lgnd is added at the ground interface of the proposed model in Fig. 4 because the waveform captured by the oscilloscope contains a reflected part with a 180 degree phase shift due to impedance mismatch, which explains the oscillating waveform shapeŒ12 . Secondly, a small spike circled by a dashed line in Fig. 2 indicates the charge redistribution. There is a time interval between this spike and the current peak, which decreases when the stress voltage rises. This time interval is the time before VDUT reaches the threshold voltage. Thirdly, stressed by 3 kV HBM pulse, devices of different dimensions in Fig. 3 indicate different Ipeak influenced by Ccover . James Karp, et al. discovered that Ccover and Ccover per chip area affect critically the CDM test result while stressing 084007-3 J. Semicond. 2013, 34(8) Li Song et al. Fig. 7. The trend of Ipeak versus. a ground plane can be placed inside the package to connect both ground pins and the metal cover, which is highly recommended for consideration of parasitic resistance and voltage drop. Another way, which is mostly used for photoelectric devices to avoid this abnormal electrostatic discharge, is to use an insulating material like glass for the cover so that destructive sparkover will not occur between the cover and the chip. Furthermore, an inference can be made that any no-connect metal component, such as a cover and a pin, close to circuits or traces of them in a package is likely to cause sparkover, leading to device damage and should be removed or connected to circuits properly during package design. This applies not only to the ceramic package discussed in this paper, but also other package types like metallic packages and plastic packages. Finally the electric connection requirement of the package, especially the no-connect metal component, needs to be paid more attention from the perspective of ESD protection and added to relevant standard specifications. Fig. 6. Current through (a) Ccover and (b) Rarc in simulation. Table 2. Test results and chip area of all tested samples. Parameter Ipeak Ccover A Ccover =A (A) (pF) (mm2 / (pF/mm2 / Sample 1 9.73 6.80 2.17 1.67 1.876 Sample 3 9.04 8.24 2.6 2.07 1.533 Sample 4 3.66 8.70 7.15 14.9 0.082 Sample 5 7.4 5.08 2.2 1.76 1.312 5. Conclusion Peak current was measured when stressed with 3 kV HBM pulse. on each pin excluding lid separated from chip by thermal interface material (TIM)Œ13 . By analyzing the data in Table 2, this trend in Fig. 7 demonstrates the following discipline in which A represents chip area. Ipeak / Ccover : A (1) For further explanation, Ccover represents the gap between A cover and chip which is arc length and determines the value of Rarc . The research in this paper has clearly answered the controversial question of whether a metal cover should be connected to a ground pin or not. The metal cover should be connected to a ground pin rather than a power pin or any IO pins because non-zero voltage at a cover would raise parasitic capacitance and probably cause an electromagnetic compatibility (EMC) problem during normal use. In case of multiple ground pins, all the ground pins should be connected to a metal cover, or An abnormal electrostatic discharge accompanied with higher current than HBM was observed when a no-connect metal cover in a ceramic packaging device was stressed with an HBM pulse, resulting in similar premature damage as found in a no-connect pin case. A sparkover contributes to this abnormal electrostatic discharge because charge redistribution between a 100 pF capacitor and Cout raises VDUT to the threshold voltage of sparkover, leading to two current individuals: an HBM current formed by 100 pF capacitor and 1.5 k human body resistance, and current overshoot formed by CDUT and low arc impedance. This transient high current can easily destroy any part of ICs for the indeterminacy of the sparkover point. Furthermore, a strong dependence of Ipeak with stress voltage and Ccover per chip area was found from experimental results. A simulation based on the proposed “sparkover-induced model” fits the captured waveform perfectly and implies the existence of a third current individual inside the sample. Despite it being a tester effect, this abnormal electrostatic discharge can also happen in real situations once the poten- 084007-4 J. Semicond. 2013, 34(8) Li Song et al. tial difference between a no-connect metal cover and a chip exceeds the threshold voltage of sparkover when, for example, a human body with static electricity touches a no-connect metal cover. It is highly recommended that metal covers should be connected to the ground plane in package design and any no-connect metal component with sparkover risk should be removed or connected to circuits properly in all kinds of packaging for ESD protection. References [1] Fang R, Wang J, Huang L, et al. The development of electronic packaging. Science & Technology Association Forum, 2012, (2): 84 [2] Inspection criteria for microelectronic packages and covers. JEDEC Solid State Technology Association, May 2011 [3] MIL-STD-883H. Departments and Agencies of the Department of Defense, February 2010 [4] ESDA/JEDEC joint standard for electrostatic discharge sensitivity testing-human body model (HBM)-component level. ESD Association & JEDEC Solid State Technology Association, November 2011 [5] Wen Y L, Ming D K. Abnormal ESD failure mechanism in high-pin-count BGA packaged ICs due to stressing nonconnected balls. IEEE Trans Device Mater Reliab, 2004, 4(1): 24 [6] Kunz H, Duvvury C, Brodsky J, et al. HBM stress of no-connect IC pins and subsequent arc-over events that lead to human-metaldischarge-like events into unstressed neighbor pins. Electrical Overstress/Electrostatic Discharge Symposium, 2006 [7] Kaschani K T, Schimon M, Hofmann M, et al. ESD damage due to HBM stressing of non-connected pins. Electrical Overstress/Electrostatic Discharge Symposium, 2006 [8] ESD association technical report for the protection of electrostatic discharge susceptible items–human metal model (HMM). Electrostatic Discharge Association, 2009 [9] IEC 61000-4-2: electromagnetic compatibility(emc)–part 4-2: testing and measurement techniques–electrostatic discharge immunity test. IEC International Standard, 2008 [10] Field-induced charged-device model test method for electrostatic-discharge-withstand thresholds of microelectronic components. JEDEC Solid State Technology Association, December 2009 [11] ESD association standard for electrostatic discharge sensitivity testing–charged device model (CDM)–component level. Electrostatic Discharge Association, July 2009 [12] Muhonen K, Peachey N, Testin A. Human metal model (HMM) testing, challenges to using ESD guns. Electrical Overstress/Electrostatic Discharge Symposium, 2009 [13] Karp J, Kireev V, Tsaggaris D, et al. Effect of flip-chip package parameters on CDM discharge. Electrical Overstress/Electrostatic Discharge Symposium, 2008 084007-5