E524.03 Features Applications General Description Ordering

advertisement

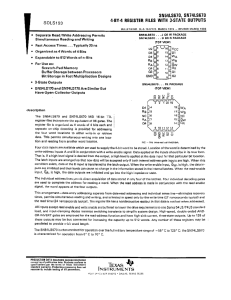

E524.03 3-WIRE ULTRASONIC TRANSCEIVER DRIVER AND SIGNAL PROCESSOR PRELIMINARY INFORMATION - AUG 01, 2011 Features General Description ÿ High sensitivity, low noise signal acquisition (0.5µVRMS) ÿ Driver power and signal gain programmable ÿ Supports transducer frequencies from 48kHz to 58kHz ÿ Fully digital signal evaluation reduces external components ÿ 12 programmable threshold/time settings for echo evaluation ÿ One wire interface for echo signal output and programming ÿ Automotive protection up to +40V (supply, IO) ÿ AEC-Q100 qualification This IC implements ultrasonic range detection with a single transceiver. A transmitter channel provides programmable power and frequency to a center tapped transformer. The receiver channel amplifies the µV echo signal and feeds it to an analog-to-digital converter. Subsequent digital filtering achieves excellent tracking stet the sending frequency without external components or trimming. The result is the echo envelope signal. Oscillator frequency, amplifier gain and transmitted power can be adjusted and stored in an embedded E2PROM via a single wire IO pin. Furthermore 12 programmable threshold/time settings are available to evaluate the echo envelope signal at the IO pin. Applications Ordering Information ÿ Ultrasonic Park Assist (USPA) ÿ Industrial Distance Measuring ÿ Robotics Product ID Temp. Range Package E524.03 -40°C to +85°C QFN20L5 US-Transducer Bumper module CTD1 RTD1 RAIN CAIN DRV1 RP RSUP DSUP CSUP1 CSUP2 DRV2 AING AINS VSUP VDDD CVDDD Body Control Unit E524.03 RIO_PU RIO_S CI CIO1 TDO IO TCK TDI CIO2 TMS VDDA GNDA GNDD GNDP TMEN CVDDA This document contains information on a pre-production product. ELMOS Semiconductor AG reserves the right to change specifications and information herein without notice. ELMOS Semiconductor AG Data Sheet 1/34 QM-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 Description Serial resistor in supply line Reverse polarity protection diode Blocking capacitor for supply line Blocking capacitor for supply line Filter resistor for transducer tank Tank capacitor for transducer Clamping zener diode to protect DRV1,2 voltages to exceed 40V 1) Serial resistor for IO line Pull up resistor for IO line Capacitor for IO line Capacitor for IO line Filter capacitor for transducer signal Condition Symbol RSUP Min 13 DSUP >250mW pay attention to voltage range Filter resistor for pay transducer signal attention to power dissipation AC coupling pay capacitor for attention to transducer signal voltage range Blocking capacitor for analog supply Blocking capacitor for digital supply Transducer resonance resistor Transducer resonance capacitor Typ 15 Max 17 e.g. BAS321 Unit Ohm - CSUP1 1.5 2.2 2.9 nF CSUP2 150 220 300 nF RSUP_TD 73 82 91 Ohm CSUP_TD 70 100 10 uF ZD_TD - e.g.25 - V RIO_S 0.9 1 1.1 kOhm RIO_PU 9 10 11 kOhm CIO1 230 330 430 pF CIO2 1.5 2.2 2.9 nF CAIN1 7 10 13 pF RAIN 90 100 110 Ohm CAIN2 325 470 620 pF CVDDA 70 100 130 nF CVDDD 70 100 130 nF RTD adjust to transducer CTD adjust to transducer Table 1: device values 1) please see also Fig. 5.2-1 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 2 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 1 Package and Pinout 1.1 No 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 Pin Description Name nc AINS AING GNDA VDDA DRV1 GNDP DRV2 nc IO VSUP VDDD GNDD TDO TDI TCK nc nc TMS TMEN EDP Type Description not connected to device, should be connected to PCB-GND, as shield Positive signal input Negative signal input Analog ground Internal analog supply voltage Driver output 1 Power ground for driver and IO-Interface Driver output 2 not connected to device, should be connected to PCB-GND, as shield Bidirectional interface Supply Voltage Internal digital supply voltage Digital ground JTAG data output JTAG data input JTAG clock not connected to device, should be connected to PCB-GND not connected to device, should be connected to PCB-GND JTAG select Test mode enable exposed die pad, has to be connected to PCB-GND Table 1.1-1: Pin Description Explanation of Types: A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage 1.2 Package Reference The device is assembled in a QFN20L4 package according to JEDEC standard MO-220, Issue K, as of June 2006. The referenced JEDEC variant is VGGD-5. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 3 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 20 19 18 17 16 TMS nc nc TCK Package Pinout TMEN 1.3 21 EDP 1 nc TDI 15 VDDD 12 5 VDDA VSUP 11 IO 4 GNDA nc GNDD 13 DRV2 3 AING GNDP TDO 14 DRV1 2 AINS 6 7 8 9 10 Fig. 1.3-1: Package Pinout for QFN20L4 (top view) This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 4 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 2 Block Diagram DRV1 DRV2 AINS AING VSUP VDDA SUPPLY BIAS Transducer Driver DIGITAL Filter COMP THRESn AMP_GAIN[3:0] DRV_CUR[3:0] Receiver INC_BW VDDD A D C AMP EEPROM Oscillator CONTROL IO_INTERFACE JTAG_INTERFACE TCK TDI TDO TMS GNDA GNDD GNDP IO TMEN Fig. 2-1: Block Diagram This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 5 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 3 Operating Conditions 3.1 • • • Absolute Maximum Ratings Operating the device at or beyond these limits may cause permanent damage. All voltages are referred to ground (0V). Currents flowing into the circuit have positive values. No. 1 2 3 4 5 6 Description Supply Voltage Supply Voltage Voltage at pin IO Voltage at pin IO Voltage at digital pins (TCK, TDO, TDI, TMS, VDDD) Condition t < 500 ms t < 500 ms Symbol VSUP VSUP VIO VIO VD Voltage at analog pins (AINS, AING, VDDA) VTMEN VDRV PTOT RT,J-A Max Unit 30 V 40 V 30 V 40 V 3.6, V VDDD +0.3 -0.3 3.6, V VDDA +0.3 -0.3 3.6 V -0.3 40 V 1.5 W 24 K/W TAMB TJ TSTG -40 -40 - 55 VA 7 8 9 10 Voltage at pin TMEN Voltage at pins DRV1 and DRV2 Power Dissipation Thermal Resistance Junction to Ambient 11 Ambient temperature 12 Junction Temperature 13 Storage Temperature TAMB <=85°C Min -0.3 -0.3 -0.3 -0.3 -0.3 125 125 125 °C °C °C Table 3.1-1: Maximum Ratings 3.2 • • • • Recommended Operating Conditions Parameters are guaranteed within the range of recommended operating conditions unless otherwise specified. All voltages are referred to ground (0V). Currents flowing into the circuit have positive values. The first electrical potential connected to the IC must be GNDA. (If not specified specify timing sequence of electrical contacts.) No. Description 1 Supply Voltage 2 Programming voltage for EEPROM at pin IO 3 DC Input Voltage 4 Input Current 5 Operating Temperature Range Condition Symbol VSUP VPROG Min 7 23 AINS/AING AINS/AING TOPR -0.3 -20 -40 Typ 25 Max 18 27 Unit V V 0.3 20 +85 V mA °C Table 3.2-1: Recommended Operating Conditions This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 6 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 4 Detailed Electrical Specification 4.1 Supply and Bias No. Description 1 Current consumption out of VSUP 2 internal analog supply Condition external CVDDA connected external CVDDD connected 3 internal digital supply 4 current out of VDDA in case of short to GND current out of VDDD in case of short to GND 5 Symbol IVSUP Min Typ 7 Max Unit mA VDDA 3.0 3.3 3.6 V VDDD 3.0 3.3 3.6 V IVDDA,SHORT -30 mA IVDDD,SHORT -75 mA Table 4.1-1: DC Parameters 4.2 No. 1 2 3 4 5 6 Transducer Driver Description Condition Clamping voltage IDRV = 500μA Leakage current of DRVn pad VDRV1,2 = 0V, 12V Current adjustment steps Adjustment step size Minimum current adjustment DRV_CUR[3:0]=' 0000' Maximum current adjustment DRV_CUR[3:0]=' 1111' Symbol VDRV,CLAMP ILEAK,DRV NIDRV STEPIDRV IDRVmin Min 40 Typ Max 100 IDRVmax Unit V nA 15 13.5 108 mA mA 310 mA Table 4.2-1: DC Parameter No. Description 1 Driver output frequency 2 3 4 Step width of frequency adjustment temp coefficient of driver output frequency Factory adjusted frequency of Driver output Condition to be adjusted by F_DRV_ADJ[6:0] Temperature=30 °C Symbol fDRV Min 40 Typ Max 58 Unit kHz LSBf_OSC 300 Hz TCf_DRV -400 ppm/K fDRV,ADJ tbd 48.00 tbd kHz Table 4.2-2: AC parameter This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 7 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 4.3 4.3.1 No. 1 2 3 4 5 6 7 Receiver Amplifier Description Minimum gain Maximum gain Step size Number of steps Gain reduction Input Impedance AINS to GNDA AING to GNDA Noise Level Condition @ fDRV=52 kHz @ fDRV=52 kHz @ fDRV=52 kHz Symbol GMIN GMAX ΔGC NG GRED RIN @ fDRV=52 kHz @ fDRV=52 kHz NP) Min 63 78 0.5 10.5 eN Typ 67 82 1.0 15 12 100 Max 71 86 1.5 Unit dB dB dB 13.5 dB kΩ 7.3 nV/ Table 4.3.1-1: Electrical Parameter table 4.3.2 Digital filter No. Description 1 Center frequency 2 -3dB-Bandwidth 3 -3dB-Bandwidth 4 -3dB-Bandwidth 5 -3dB-Bandwidth Condition number of bursts=8 FILTADJUST=0 number of bursts=8 FILTADJUST=0 number of bursts=8 FILTADJUST=0 number of bursts=8 FILTADJUST=0 Symbol fc,filt BW,DFILT8,0 Min Typ Max 1 0.2191 Unit fDRV fDRV BW,DFILT8,1 0.1058 fDRV BW,DFILT16,0 0.1058 fDRV BW,DFILT16,1 0.0520 fDRV Table 4.3.2-1: Electrical Parameters 4.3.3 Comparator No. Description Condition 1 Time, the comparator output is bit masked COMP_MASK=1 Symbol TCMASK Min - Typ 16 Max - Unit 1/fDRV Table 4.3.3-1: Electrical Parameter, comparator This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 8 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 4.4 IO Interface No. Description Condition 1 Voltage threshold for pin IO to detect low input signal 2 Voltage threshold for pin IO to detect high input signal 3 Voltage at pin IO to output low IOUT = 4mA level 4 current limitation for pin IO VOUT < 18V Symbol VIO_IL Min 0.29 Typ 0.33 Max 0.36 Unit VSUP VIO_IH 0.62 0.67 0.70 VSUP VIO_OL 0.5 V IIO_SHORT 60 mA Table 4.4-1: DC Parameters No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Description Slew Rate Input debouncer IO low phase for send request IO low phase for receive request IO low phase to enter command mode IO low phase to enter programming command mode IO high phase after TCMD and TCMD_PROG Setup time for VPROG Programming time Bit length, ECU to bumper module IO low phase for a logical '0', ECU to bumper module IO low phase for a logical '1', ECU to bumper module Bit length, bumper module to ECU IO low phase for a logical '0', bumper module to ECU IO low phase for a logical '1', bumper module to ECU pulse width low frequency calibration pulse Condition Symbol SRVIO TDEB TSND TREC Min 0 4.5 9 Typ 1.7 6 12 Max Unit V/µs 1 1/fDRV 8.92 1/fDRV 14.92 1/fDRV TCMD 15 18 20.92 1/fDRV TCMD_PROG 15 18 20.92 1/fDRV TD 1.08 3 4.42 1/fDRV TVPROG TPROG TBIT_WR 5 9 20 12 ms ms 14.92 1/fDRV TBIT0_WR 4.5 6 8.92 1/fDRV TBIT1_WR 1.08 3 4.42 1/fDRV TBIT 12 1/fDRV TBIT0 6 1/fDRV TBIT1 3 1/fDRV TCAL 12 1/fDRV Table 4.4-2: AC Parameters For fDRV = 58 kHz, 3*1/fDRV=52.72us This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 9 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 4.5 JTAG Interface for lab analysis No. Description Condition 1 Input high voltage at pins: TCK, TDI, TMS 2 Input low voltage at pins: TCK, TDI, TMS 3 Output high voltage at pin TDO IOH,TDO=-2mA 4 Output low voltage at pin TDO IOL,TDO=2mA Symbol VIH Min 2.6 VIL VOH VOL Typ Max Unit V 0.7 V 0.4 V V 2.4 Table 4.5-1: DC Parameters This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 10 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5 Functional Description 5.1 Supply and Bias Bumper module E524.03 VDDD regulator VDDD CVDDD GNDD VDDA regulator GND VDDA C VDDA GNDA BIAS generator GND Supply and Bias Fig. 5.1-1: block diagram of supply and bias Functions of this block are: • generation of chip internal analog supply • generation of chip internal digital part • generation of references and bias currents for chip internal use Both, the analoge supply VDDA as well as the digital supply VDDD, require external blocking capacitors CVDDA and CVDDD. It is recommended to place the external capacitors as close as possible to the related pins VDDx and GNDx. VDDA and VDDD are not intended to supply any external components. In case VDDA or VDDD are shorted to GND, the output current will be limited to I VDDA,SHORT respectively IVDDD,SHORT. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 11 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.2 Transducer Driver The center tap of the transformer is connected to the VSUP-pin. When the transducer driver is activated by the 'SEND REQUEST' command, the pins DRV1 and DRV2 are tied towards ground by internalswitches alternately with the driver output frequency f DRV. The current through the transformer and thus the transducer power is controlled by an internal current source. The number of output periods is defined by the measurement configuration and can be set to 8 or 16. The driver current IDRV is set by bits DRV_CUR[3:0]. The relation between the driver current IDRV and the bits DRV_CUR[3:0] is given by the following formula: The frequency fDRV can be adjusted by EEPROM bits F_DRV_ADJ[6:0]. The guaranteed adjustment range is defined by fOSC,MIN and fOSC,MAX. The typical stepwidth is defined as LSBf_OSC,typ. The frequency is strictly monotonic increasing with increasing value of F_DRV_ADJ[6:0]. Before delivery the frequency is adjusted to fOSC,ADJ. The setting F_DRV_ADJ[6:0]=0 corresponds to the minimum frequency that might be much lower than fOSC,MIN. The procedure for adjusting the frequency should be as following: 1. 2. 3. 4. 5. 6. 7. Read the actual value of F_DRV_ADJ[6:0] measure the actual frequency calculate the difference fDIFF=target frequency-actual frequency calculate the rough number n of steps corresponding to fDIFF by n=fDIFF/LSBf_OSC,typ adjust F_DRV_ADJ[6:0] by n repeat until the target frequency is reached store the setting for F_DRV_ADJ[6:0] by EE-Programming command (EE-write impacts only the output of the Driver Frequency Calibration command, for all other frequency related functions (e.g. driver output frequency, communication timing), the new setting of F_DRV_ADJ[6:0] will be activated after EE-Programming command only) Remark: The timing for communication is based on f DRV, thus activating another fDRV by EEProgramming changes the timing for communication. MISSING REFERENCE shows the simplified signal curves at pins DRV1 and DRV2 before and during transmission. When driving the transducer, the voltages at pins DRV1 and DRV2 exceed the supply voltage VSUP. Thus activating the transducer (by sending the 'SEND REQUEST' command) at supply voltages close to the absolute maximum rating of VSUP might harm the IC. One proposed countermeasure is the use of a clamping zener diode ZD_TD. Voltage at pin DRV1 voltage Voltage at pin DRV2 VSUP time 1/fDRV start of transmission Fig. 5.2-1: Simplified signal curves at pins DRV1 and DRV2 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 12 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.3 Receiver AINS A D C AMP AING DIGITAL Filter signal line COMP THRESn INC_BW AMP_GAIN[3:0] Receiver EEPROM CONTROL Fig. 5.3-1: Block diagram of Receiving Path 5.3.1 Amplifier The gain of the amplifier can be programmed by the bits AMP_GAIN[3:0]. The total gain can be calculated using the following formula: To improve the performance for detecting objects in short distances, the gain can be reduced by setting bit GRED during measurement configuration. Activating the gain reduction reduces GAIN by value G RED. The input of the amplifier is designed differentially to minimize pickup of unwanted signals. AINS should be used as signal input AING as signal ground. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 13 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.3.2 Digital filter The output of the digital filter corresponds to the envelope of the rectified signal. The digital representations of the echo and threshold signals can be watched over the JTAG-interface. One digit of the 10bit values corresponds to: The characteristic of the digital filter depends on: • the number of transmitted burst pulses defined by 'measurement configuration' • the programmed filter adjustment by bit FILTADJUST The filter bandwidth according to the number of bursts and bit FILTADJUST is shown in Table 5.3.2-1. number of burst pulses 8 8 16 16 bit FILTADJUST 0 1 0 1 bandwidth BW,DFILT8,0 BW,DFILT8,1 BW,DFILT16,0 BW,DFILT16,1 Table 5.3.2-1: Bandwidth of digital filter depending on configuration Fig. 5.3.2-1: Filter characteristic, number of bursts=8 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 14 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 Fig. 5.3.2-2: filter characteristic, number of bursts=16 5.3.3 Comparator This digitally realized block compares the output of the digital filter to a threshold provided by registers of the control unit. Depending on the ICs operating mode and configuration, there is a rich offer for threshold programming. The output of the comparator is passed to the control unit. 5.3.3.1 functionality in SEND and RECEIVE mode SEND or RECEIVE mode is entered with the rising edge of the corresponding command (end of T SND or TREC). In SEND and RECEIVE mode, a filter output signal exceeding the comparator threshold, indicates a received echo. The threshold passed to the comparator in SEND and RECEIVE mode is a function of time. This function is defined by: • an initial value • up to 14 threshold values which are connected by linear interpolation • an additional offset • a scaling factor As long as the IC operates in SEND or RECEIVE mode, no instructions coming over the IO-Interface are accepted. The interface is ready to receive new instructions, when a high level remains at pin IO for at least TDEB after the SEND or RECEIVE mode is exited. The IC offers several programmable opportunities for individual configuration of the threshold function: This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 15 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 INTERVAL LENGTH, bit THRES_LEN The time, the IC operates in SEND or RECEIVE mode is divided into up to 15 intervals. The duration of these intervals is selected by bit THRES_LEN. Additionally the offset value of the threshold function is effected by this bit. THRES_LEN 0 1 function short intervals selected, threshold offset set to high value=62 long intervals selected, threshold offset set to low value=31 range short range long range Table 5.3.3.1-1: function of bit THRES_LEN Further on, the intervals depend linearly on the selected transducer frequency f DRV. The programmable threshold values THRES1 - THRES14 are reached at the end of the corresponding interval. During the interval the threshold is evaluated by a linear interpolation with the end value of the previous interval. The initial value is valid for complete interval 0. Table 5.3.3.1-2 shows the intervals for two different frequencies in dependence on bit THRES_LEN and gives the corresponding register THRESn to program the exponent of the threshold value. Interval name 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 threshold exponent initial THRES1 THRES2 THRES3 THRES4 THRES5 THRES6 THRES7 THRES8 THRES9 THRES10 THRES11 THRES12 THRES13 THRES14 Interval [ms] Interval [ms] Interval [ms] Interval [ms] short range fDRV=48kHz 0 - 2.0 2.0 -3.0 3.0 - 4.0 4.0 - 5.0 5.0 - 6.0 6.0 - 7.0 7.0 - 8.0 8.0 - 9.0 9.0 - 10.0 10.0 - 11.0 11.0 - 12.0 12.0 - 13.0 13.0 - 14.0 14.0 - 15.0 15.0 - 18.0 short range fDRV=58kHz 0 - 1.66 1.66 - 2.48 2.48 - 3.31 3.31 - 4.14 4.14 - 4.97 4.97 - 5.79 5.79 - 6.62 6.62 - 7.45 7.45 - 8.28 8.28 - 9.10 9.10 - 9.93 9.93 - 10.76 10.76 - 11.59 11.59 - 12.41 12.41 - 14.90 long range fDRV=48kHz 0 - 2.0 2.0 - 4.0 4.0 - 6.0 6.0 - 8.0 8.0 - 10.0 10.0 - 12.0 12.0 - 14.0 14.0 - 16.0 16.0 - 18.0 18.0 - 21.0 21.0 - 24.0 24.0 - 27.0 27.0 - 30.0 30.0 - 33.0 33.0 - 36.0 long range fDRV=58kHz 0 - 1.66 1.66 - 3.31 3.31 - 4.97 4.97 - 6.62 6.62 - 8.28 8.28 - 9.93 9.93 - 11.59 11.59 - 13.24 13.24 - 14.90 14.90 - 17.38 17.38 - 19.86 19.86 - 22.34 22.34 - 24.83 24.83 - 27.31 27.31 - 29.79 Table 5.3.3.1-2: Intervals depending on selected range and FDRV Threshold values, initial and THRES1 - THRES14 The threshold values resulting from the programmed exponent THRESn can be calculated by following formula: Table 5.3.3.1-3 shows the resulting threshold values depending on the programming of THRESn and the corresponding voltage. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 16 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 threshold exponent 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 threshold value without offset and scaling 0 5 10 15 21 28 35 42 50 59 68 78 89 101 113 127 141 157 174 192 212 233 256 280 307 335 366 399 434 472 514 558 typical voltage [mV] 0 8.1 16.1 24.2 33.9 45.2 56.5 67.7 80.6 95.2 109.7 125.8 143.5 162.9 182.3 204.8 227.4 253.2 280.6 309.7 341.9 375.8 412.9 451.6 495.2 540.3 590.3 643.5 700.0 761.3 829.0 900.0 Table 5.3.3.1-3: Threshold values resulting from exponent and typical voltage INITIAL VALUE, bit THRES_INI In SEND mode the initial threshold exponent is always set to maximum value of 31. In RECEIVE mode the initial threshold exponent is defined by bit THRES_INI. THRES_INI 0 1 function in receive mode initial threshold exponent=31 initial threshold exponent=THRES1 Table 5.3.3.1-4: function of bit THRES_INI This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 17 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 End of SEND and RECEIVE mode, THRES7 - THRES14 If short range is selected, SEND and RECEIVE mode end after interval 14. If long range is selected SEND and RECEIVE mode end earliest after interval 7 and latest after the 14th interval, depending on the programmed values THRES7-THRES14. If value THRESn, for n =8-14, is set to maximum value and higher than the previous value THRES(n1), SEND and RECEIVE mode ends after interval n-1, else after interval 14. Example for long range: THRES11=6 THRES12=31 (maximum value) -> SEND or RECEIVE mode ends after interval 11. SCALING in RECEIVE mode, bits THRES_SCALE[1:0] In RECEIVE mode the threshold sensitivity can be increased by a scaling factor. All threshold values defined by THRES1 - THRES14 are multiplied with this scaling factor. The scaling factor is set by bits THRES_SCALE[1:0] according to Table 5.3.3.1-5. THRES_SCALE[1] 0 0 1 1 THRES_SCALE[0] 0 1 0 1 SCALING_FACTOR 0.25 0.5 0.75 1.0 Table 5.3.3.1-5: Scaling for Receive Threshold REMARK: the SCALING_FACTOR in SEND mode cannot be modified, SCALING_FACTOR is always 1.0 THRESHOLD OFFSET, bit THRES_LEN The threshold passed to the comparator in SEND mode is the sum of the interpolated threshold function and an additional offset value. This offset value is: • 62 for short range • 31 for long range Summarized: the threshold value used for the interpolation algorithm is calculated as following: This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 18 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 Threshold value for noise measurement Constant threshold value during interval 0 Linear interpolation Start of SEND or RECEIVE mode Interval 14 Interval 13 Interval 12 Interval 11 Interval 10 Interval 9 Interval 8 Interval 7 Interval 6 Interval 5 Interval 4 Interval 3 Interval 2 Interval 1 SEND or RECEIVE request Interval 0 Threshold value max time End of SEND or RECEIVE mode offset Fig. 5.3.3.1-1: intervals of SEND or RECEIVE mode and related threshold values example 1: short range, send request, THRESn programmed to 15 example 2: long range, receive request, scaling_factor=0.75, THRESn programmed to 7 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 19 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.3.3.2 NOISE measurement during SEND and RECEIVE command As increased ambient noise might disturb the measurement in SEND or RECEIVE mode, the IC measures the ambient supersonic noise directly before entering SEND or RECEIVE mode. The ambient noise measurement is performed during the low phase of the SEND or RECEIVE command (T SND / TREC). The output of the digital filter is compared to a threshold value which is passed from the control unit to the comparator. The threshold value can be selected by bits NOISE_CFG[1:0] according to Table 5.3.3.2-1. NOISE_CFG[1] 0 NOISE_CFG[0] 0 0 1 1 1 0 1 threshold value threshold value at the end of previous SEND or RECEIVE mode, but SCALING_FACTOR fixed to 1.0 62 124 620 Table 5.3.3.2-1: Threshold value for noise measurement depending of bits NOISE_CFG[1:0] With the IO command "READ STATUS" the noise information can be read. The threshold value for the first noise measurement after 'power on' is at maximum value of 1023. The result of the noise measurement is output by the status register. 5.3.3.3 Masking of comparator output The comparator output can be masked for the time T CMASK after the output signal of the digital filter drops below the comparator threshold. This functionality might be useful if the IC is operated with high gain and low comparator threshold. In this combination even low noise coupling from the IO line to the analog input circuitry e.g. the transformer can cause an additional echo signal. The masking can be enabled with bit COMP_MASK according to Table 5.3.3.3-1. COMP_MASK 0 1 function Comparator masking not active Comparator masking active Table 5.3.3.3-1: function of bit COMP_MASK This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 20 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4 IO Interface Bumper module Body control unit E524.03 CONTROL VSUP_LINE RIO_PU_BCU RSUP DSUP VSUP CSUP1 CSUP2 RXD TXD GND_LINE IO_INTERFACE Debouncing RIO_PU C_IO_BCU IO RIO_S IO_LINE CIO1 CIO2 GNDP Fig. 5.4-1: block diagram IO interface The IO interface manages the communication between bumper control unit (BCU) and the bumper module. Data is transferred via the IO line. Exchange of commands, register- and EEPROM data In order to send data to the bumper module the IO line voltage has to be modulated by the bumper control unit. A voltage at the IC-pin IO below VIO_IL will be detected as low level, a voltage above VIO_IH as high level. The input has a debouncing circuit that suppresses interference signals shorter than TDEB. Data is transmitted from the bumper module to the BCU by modulating the pulldown current IPD_IO into pin IO. IPD_IO pulls down the voltage of the IO line against the external pull up resistors RIO_PU and RIO_PU_BCU. In order to reduce EMI the current IPD_IO is regulated to achieve a voltage slew rate of SRVIO of the falling edge at line IO, as the rising edge is defined by the external circuitry the current can only be regulated to guarantee a slew rate less than SRVIO. Echo reporting In SEND and RECEIVE mode, the IO interface outputs a detected echo signal. A valid echo signal (see 5.3.3.1) is reported with a low level as long as the filter output signal exceeds the actual threshold. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 21 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 Diagnosis report in SEND mode The IC offers the opportunity to test the proper connection of the transducer. After entering SEND mode, the transducer driver is activated. This causes high signals at the amplifier input and the comparator will detect an 'echo signal'. A properly connected transducer in conjunction with the transformer will continue to oscillate for a certain release time, even if the transducer driver is already deactivated. Thus the release time of the transducer/transformer combination is an indicator for the transducer connection see Fig. 5.4.1-1. Bit Encoding The sequence to send or receive a logical '1' or '0' on the IO line is shown in the following diagram: 0 TBIT0 TBIT 1 TBIT1 TBIT Fig. 5.4-2: Bit Encoding Commands The device provides the following state commands transmitted from the ECU applied to the IO: • Send Request • Receive Request • Threshold Programming • Read Status • EE-Write • EE-Read • EE-Programming • Measurement Configuration • Driver Frequency calibration This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 22 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4.1 Send Request This command is used to send a burst. After the burst the device is in the receive mode with 100% of the threshold range. The following diagrams show examples for a send request. threshold signal line t IO TSND TTX Echo Reporting IO line controlled by host IO line controlled by sensor Fig. 5.4.1-1: Send Request 5.4.2 Receive Request Operation as a pure receiving unit without triggering the ultrasonic transducer is initiated by a bus signal. The threshold for echo detection can be programmed to 25%, 50%, 75% or 100% of full threshold range. threshold signal line t IO TREC Echo Reporting IO line controlled by host IO line controlled by sensor Fig. 5.4.2-1: Receive Request This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 23 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4.3 Threshold programming With this command the threshold values and several control bits for threshold scaling are written into the device: Bit no. of bits 0-4 5-9 10-14 15-19 20-24 25-29 30-34 35-39 40-44 45-49 50-54 55-59 60-64 65-69 70-71 5 5 5 5 5 5 5 5 5 5 5 5 5 5 2 72 73 1 1 74 75 76 77 78 1 1 1 1 1 Function 1st threshold value 2nd threshold value 3rd threshold value 4th threshold value 5th threshold value 6th threshold value 7th threshold value 8th threshold value 9th threshold value 10th threshold value 11th threshold value 12th threshold value 13th threshold value 14th threshold value Scaling for receive operation Initial threshold value Length of measurement cycle even parity bit for bit 73-58 even parity bit for bit 57-42 even parity bit for bit 41-26 even parity bit for bit 25-10 even_parity bit for bit 9-0 Name THRES1 THRES2 THRES3 THRES4 THRES5 THRES6 THRES7 THRES8 THRES9 THRES10 THRES11 THRES12 THRES13 THRES14 TRES_SCALE[1: 0] THRES_INI THRES_LEN PARITY0 PARITY1 PARITY2 PARITY3 PARITY4 Default (bin) 31 31 31 30 29 28 27 25 22 14 10 6 0 0 2 0 0 - Table 5.4.3-1: Write threshold command The first bit transmitted on the IO line is the MSB of thres1 (bit 0) and the last bit is the parity bit 78 (parity for bits 0...9). This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 24 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 IO TCMD TD 0 0 0 1 command threshold values + parity bits IO line controlled by host IO line controlled by sensor Fig. 5.4.3-1: Write threshold command 5.4.4 Read Status The command 'read status' can be used to verify the last transmission of the threshold values and to get information about the noise level of the latest send/receive request. The noise level is analyzed during the low phase on the IO line of the send/receive request command. The meaning of these two bits is as follows: first bit 0 1 meaning last data reception incorrect, default data active last data reception successful, transmitted data active Table 5.4.4-1: Read Status: First Bit second bit 0 1 meaning no noise detected during last measurement cycle noise detected during last measurement cycle Table 5.4.4-2: Read Status: Second Bit IO TCMD TD 0 0 1 0 command 2 bit status IO line controlled by host IO line controlled by sensor Fig. 5.4.4-1: Read status command This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 25 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4.5 EE-Write The adjustment values for oscillator, gain of amplifier and ultrasonic level can also be communicated via the bi-directional interface. During the last functional test of the system, the values can be read in, adjusted and stored in an EEPROM. The function of all EEPROM bit is described in the following table: Bit no. of bits 0 1 Name SPARE_BIT 1 1 IOMASK 2-3 4 2 1 NOISE_CFG FILTADJUST 5-11 7 F_DRV_ADJ 12-15 4 DRV_CUR 16-19 4 AMP_GAIN Function EEPROM bit without internal functionality, can be used for customer specific data disable change on IO after rising edge on IO noise strategy adjustment of filter bandwidth driver frequency adjustment transducer current adjustment amplifier gain adjustment Default (dec) 0 0 3 0 calibrated to fDRV = 48 kHz 8 8 Table 5.4.5-1: EE-Programming If "write EEPROM data" is selected the data bits follow directly after the command bits. The transmitted data bits overwrite the EEPROM data to test the new EEPROM values. The first bit transmitted on the IO line is the highest bit of the spare bits (bit 0) and the last bit is the LSB of AMP_GAIN (bit 19). IO TCMD TD 0 1 0 1 command EEPROM data IO line controlled by host IO line controlled by sensor Fig. 5.4.5-1: Write EEPROM data command This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 26 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4.6 EE-Read The "read EEPROM" command loads the EEPROM contents into registers and transmits them on the IO line. The EEPROM contents will be delivered three times: first time using the nominal read voltage of the EEPROM cell, second with a low level read voltage and third time with high level read voltage. That gives the user a hint, whether the EEPROM cell has been programmed properly. Additionally a status bit is transmitted. The status bit follows the EEPROM bits, so it is also transmitted three times. This bit is the output of a programming voltage comparator which observes the programming voltage during the programming procedure. A high level means the programming voltage has been in the correct range, a low levels shows that the programming was not correct. The first bit transmitted on the IO line is the highest bit of the spare bits (bit 0 table 'EE-Write') followed by bits 1 to 19 and additional bit 20 -programming voltage status-. This sequence is repeated two times as described above. IO TCMD TD 0 1 0 0 command EEPROM data IO line controlled by host IO line controlled by sensor Fig. 5.4.6-1: Read EEPROM data command 5.4.7 EE-Programming When choosing the functionality "program EEPROM", the EEPROM data bits will be programmed with the current register contents. The whole procedure has to be finished by a waiting time of T PROG. During this time, the voltage of the Pin IO has to be set to VPROG within TVPROG. Otherwise, the EEPROM will not be programmed. VPROG IO TCMD_PROG TD 0 1 1 0 TVPROG TPROG command IO line controlled by host IO line controlled by sensor Fig. 5.4.7-1: Program EEPROM command This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 27 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.4.8 Measurement Configuration To achieve an improved short distance capability of the sensor the gain and burst length can be reduced. The following table shows the different commands for the configuration of the bust length and gain reduction: Command (bin) number of burstpulses / NBURST 8 16 8 16 1100 1101 1110 1111 gain reduction / GRED default configuration OFF OFF ON ON Table 5.4.8-1: Measurement Configuration IO TCMD TD 1 1 X X command config IO line controlled by host IO line controlled by sensor Fig. 5.4.8-1: Configure Measurement command 5.4.9 Driver Frequency Calibration To calibrate the internal oscillator to the required frequency eight pulses with a defined width of T CAL each can be driven on the IO line. The following diagram shows the flow: IO TCMD_PROG TD 0 0 1 1 TD TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL TCAL command IO line controlled by host IO line controlled by sensor Fig. 5.4.9-1: Oscillator Calibration Pulse This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 28 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.5 JTAG Interface for lab analysis To access the test and debug structures of the IC a 4 -wire JTAG interface is used. The JTAG interface can be accessed via pins TMS,TCK, TDI and TDO when the TMEN pin is set to one. TMEN pin set to zero resets all test and debug structures, the IC operates in normal mode. The JTAG will not be reset by the internal power-on-reset (POR). 5.5.1 JTAG Instruction Register The instruction register (IR) is 8 bits wide with the least-significant bit (LSB) shifted in first. Each instruction bit is captured from TDI by the IC on the rising edge of TCK. Fig. 5.5.1-1 shows how to load an instruction into the JTAG IR register. See Table 5.5.3-1 for a complete list of the JTAG instructions used to access the test registers. Fig. 5.5.1-1: Instruction Register Access 5.5.2 JTAG Data Register A 20-bit wide JTAG data register (DR) is implemented. The data word is shifted, most-significant bit (MSB) first, into the IC's TDI input. Each bit is captured from TDI on a rising edge of TCK. At the same time, TDO shifts out the last captured/stored value in the addressed data register. A new bit is present at TDO with a falling edge of TCK. Fig. 5.5.2-1: Data Register Access shows how to load a n-bit word into the JTAG DR and read out a stored value via TDO. Fig. 5.5.2-1: Data Register Access This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 29 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 5.5.3 JTAG Instruction Summary instruction name IR_READ_ENV IR_READ_THRES IR_READ_ENVTHRES value / hex 0xD0 0xD1 0xD2 description read current envelope value read current threshold value read current envelope and threshold value Table 5.5.3-1: JTAG Instructions 5.5.4 JTAG Instruction "IR_READ_ENV" After shifting the instruction "IR_READ_ENV" into the JTAG instruction register the IC will return the current result of the receiving chain (filter output) on the TDO output. Incoming data on TDI is ignored. The output value is 10 bit wide and the maximum read frequency is f TCK = 2.0 MHz. 5.5.5 JTAG Instruction "IR_READ_THRES" After shifting the instruction "IR_READ_THRES" into the JTAG instruction register the ASIC will return the current threshold level at the comparator input on the TDO output. Incoming data on TDI is ignored. The output value is 10 bit wide and the maximum read frequency is f TCK = 2.0 MHz. 5.5.6 JTAG Instruction "IR_READ_ENVTHRES" With the instruction "IR_READ_ENVTHRES" shifted into the JTAG instruction register the IC will return the current result of the receiving chain (filter output) and the current threshold level at the comparator input on the TDO output. Incoming data on TDI is ignored. The output value is 20 bit wide and the maximum read frequency is fTCK = 2.0 MHz. First 10 bits of the receiving channel are transmitted starting with the MSB followed by the 10 bit comparator threshold value. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 30 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 6 ESD, Latchup and EMC 6.1 Electro Static Discharge (ESD) Standard Model Capacitance Resistance Voltage Pulse rise time (10%-90%) Test point Number of pulses AEC-Q100-002 Human Body Model 100pF 1,5 kΩ +/- 4 kV for leads VSUP,IO +/- 2 kV for all other leads <10 ns pin to supply 1 of each polarity Table 6.1-1: ESD on IC Level, Human Body Model (HBM) Standard Model Resistance Voltage Pulse rise time (10%-90%) Test point Number of pulses AEC-Q100-011 Charged Device Model 1Ω +/- 750 V for corner leads +/- 500 V for all other leads <400 ps pin to supply 3 of each polarity Table 6.1-2: ESD on IC Level, Charged Device Model (CDM) 6.2 Latch-up Latch-up performance is validated according JEDEC standard JESD 78 in its valid revision. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 31 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 6.3 6.3.1 EMC Chip Level Measurement of electromagnetic emission and immunity is performed in a frequency range of 150kHz to 1GHz with the typical application. Emission is validated according: IEC 61967 - 4 ( conducted : 150Ω-Methode ) IEC 61967 - 2 ( radiated : GTEM-Methode ) Susceptibility is validated according: • • • • IEC 62132 - 4 ( conducted : DPI-Methode ) IEC 62132 - 2 ( radiated : GTEM-Methode ) Immunity against Transients is validated on the SUP_LINE according to ISO 7637-1, ISO 7637-2 on the IO_LINE according to ISO 7637-1, ISO 7637-3 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 32 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 7 Marking 7.1 Top Side ELMOS 52403 YWW*# AXXXP Table 7.1-1: Top Side marking of device E524.03 center aligned Signature 52403 YWW * # A XXX P Explanation ELMOS project number Year and week of assembly Mask revision code ELMOS internal code ELMOS project revision code Production lot number Assembler code Table 7.1-2: Explanation of marking signatures of device E524.03 This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 33 / 34 Qm-No.: 25DS0068E.00 3-Wire Ultrasonic Transceiver Driver and Signal Processor E524.03 PRELIMINARY INFORMATION - AUG 01, 2011 WARNING – Life Support Applications Policy ELMOS Semiconductor AG is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing ELMOS Semiconductor AG products, to observe standards of safety, and to avoid situations in which malfunction or failure of an ELMOS Semiconductor AG Product could cause loss of human life, body injury or damage to property. In development your designs, please ensure that ELMOS Semiconductor AG products are used within specified operating ranges as set forth in the most recent product specifications. General Disclaimer Information furnished by ELMOS Semiconductor AG is believed to be accurate and reliable. However, no responsibility is assumed by ELMOS Semiconductor AG for its use, nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ELMOS Semiconductor AG. ELMOS Semiconductor AG reserves the right to make changes to this document or the products contained therein without prior notice, to improve performance, reliability, or manufacturability . Application Disclaimer Circuit diagrams may contain components not manufactured by ELMOS Semiconductor AG, which are included as means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. The information in the application examples has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of ELMOS Semiconductor AG or others. Contact Information Headquarters ELMOS Semiconductor AG Heinrich-Hertz-Str. 1 • D-44227 Dortmund (Germany) +492317549100 Regional Sales and Application Support Office Munich ELMOS Semiconductor AG Am Geflügelhof 12 • 85716 Unterschleißheim/Eching +49893183700 : sales@elmos.de : www.elmos.de Sales Office France ELMOS FRANCE SAS 9/11 allée de l'Arche • La Défense • 92671 Courbevoie cedex (France) +33149971591 Sales and Application Support Office North America ELMOS NA. Inc. 32255 Northwestern Highway, Suite 45 • Farmington Hills, MI 48334 +12488653200 Sales and Application Support Office Korea and Japan ELMOS Korea Dongbu Root building, 16-2, Suite 509, • Sunae-dong, Bundang-gu, Seongnam-shi, Kyonggi-do (Korea) +82317141131 Sales and Application Support Office China ELMOS Semiconductor Technology (Shanghai) Co., Ltd. 57-01E, Lampl Business Centre, 57F, The Exchange • 1486 Nanjing W Rd. (299 Tongren Rd) • JingAn Shanghai • P.R.China 200040 +862161717358 Sales and Application Support Office Singapore ELMOS Semiconductor Singapore Pte Ltd. 60 Alexandra Terrace • #09-31 The Comtech • Singapore 118502 +6566351141 © ELMOS Semiconductor AG, 2011. Reproduction, in part or whole, without the prior written consent of ELMOS Semiconductor AG, is prohibited. This document contains information on a product under development. ELMOS Semiconductor AG reserves the right to change or discontinue this product without notice. ELMOS Semiconductor AG Data Sheet 34 / 34 Qm-No.: 25DS0068E.00