TZ2100 Series

Technical Data Sheet

CMOS Digital Integrated Circuit Silicon Monolithic

TZ2100 Series

Application Processor Lite ApP Lite™

Overview

TZ2100 series are application processors utilizing a single 600 MHz ARM® Cortex® -A9 core with a floating

point unit (FPU), a 2D graphics, a parallel LCD controller interface, camera input interface and an 1 MB of

integrated SRAM. This device is highly integrated, as a main processor for various applications with integrated a

USB host or device controller (optional), an Ethernet controller, an extended external buses, and rich interfaces.

The TZ2100 processors are supported a security service with an encryption and decryption capability (optional)

and a secure boot function (optional) to enable construction of a robust secure system. These products are suitable

for various applications, in addition, an SRAM and a RTC for back-up mode of power state are incorporated.

The TZ2100 series are family products of ApP Lite™.

Applications

This product is leveraged to meet needs of following applications; human machine interface, machine to machine

interface, single-board computing and portable data terminal.

Features

● Host CPU

‒ ARM Cortex-A9 MP Core (Revision r4p1p)

Up to 600 MHz operation frequency

‒ ARMv7-A instruction set architecture

‒ Floating point unit (FPU)

‒ 32 KB L1 I cache/ D cache

‒ 128 KB L2 cache

‒ Memory management unit: 128-entry TLB

‒ Debug technology:

CoreSightTM (revision: r2p0-01)

v7 debug architecture, JTAG debug interface

‒ Proprietary low power mode for WFI

● System contoller

‒ System management unit (SMU):

Reset management, clock controller

‒ Power management unit (PMU):

External and internal power management

‒ Secure boot (optional)

‒ Secure services (optional)

AES, SHA-1, SHA-256, RSA

Random number generator (RNG)

‒ Interruption controller

● SDRAM controller

‒ DDR3 / 3L memory interface (16-bit width)

‒ Data rate:

800 Mbps

‒ Memory size: up to 512 MB

‒ ODT control

2016-07-19

● Integrated SRAM

‒ 1 MB SRAM

‒ 32 KB SRAM for data backup

Low power dissipation for data retention

● Real time clock (RTC)

Low power dissipation

‒ Clock frequency:

32.768 kHz

‒ Clock timer, Calendar

‒ Time adjustment, alarm interrupt, Periodic interrupt,

BCD format

● DMA controller

‒ AXI protocol DMA with DMA330 supported

‒ Multiple transfer mode

Memory to Memory, Memory to Peripheral, and

Peripheral to Memory

‒ 8 channels thread for DMA transfer and one channel

thread for DMA management

● Timer

‒ 16 channels of 32-bit down counter

enable one channel as watch dog timer

● 2D graphics accelerator

‒ Toshiba original graphics accelerator

‒ Blitting, Rotation, Transforming, Drawing

● YUV to RGB converter

‒ Input format: YUV 4:2:0 8bit, YUV 4:2:2 8bit

‒ Input resolution: QVGA, VGA, up to 2048×2048

‒ Output format: RGBA8888, ARGB8888, RGB565,

RGB888

1 / 64

Rev. 1.6

© 2015 Toshiba Corporation

TZ2100 Series

Technical Data Sheet

● LCD controller

‒ Parallel output:

‒ Output resolution:

‒ Frame rate:

‒ Input format:

●

●

●

●

●

●

RGB 24 bits

up to WVGA

up to 60 fps

RGBA8888, ARGB8888,

RGB565, ARGB1555

‒ Alpha blending: up to five planes

Camera input:

‒ One channel

‒ Parallel input:

8-bit Data

‒ Frame rate:

up to 60 fps

‒ Resolution (by 8-pixel): up to 2048 × 2048

‒ Input format:

YUV 4:2:2 8-bit,

RAW8, RGB565,

ITU-RBT.656

Audio interfaces

‒ Two channels: 1 channel dedicated for output

1 channel for input and output

‒ Format:

I2S stereo, LR stereo, PCM monaural

‒ Sampling clock:

192 kHz, 96 kHz, 48 kHz,

44.1 kHz, 32 kHz, etc.

USB2.0 host interface (optional)

‒ One port USB 2.0 (EHCI rev 1.0, OHCI)

‒ Data transfer rate: 480 Mbps / 12 Mbps / 1.5 Mbps

‒ Transmission mode:

control, interrupt,

bulk, isochronous

USB2.0 device interface (optional)

‒ One port (exclusively used by Host / Device)

‒ Data transfer rate: 480 Mbps / 12 Mbps / 1.5 Mbps

‒ Transmission mode:

control, interrupt,

bulk, isochronous

10/100 Ethernet MAC

‒ One Ethernet MAC channel for 10/100 Mbps

‒ IEEE Standard 802.3,2000 Edition

‒ Support full duplex/half duplex communication

‒ RMII (10/100 Mbps) interface to Ethernet PHY

device

‒ IEEE802.3x flow control function

‒ Support Jumbo Frame (up to 4 KB)

eMMC / SD Card / SDIO interface

‒ Two channels for 4-bit data width.

‒ One channel for 8bit-data width.

‒ Data transmission rate: 150 MHz (max)

‒ Supported standard:

eMMC Ver. 4.5, SD Ver. 3.0, and SDIO Ver. 3.0

DS, HS, SDR12, SDR25, SDR50, SDR104 modes.

‒ SD card control terminals

2016-07-19

● SPI Flash Memory Controller interface

‒ Chip select: 2-bit

‒ Data bus width: Single, Dual or Quad mode interface

‒ Data transmission rate: up to 50 MHz

‒ Memory size: from 64 KB to 128 MB

● SPI interfaces (for master controller and transmission)

‒ Seven channels for transmission or two for master

controller can be selected.

Data transmission rate: up to 25 MHz

‒ One channel for slave controller

Data transmission rate: up to 5 MHz

● External BUS interface

‒ Data BUS width:

32 bits, 16 bits and 8 bits Coexistence is allowed.

‒ Address BUS width:

27 bits

‒ Memory capacity:

up to 768 MB

‒ Chip select:

4-bit

‒ Asynchronous read/write, asynchronous page read,

synchronous burst read/write.

‒ Asynchronous boot devices are supported.

● UART interfaces

‒ Four channels. One channel without flow control

port.

‒ Data transmission rate: up to 1.5 Mbps

‒ Flow control ports

Compatible with UART 16550 data format

Support external clock input.

Full duplex transmission mode and DMA

transfer mode

● I2C bus interfaces

‒ Four channels

‒ Open drain output and Schmidt-trigger input

‒ Support fast mode plus (up to 1000 kbps), Fast

mode, Standard mode

‒ A master (compatible with a multi-master) or a slave

is selectable.

● Parallel port input interface

‒ One channel

‒ Data width: 8-bit

‒ Data FIFO: 8-bit × 16-stage

● GPIO interface

‒ Up to 128 channels

‒ External inputs can be used as interrupt signals.

● AD converter inputs

‒ Four input channels

‒ 12-bit successive AD converter

‒ Sampling rate: up to 1.07 MHz

● PWM outputs

‒ Six channels

‒ Frequencies and duty ratios can be arbitrarily set.

2 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

List of Products

This table shows TZ2100 Series lineups. The following table shows the items which have a difference in

specifications.

Product Number

Maximum

CPU Operation

Frequency (MHz)

TZ2100XBG(O,2)

TZ2100XBG(O,5)

TZ2102XBG(O,3)

TZ2102XBG(O,6)

TZ2101XBG(O,6)

300

300

600

600

600

Operating

Temperature

Range

Ta (°C)

-40~85

-20~80

-20~80

-40~85

-40~85

Internal

Voltage

Range (V)

Security

service

availability

USB 2.0

Interface

1.00~1.20

1.00~1.20

1.06~1.21

1.10~1.20

1.10~1.20

—

—

—

—

Available

—

Host / Device

Host

Host / Device

Host / Device

ApP Lite is a trade mark of Toshiba corporation.

2016-07-19

3 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

List of Contents

Overview............................................................................................................................................................... 1

Applications .......................................................................................................................................................... 1

Features ............................................................................................................................................................... 1

List of Products..................................................................................................................................................... 3

Preface ................................................................................................................................................................. 8

References ........................................................................................................................................................... 8

Conventions in this document .......................................................................................................................... 8

1. Features ........................................................................................................................................................... 9

1.1. CPU ........................................................................................................................................................... 9

1.2. System controller ....................................................................................................................................... 9

1.3. SDRAM controller ...................................................................................................................................... 9

1.4. Integrated Memory .................................................................................................................................. 10

1.5. Real time clock (RTC) ............................................................................................................................. 10

1.6. Peripheral functions ................................................................................................................................. 10

1.7. Graphics Accelerator, YUV Conversion and LCD Controller.................................................................. 10

1.8. Camera Input ........................................................................................................................................... 11

1.9. Audio interfaces ....................................................................................................................................... 11

1.10. High-speed interface Controller ............................................................................................................ 11

1.11. Peripheral Interfaces ............................................................................................................................. 12

2. Block Diagram ................................................................................................................................................ 14

3. Pin Information ............................................................................................................................................... 15

3.1. Pin Alignment .......................................................................................................................................... 15

3.2. Pin List (Ball number order)..................................................................................................................... 16

3.3. Signal description (in order of pin function)............................................................................................. 20

Clock Sources and Reset ........................................................................................................................................... 20

DDR3/DDR3L Memory Interface ................................................................................................................................ 20

SPI Flash Memory Controller Interface....................................................................................................................... 22

eMMC / SD card / SDIO Interfaces............................................................................................................................. 22

External BUS interface ............................................................................................................................................... 23

UART interface ........................................................................................................................................................... 24

I2C bus interface ......................................................................................................................................................... 25

SPI Interfaces (for Master Controller) ......................................................................................................................... 26

SPI Interfaces (Dedicated for Transmission) .............................................................................................................. 26

SPI Interface (for Slave Controller) ........................................................................................................................... 27

USB2.0 Host or Device Interface .............................................................................................................................. 27

Ethernet MAC Interface ............................................................................................................................................ 27

Camera Input ............................................................................................................................................................ 28

Display Output .......................................................................................................................................................... 28

Audio Interface ......................................................................................................................................................... 29

PWM Output ............................................................................................................................................................. 29

Parallel Port Input Interface ...................................................................................................................................... 29

2016-07-19

4 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

GPIO Interfaces ........................................................................................................................................................ 30

AD Converter Input ................................................................................................................................................... 33

JTAG interface for debugging ................................................................................................................................... 33

Others ....................................................................................................................................................................... 33

VDDs and VSSs ....................................................................................................................................................... 34

3.4. Setting Pin Functions............................................................................................................................... 35

Setting pin function with Registers.............................................................................................................................. 35

4. Electrical characteristics................................................................................................................................. 38

4.1. Absolute Maximum ratings ...................................................................................................................... 38

4.2. Recommended Operating Conditions ..................................................................................................... 38

Operating Conditions of the TZ2100XBG ................................................................................................................... 38

Operating Conditions of TZ2102XBG ......................................................................................................................... 39

Operating Conditions of TZ2101XBG/TZ2102XBG (Extended Temperature Products) ............................................. 40

4.3. Current Dissipations ................................................................................................................................ 41

4.4. DC Characteristics................................................................................................................................... 42

Digital I/O pins ............................................................................................................................................................ 42

eMMC/SD Card/SDIO pins ......................................................................................................................................... 43

4.5. AC Characteristics ................................................................................................................................... 44

Clock Inputs ................................................................................................................................................................ 44

DDR3/DDR3L Memory Interface ................................................................................................................................ 45

SPI Flash Memory Controller Interface....................................................................................................................... 46

eMMC / SD Card / SDIO Interface.............................................................................................................................. 47

External Bus Interface ................................................................................................................................................ 50

4.5.5.1. Synchronous mode .......................................................................................................................................................50

4.5.5.2. Asynchronous Mode......................................................................................................................................................51

I2C Bus Interface ........................................................................................................................................................ 52

SPI Interface (for Master Controller and Transmission).............................................................................................. 54

SPI Interface (for Slave Controller) ............................................................................................................................. 55

Ethernet MAC interface .............................................................................................................................................. 56

Camera Input ............................................................................................................................................................ 57

LCD Output............................................................................................................................................................... 58

Audio Interface ......................................................................................................................................................... 59

Parallel Data Input .................................................................................................................................................... 61

AD Conversion Input ................................................................................................................................................ 61

5. Package ......................................................................................................................................................... 62

5.1. Package outline ....................................................................................................................................... 62

6. Revision history .............................................................................................................................................. 63

RESTRICTIONS ON PRODUCT USE............................................................................................................... 64

2016-07-19

5 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

List of Figures

Figure 2.1 Block diagram ......................................................................................................................... 14

Figure 3.1 Pin alignment of this product .................................................................................................. 15

Figure 5.1 Package Outline...................................................................................................................... 62

List of Tables

Table 3.1 Pin List (Ball number order) ..................................................................................................... 16

Table 3.2 Shared Pin Switching Table ..................................................................................................... 35

Table 6.1 Revision History ....................................................................................................................... 63

2016-07-19

6 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

* ARM, AMBA, Cortex, Jazelle, NEON, and TrustZone are registered trademarks of ARM Limited (or its

subsidiaries) in the EU and/or elsewhere. CoreLink and CoreSight are trademarks of ARM Limited (or its

subsidiaries) in the EU and/or elsewhere. All rights reserved.

* All other trademarks and trade names are properties of their respective owners.

2016-07-19

7 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

Preface

References

● Reference standard

‒ DDR3 SDRAM SPECIFICATION

Conventions in this document

● The numerical values are expressed as follows.

Hexadecimal number: 0xABC

Decimal number: 123 or 0d123 - Only when it needs to be explicitly shown that they are decimal numbers.

Binary number: 0b111 - It is possible to omit the "0b" when the number of bit can be distinctly understood

from a sentence.

● "_N" is added to the end of signal names to indicate low active signals.

● It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

● When two or more signal names are referred, they are described like as [m:n].

Example: S[3:0] shows four signal names S3, S2, S1, and S0 together.

● The characters surrounded by [ ] defines the register.

Example: [ABCD]

● "n" substitutes suffix number of two or more same kind of registers, fields, and bit names.

Example: [XYZ1], [XYZ2], and [XYZ3] to [XYZn]

● The bit range of a register is written like as [m:n].

Example: Bit[3:0] expresses the range of bits 3 to 0.

● The configuration value of a register is expressed by either the hexadecimal number or the binary number.

Example: [ABCD].EFG = 0x01 (hexadecimal), [XYZn].VW = 1 (binary)

● Word and Byte represent the following bit length.

Byte:

8-bit

Half word:

16-bit

Word:

32-bit

Double word:

64-bit

● Properties of each bit in a register are expressed as follows.

R: Read only

W: Write only

W1C:

Write 1 Clear - The corresponding bit is cleared (=0) when "1" is written to this bit.

W1S:

Write 1 Set - The corresponding bit is set (=1) when "1" is written to this bit.

R/W:

Read and Write are possible.

R/W0C:

Read/Write 0 Clear

R/W1C:

Read/Write 1 Clear

R/W1S:

Read/Write 1 Set

RS/WC:

Read Set/Write Clear - Set after read operation, cleared after write operation.

● Unless otherwise specified, register access supports only word access.

● The register defined as reserved must not be rewritten. Moreover, don't use the read value.

● The value read from the bit having default value of "—" is unknown.

● When a register containing both of writable bits and read-only bits is written, read-only bits should be written

with their default value. In the cases that default is "—," follow the definition of each register.

● Reserved bits of the Write-only register should be written with their default value. In the cases that default is

"—," follow the definition of each register.

2016-07-19

8 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

1. Features

1.1. CPU

(1) Host CPU

ARM Cortex-A9 MP Core (Revision r4p1)

Instruction set architecture: ARMv7-A architecture

Operation frequency:

600 MHz (Note 1) / 300 MHz / 150 MHz / 75 MHz etc., selectable

Level-1 instruction cache: 32 KB (4-wait set associative)

Lvevl-1 date cache:

32 KB (4-wait set associative)

Level-2 cache:

128 KB (8-wait set associative)

Data engine:

Floating point unit (FPU)

Support single and double precision data processing

Internal bus:

64-bit AXI master interface

Debug technology:

ARM® CoreSightTM (revision: r2p0-01)

v7 debug architecture, JTAG debug interface

Memory management unit: 128-entry TLB

Pipe line:

Super scalar, out of order

Proprietary low power mode to minimize power consumption in Wait for Interruption command

Note 1:

TZ2101XBG, TZ2102XBG only

1.2. System controller

(1) System management unit (SMU)

Reset management, clock controller

(2) Power management unit (PMU)

External and internal power management

(3) Secure boot (optional)

(4) Secure services (optional)

AES, SHA-1, SHA-256, RSA,

Random number generator (RNG)

(5) Interruption controller

Output interrupt requests to the host CPU

1.3. SDRAM controller

(1) SDRAM controller

DDR3 / 3L memory interface

Bus width:

16-bit

Data rate:

800 Mbps

Memory size:

up to 512 MB

Support self-Refresh mode

ODT controller

2016-07-19

9 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

1.4. Integrated Memory

(1) Internal SRAM

1 MB SRAM is contained for data and programming.

(2) SRAM for data backup

32 KB SRAM for data backup.

Low power dissipation for data retention in a separated power domain

1.5. Real time clock (RTC)

(1) Real time clock (RTC)

Frequency of oscillation:

32.768 kHz

Clock display (hour, minute, second), am-pm / 24-hour

Calendar (month, week, date, and leap year)

Time adjustment, alarm interrupt, Periodic interrupt, BCD format

Low power dissipation in a separated power domain

1.6. Peripheral functions

(1) DMA controller

Multiple transfer mode (Memory to Memory, Memory to Peripheral, Peripheral to Memory)

Original instruction set enables programmable DMA transfer.

Eight channel threads for DMA transfer and one channel thread for DMA management

(2) Timer

16 channels of 32-bit down counter.

One counter can be selected as a watchdog timer (WDT).

1.7. Graphics Accelerator, YUV Conversion and LCD Controller

(1) 2D graphics accelerator

Toshiba original graphics accelerator

Blitting engine (Alpha blending), Transforming engine, Rotation engine (Rotation, Scaling, Transparent),

Drawing engine (Anti-Aliasing)

Output format:

RGBA8888, ARGB8888, RGB565, ARGB1555

(2) YUV converter

YUV to RGB conversion

Input resolution: QVGA, VGA, 2048 × 2048 (max)

Input format:

YUV_4:2:0 8-bit, YUV_4:2:2 8-bit

Output format:

RGBA8888, ARGB8888, RGB565, RGB888

(3) LCD controller

Parallel output:

Output resolution:

Frame rate:

Input format:

Alpha blending:

2016-07-19

24-bit (RGB), Vsync, Hsync, Clock, Valid

up to WVGA (800 × 480 max)

up to 60 fps

RGBA8888, ARGB8888, RGB565, ARGB1555

up to Five planes

10 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

1.8. Camera Input

(1) 8-bit Parallel

Parallel input:

Frame rate:

Resolution:

Input format:

8-bit Data, Vsync, Hsync/ Enable, Clock

up to 60 fps

up to 2048 × 2048 (by 8-pixel)

YUV 4:2:2 8-bit, RAW8, RGB565, ITU-RBT.656

1.9. Audio interfaces

(1) Audio Interfaces

Two channels:

Audio format:

Sampling frequency:

One channel dedicated for output, and the other one for output and input.

Selectable master or slave

I2S stereo, LR stereo, PCM monaural

192 kHz, 96 kHz, 48 kHz, 44.1 kHz, 32 kHz, 24 kHz

1.10. High-speed interface Controller

(1) USB2.0 host interface (optional)

USB2.0 host:

1 port

Complaint with USB2.0 (EHCI rev 1.0, OHCI supported)

Data transmission rate:

480 Mbps, 12 Mbps or 1.5 Mbps

Transmission mode:

control, interrupt, bulk, isochronous

(2) USB2.0 device interface (optional)

USB2.0 device:

1 port (exclusive use for Host / Device)

Data transmission rate:

480 Mbps, 12 Mbps or 1.5 Mbps

Transmission mode:

control, interrupt, bulk, isochronous

(3) 10/100 Ethernet MAC Interface

One MAC channel for 10/100 Mbps transmission speed

Complaint with IEEE Standard 802.3,2000 Edition

Support full duplex/half duplex communication

RMII (10/100 Mbps) interface to Ethernet PHY device

IEEE802.3x flow control

Jumbo Frame supported (up to 4 KB)

Upper level protocol function supported (automatic checksum calculation for receiving data)

Dedicated controller for PHY device register access

Interruption synchronizing mode

2016-07-19

11 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

1.11. Peripheral Interfaces

(1) External Bus Interface

Chip select:

4 bits

Data width:

32-bit / 16-bit / 8-bit (these widths can coexist)

Address width:

27 bits

Corresponding Memory size: up to 768 MB

Transfer system:

Asynchronous read/write

Asynchronous page read

Synchronous burst read/write

Boot device support:

Chip enable 0 enables use of a 32-/16-bit device as an asynchronous boot

device.

(2) eMMC / SD Card / SDIO Interface

Three channels:

The data width of one channel is 8 bits and two channels are 4 bits.

Data transmission rate:

150 MHz (max)

Boot device support:

One channel of eMMC and one channel of a SD card can be used as boot

devices.

Transmission mode:

DS/HS/SDR12/SDR25/SDR50/SDR104 for SD card/SDIO

Backward-compatibility/High-Speed/HS200 for eMMC

SD card control pins:

card detection, write protection, power, 3.3 V / 1.8 V voltage switch

Supported standard:

eMMC Ver. 4.5, SD Ver 3.0, and SDIO Ver 3.0.

(3) SPI Flash memory controller interface

Chip select:

2-bit

Boot device support

Data bus width:

Single, Dual or Quad mode

Data transmission rate:

50 MHz (max)

Memory size:

from 64 KB to 128 MB

Support four bytes addressing mode

(4) SPI interfaces (for master controller and transmission)

Two channels can be selected for the master controller. Up to seven channels for transmission can be

selected.

BUS width:

Single mode interface

Data transmission rate:

25 MHz as the maximum frequency, and 1/1 to 1/32767 prescaler is available.

Data FIFO:

16-bit × 16-stage

(5) SPI interface (for slave controller)

One channel

Bit width:

Single mode interface

Data transmission rate:

up to 5 MHz

Data FIFO:

16-bit × 16 stage

(6) UART interfaces

Four channels

Data transmission rate:

up to 1.5 Mbps

Three channels with flow control port

Auto flow control (CTS/RTS)

Complaint with UART 16550 data format

Support external clock input

Support full duplex communication, DMA transmission mode

One channel without flow control port (e.g. debug terminal)

2016-07-19

12 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

(7) I2C bus interfaces

Four channels

Open drain output and Schmidt-trigger input

Data transmission rate:

Standard mode:

up to 100 kbps,

Fast mode:

up to 400 kbps

Fast mode plus:

up to 1000 kbps

Operation mode:

Master (support multi-master) or Slave

(8) Parallel port input interface

Operate as a target and receives write data from an external host.

Data width:

8-bit

FIFO:

8-bit × 16-stage

Support the active polarity of a strobe signal.

(9) GPIO interfaces

128 channels

124 channels are shared with other functions (Open drain output at six channels).

Four channels are dedicated pins. The I/O power supply is VDD3V3_PA (described in Section 3.3.18).

Input or output direction configurable

External inputs can be used as interrupt signals.

Configurable to set pull-up or pull-down resister

(10) AD converter

Four channels

12-bit successive conversion

Sampling frequency:

1.07 MHz (max) when using one channel

379 kHz (max) when using four channels

(11) PWM output

Six channels

Configurable frequency and duty of pluses and synchronous output mode is supported.

Configurable pulse generator

2016-07-19

13 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

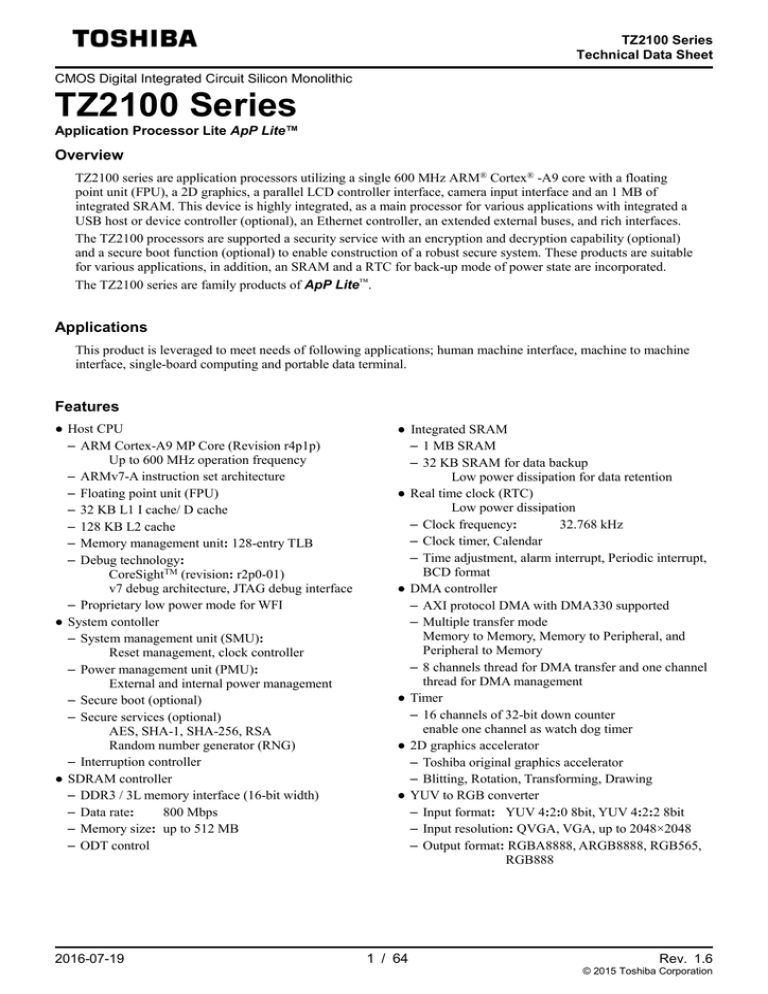

2. Block Diagram

Figure 2.1 shows a block diagram of the TZ2100 Series.

CPU

LCD Controller

ARM Cortex-A9

(600 MHz / 300 MHz)

(L1: I 32 KB/ D 32 KB)

(L2: 128 KB)

FPU

Peripherals

32bit EBUS I/F

2D Graphics

Accelerator

eMMC/SDIO x3

YUV Converter

SPIM/TX x7, SPIS

SPIB x2

UART x4

SDRAM

controller

1 MB SRAM

High speed I/O

Ethernet MAC

USB EHCI (Note 1)

USB

PHY

(Note 1)

USB OHCI (Note 1)

USB2.0 Dev (Note 1)

Camera Input

I2C x4

I2S x2

Encrypt engine

(Note 1)

ADC x4

Power management

Timer x14 (WDT)

PMU

PWM

Timer x2

GPIO

RTC

DMA Controller

Back up SRAM 32KB

Interrupt controller

Figure 2.1 Block diagram

Note 1:

2016-07-19

There are optional functions as follows:

USB2.0 device, USB2.0 host, security service functions and secure boot.

14 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

3. Pin Information

3.1. Pin Alignment

Figure 3.1 shows a pin alignment of this product.

TOP VIEW

B

A

1

C

3

EMMC

0_DAT 0_DAT

VSS

EMMC

0

4

EMMC

EMMC

0_DAT 0_DAT

0_CLK

EMMC

1

5

EMMC

EMMC

0_CLK 0_DAT 0_DAT

B

EMMC

2

6

EMMC

EMMC

0_DAT 0_DAT

0_CMD

6

7

8

9

E3_N

LKO

DD2

DD11

DD14

DD19

E2_N

E_N

EB0_C

DD3

DD9

DD13

DD18

EB0_A EB0_A

E1_N

DD4

DD17

E0_N

DD1

DD6

DD7

DD12

DD16

LKB

LK

_15

GPIO0

GPIO0

GPIO0

GPIO0

GPIO0

_16

_17

_19

_20

_18

GPIO0

GPIO0

GPIO0

GPIO0

_21

_22

_24

_23

LKI

GPIO0

GPIO0

GPIO0

GPIO0

_25

_26

_27

_29

_28

DD5

_30

_31

CLK

SPIB0_ SPIB0_

IO2

IO1

MMC

EL2

EL3

_13

_14

R

GPIO0

I2C0_S GPIO0

T

GPIO0

GPIO0

U

XD

DDR0_

V

EL5

DDR0_ DDR0_

CL

_4

GPIO0

_8

_9

VSS

DQ11

DQ13

VSS

DQ15

DDR0_

DQ9

XD

_10

8_3V3

VDD1V

8_3V3

_SD0

3_PL_I

VDD3V

3_PL_I

2C

VDDC_

PA

GPIO0

VSS

_11

GPIO0

GPIO0

GPIO0

_5

_6

_7

DM1

DDR0_

VSS

DQS_N

DDR0_

DQ14

1

VREF

_3V3_E 8_3V3

MMC

_SD1

VDDC_

VSS

PA

VDDC_

PA

VSS

VDDC_

PA

VSS

DD22

DD21

AT0

AT4

16

17

18

19

AT10

AT11

AT13

AT14

AT15

VSS

AT8

AT12

AT16

AT18

AT19

AT20

AT22

EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D

VD_N

AT6

DD26

AT3

AT17

AT23

AT24

AT25

AT26

AT27

AT7

AT21

VSS

DQ8

VSS

EB0_B EB0_B

E0_N

E1_N

GPIO1

GPIO1 EB0_W XIN_3 XOUT_

_SD1

EBUS

EBUS

VDDC_

PA

VSS

VSS

VSS

VSS

VSS

VSS

PA

VSS

PA

VSS

1_DDR 1_DDR

VDDC_

PA

VSS

VDD_D VDD_D DDR0_

DRIO

DRIO

E_N

E2_N

VSS

VDDC_

AT31

EB0_B EB0_B

AT2

3_PL_

VSS

AT29

DD25

3_PL_

VSS

AT30

VSS

VSS

ZQ

3_PB

OEN_N RST_N

VDD3V

DBG_T LOWP

3_PB

CK

SYS_R

ESET_

3_PA

N

VDD3V

GPIO0

3_PA

_3

VDDC_ VDDPL

PA

VSS

MS

32K

DBG_S

RST_N

DO

AKEUP

VSS

GPIO0 POR_O

_0

DI

SYS_W

WR

R33

VDDPL

UT_N

WDT_

RSTOU

T_N

GPIO0

GPIO0

_2

_1

XIN

XOUT

R33

3_USB 3_USB

USB0_ USB0_ USB0_ USB0_ USB0_

L0

REXT

CLK

VBUS

DM

DP

VSSUS USB0_ VSSUS VSSUS

L2

B

VDD1V

VPGM

2K

PD_BG PD_PO VDD3V VDD3V

L1

VDDC_ VDDPL

PA

AIT_N

E3_N

BAK_IS DBG_T DBG_T DBG_T DBG_T

VDD3V

VDDC_ VDD3V

PA

_0

TEST

B

B

VDD3V VSSAD SAD0_ SAD0_

1_DDR

3_ADC

PLL

C

DIN2

DIN3

DQS_P

DM0

VSS

DDR0_

DQS_N

0

DQ0

DQ6

RAS_N

WE_N

BA2

VSS

CA0

3_ADC

C

DIN0

DIN1

VSS

VSS

VSS

VSS

DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_

0

VSS

AT28

EB0_A EB0_D

8_3V3

VDDC_ VDD1V VDD1V

VSS

DQ2

DQ4

CAS_N

ODT

BA0

DDR0_ DDR0_ DDR0_ DDR0_ DDR0_

DQ3

DQ5

CS_N

CA15

CA8

CA3

DDR0_

RESET

_N

CA2

CA9

CA13

DDR0_ DDR0_ DDR0_

CA5

CA7

BA1

VSS

VSS

DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_

DQ1

Figure 3.1

2016-07-19

15

VDD3V VSSAD SAD0_ SAD0_

DDR0_

VSS

DDR0_

DQS_P

DDR0_

DQ10

1

VSS

AT9

DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_ DDR0_

DQ12

DDR0_

VSS

AT5

2C

EL4

_12

DDR0_

AT1

VDD3V

I2C0_S GPIO0

VSS

DD23

DD20

_SD0

IO0

DA

DD15

VDD1V

CS0_N CS1_N

N

EL1

DD10

_3V3_E

BOOTS BOOTS BOOTS BOOTS BOOTS

EL0

DD24

VDD1V8 VDD1V8 VDD1V VDD1V VDD3V VDD3V

SPIB0_ SPIB0_

IO3

14

_1

GPIO0 SPIB0_ SPIB0_ SPIB0_

BOOTS UA0_R UA0_T GPIO0

W

DD0

GPIO0

P

M

L

K

J

H

MD

GPIO0

13

EB0_C EB0_A EB0_A EB0_A EB0_A EB0_A EB0_A EB0_A EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_W

AT0

AT1

12

EB0_A EB0_A EB0_A

DD8

SD0_D SD0_C SD0_C SD0_C GPIO0

AT2

11

EB0_C EB0_O EB0_A EB0_A EB0_A EB0_A EB0_A EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D

SD0_D SD0_D SD0_D EB0_C EB0_A EB0_A EB0_A EB0_A EB0_A

AT3

10

EB0_C EB0_C EB0_A EB0_A EB0_A EB0_A EB0_A EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D EB0_D

E

7

5

F

3

4

G

D

2

EMMC

DQ7

CKE

CA10

CA6

CA11

CA14

CA4

CA1

CA12

DDR0_

CK_P

DDR0_

CK_N

VSS

VSS

VSS

VSS

Pin alignment of this product

15 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

3.2. Pin List (Ball number order)

Table 3.1 shows a pin list.

Table 3.1 Pin List (Ball number order)

Ball

Number

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

C1

C2

C3

C4

2016-07-19

Pin name

VSS

EMMC0_DAT0

EMMC0_DAT4

EB0_CE3_N

EB0_CLKO

EB0_ADD2

EB0_ADD11

EB0_ADD14

EB0_ADD19

EB0_ADD24

EB0_DAT1

EB0_DAT5

EB0_DAT9

EB0_DAT10

EB0_DAT11

EB0_DAT13

EB0_DAT14

EB0_DAT15

VSS

EMMC0_CLK

EMMC0_DAT1

EMMC0_DAT5

EB0_CE2_N

EB0_OE_N

EB0_ADD3

EB0_ADD9

EB0_ADD13

EB0_ADD18

EB0_ADD23

EB0_DAT0

EB0_DAT4

EB0_DAT8

EB0_DAT12

EB0_DAT16

EB0_DAT18

EB0_DAT19

EB0_DAT20

EB0_DAT22

EMMC0_CLKB

EMMC0_DAT2

EMMC0_DAT6

EB0_CE1_N

Power supply

of pin

—

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_SD1

VDD1V8_3V3_SD1

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

—

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_SD1

VDD1V8_3V3_SD1

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_SD1

Ball

Number

C6

C7

C9

C10

C11

C13

C14

C15

C16

C17

C18

C19

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

E1

E2

E3

E4

E5

E6

E7

E8

E9

E11

E12

16 / 64

1/4

Pin Name

EB0_ADD4

EB0_ADD8

EB0_ADD17

EB0_ADD22

EB0_AVD_N

EB0_DAT6

EB0_DAT17

EB0_DAT23

EB0_DAT24

EB0_DAT25

EB0_DAT26

EB0_DAT27

EMMC0_CMD

EMMC0_DAT3

EMMC0_DAT7

EB0_CE0_N

EB0_ADD1

EB0_ADD6

EB0_ADD7

EB0_ADD12

EB0_ADD16

EB0_ADD21

EB0_ADD26

EB0_DAT3

EB0_DAT7

EB0_DAT21

EB0_DAT28

EB0_DAT30

EB0_DAT29

EB0_DAT31

EB0_WE_N

SD0_DAT3

SD0_DAT2

SD0_DAT1

EB0_CLKI

EB0_ADD0

EB0_ADD5

EB0_ADD10

EB0_ADD15

EB0_ADD20

EB0_ADD25

EB0_DAT2

Power supply

of pin

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_EMMC

VDD1V8_3V3_SD1

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD1V8_3V3_SD0

VDD1V8_3V3_SD0

VDD1V8_3V3_SD0

VDD1V8_3V3_SD1

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

Rev. 1.6

TZ2100 Series

Technical Data Sheet

Table 3.1 Pin List (Ball number order) 2/4

E15

E16

E18

EB0_BE2_N

EB0_BE0_N

EB0_BE1_N

E19

EB0_BE3_N

Power supply

Ball

Number

of pin

VDD3V3_PL_EBUS H15

VDD3V3_PL_EBUS H16

VDD3V3_PL_EBUS H18

VDD3V3_PL_EBUS

H19

F1

F2

F3

F4

F5

SD0_DAT0

SD0_CMD

SD0_CLKB

SD0_CLK

GPIO0_15

VDD1V8_3V3_SD0

VDD1V8_3V3_SD0

VDD1V8_3V3_SD0

VDD1V8_3V3_SD0

VDD3V3_PL_I2C

F15

GPIO1_1

VDD3V3_PL_EBUS J7

F16

F17

F18

F19

G1

G2

G3

G4

G5

GPIO1_0

EB0_WAIT_N

XIN_32K

XOUT_32K

GPIO0_16

GPIO0_17

GPIO0_19

GPIO0_20

GPIO0_18

VDD1V8_3V3_EMM

C

VDD1V8_3V3_EMM

C

VDD1V8_3V3_SD1

VDD1V8_3V3_SD1

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PB

BAK_ISOEN_N

DBG_TRST_N

DBG_TMS

DBG_TDI

DBG_TDO

GPIO0_21

GPIO0_22

GPIO0_24

GPIO0_23

VDD1V8_3V3_SD0

VSS

VDDC_PA

VSS

VDDC_PA

VSS

VDD3V3_PB

VDD3V3_PL_EBUS

VDD3V3_PL_EBUS

VDD3V3_PB

VDD3V3_PB

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

Ball

Pin Name

Number

G7

G8

G9

G10

G11

G12

G13

G15

G16

G17

G18

G19

H1

H2

H4

H5

H7

H8

H9

H10

H11

H12

H13

2016-07-19

—

—

—

—

—

—

VDD3V3_PB

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

—

—

—

—

—

Pin Name

Power supply

of pin

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

J8

J9

J10

J11

J12

J13

J15

J16

J17

DBG_TCK

LOWPWR

SYS_WAKEUP

WDT_RSTOUT_

N

GPIO0_25

GPIO0_26

GPIO0_27

GPIO0_29

GPIO0_28

VDD1V8_3V3_S

D0

VDDC_PA

VSS

VSS

VSS

VDDC_PA

VDD3V3_PA

SYS_RESET_N

DBG_SRST_N

VSS

J18

GPIO0_2

VDD3V3_PA

J19

GPIO0_1

VDD3V3_PA

K1

K2

K3

K4

K5

K7

K8

K9

K10

K11

K12

K13

K15

K16

K17

K18

K19

L1

L2

L4

L5

GPIO0_30

GPIO0_31

SPIB0_CLK

SPIB0_IO1

SPIB0_IO0

VDD3V3_PL_I2C

VSS

VSS

VSS

VSS

VSS

VDD3V3_PA

GPIO0_3

GPIO0_0

POR_OUT_N

XIN

XOUT

SPIB0_IO2

SPIB0_IO3

SPIB0_CS0_N

SPIB0_CS1_N

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

—

—

—

—

—

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

VDD3V3_PA

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

J1

J2

J3

J4

J5

17 / 64

VDD3V3_PA

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

—

—

—

—

—

VDD3V3_PA

VDD3V3_PA

—

Rev. 1.6

TZ2100 Series

Technical Data Sheet

Table 3.1 Pin List (Ball number order) 3/4

Ball

Number

L7

L8

L9

L10

L11

L12

L13

L16

L17

L18

L19

M1

M2

M3

M4

M5

M7

M8

M9

M10

M11

M12

M13

M15

M16

M17

M18

M19

N1

N2

N3

N4

N5

N7

N8

N9

N10

N11

N12

N13

N16

N17

2016-07-19

Pin Name

VDD3V3_PL_I2C

VDDC_PA

VSS

VSS

VSS

VDDC_PA

VDDPLL1

PD_BGR33

PD_POR33

VDD3V3_USB

VDD3V3_USB

BOOTSEL0

BOOTSEL1

BOOTSEL2

BOOTSEL3

BOOTSEL4

VDDC_PA

VSS

VDDC_PA

VSS

VDDC_PA

VSS

VDDPLL0

USB0_REXT

USB0_CLK

USB0_VBUS

USB0_DM

USB0_DP

BOOTSEL5

UA0_RXD

UA0_TXD

GPIO0_10

GPIO0_11

VSS

VDDC_PA

VDD1V1_DDR

VDD1V1_DDR

VSS

VDDC_PA

VDDPLL2

VSSUSB

USB0_TEST

Power supply

of pin

—

—

—

—

—

—

—

—

—

—

—

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

—

—

—

—

—

VDD3V3_USB

VDD3V3_USB

VDD3V3_USB

VDD3V3_USB

VDD3V3_USB

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

—

—

—

—

—

—

VDD3V3_USB

Ball

Number

N18

N19

P1

P2

P4

P5

P7

P8

P9

P10

P11

P12

P13

P16

P17

P18

P19

R1

R2

R3

R4

R5

R16

R17

R18

R19

T1

T2

T3

T4

T6

T7

T8

T9

T10

T11

T12

T13

T15

T16

T17

T18

18 / 64

Pin Name

VSSUSB

VSSUSB

GPIO0_13

GPIO0_14

I2C0_SDA

GPIO0_12

DDR0_VREF

VSS

VDD_DDRIO

VDD_DDRIO

DDR0_ZQ

VPGM

VDD1V1_DDRPLL

VDD3V3_ADC

VSSADC

SAD0_DIN2

SAD0_DIN3

I2C0_SCL

GPIO0_4

GPIO0_5

GPIO0_6

GPIO0_7

VDD3V3_ADC

VSSADC

SAD0_DIN0

SAD0_DIN1

GPIO0_8

GPIO0_9

VSS

DDR0_DQ12

DDR0_DQ10

DDR0_DQ8

DDR0_DQ0

DDR0_DQ6

DDR0_RAS_N

DDR0_WE_N

DDR0_BA2

DDR0_CA0

VSS

VSS

VSS

VSS

Power supply

of pin

—

—

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD_DDRIO

—

—

—

VDD_DDRIO

—

—

—

—

VDD3V3_ADC

VDD3V3_ADC

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

—

VDD3V3_ADC

VDD3V3_ADC

VDD3V3_PL_I2C

VDD3V3_PL_I2C

—

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

—

—

—

—

Rev. 1.6

TZ2100 Series

Technical Data Sheet

Table 3.1 Pin List (Ball number order) 4/4

Ball

Pin Name

Number

T19

U1

U2

U3

U4

U5

U6

U7

U8

U9

U10

U11

U12

U13

U14

U15

U16

U17

U18

U19

V1

V2

V3

V4

V5

V6

V7

V8

V9

VSS

DDR0_DQ11

VSS

DDR0_DM1

VSS

DDR0_DQ14

VSS

DDR0_DM0

DDR0_DQ2

DDR0_DQ4

DDR0_CAS_N

DDR0_ODT

DDR0_BA0

DDR0_CA3

DDR0_CA2

DDR0_CA9

DDR0_CA13

VSS

DDR0_CK_P

VSS

DDR0_DQ13

DDR0_DQ15

VSS

DDR0_DQS_N1

VSS

DDR0_DQS_P0

VSS

DDR0_DQ3

DDR0_DQ5

2016-07-19

Power supply

of pin

—

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

VDD_DDRIO

Ball

Number

V10

V11

V12

V13

V14

V15

V16

V17

V18

V19

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12

W13

W14

W15

W16

W17

W18

W19

19 / 64

Pin Name

DDR0_CS_N

DDR0_CA15

DDR0_CA8

DDR0_RESET_N

DDR0_CA5

DDR0_CA7

DDR0_BA1

VSS

DDR0_CK_N

VSS

VSS

DDR0_DQ9

VSS

DDR0_DQS_P1

VSS

DDR0_DQS_N0

VSS

DDR0_DQ1

DDR0_DQ7

DDR0_CKE

DDR0_CA10

DDR0_CA6

DDR0_CA11

DDR0_CA14

DDR0_CA4

DDR0_CA1

DDR0_CA12

VSS

VSS

Power supply

of pin

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

—

VDD_DDRIO

—

—

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

—

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

VDD_DDRIO

—

—

Rev. 1.6

TZ2100 Series

Technical Data Sheet

3.3. Signal description (in order of pin function)

Some of pins are assigned multiple functions with this product. To define a function on a pin, setting appropriate

pin configuration registers is required after booting up this product. The setting needs to be done with care since

some of the configuration bits may affect multiple different pins in one bit at once.

IDX

Index by

each

function

Signal

Signal name

In / Out

Description

IO's direction Description

or attribute

of signal

Pin share

"yes" means that multiple functions are

signed to this pin

According to the above table, tables shown in 3.3.1 or afterwards show signal descriptions by function group. The

input/output columns may describe "Analog," "Power" and "GND."

Clock Sources and Reset

IDX

Signal name

In / Out

1

XIN

In

2

XOUT

3

XIN_32K

In

4

XOUT_32K

IO

5

6

7

8

9

10

11

SYS_RESET_N

POR_OUT_N

WDT_RSTOUT_N

BAK_ISOEN_N

DBG_SRST_N

SYS_WAKEUP

LOWPWR

In

Out

Out

In

In

In

Out

Out

Description

Resonator input for the system clock (24 MHz)

Oscillator Input for the system clock (24 MHz)

Resonator output for the system clock (24 MHz)

Resonator input for the RTC (32.768 kHz)

Resonator output for the RTC (32.768 kHz)

Oscillator Input for the RTC (32.768 kHz)

System reset input

Power on reset output

Watch dog timer reset output

Backup power domain enable input

CPU (without debug resource) system reset input

Wake up interrupt input

Low power enable output

DDR3/DDR3L Memory Interface

IDX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

Signal name

DDR0_CK_P

DDR0_CK_N

DDR0_CKE

DDR0_CA15

DDR0_CA14

DDR0_CA13

DDR0_CA12

DDR0_CA11

DDR0_CA10

DDR0_CA9

DDR0_CA8

DDR0_CA7

DDR0_CA6

DDR0_CA5

DDR0_CA4

DDR0_CA3

DDR0_CA2

DDR0_CA1

2016-07-19

In / out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Description

DDR3/DDR3L differential clock output (plus)

DDR3/DDR3L differential clock output (minus)

DDR3/DDR3L clock enable

DDR3/DDR3L address 15

DDR3/DDR3L address 14

DDR3/DDR3L address 13

DDR3/DDR3L address 12

DDR3/DDR3L address 11

DDR3/DDR3L address 10

DDR3/DDR3L address 9

DDR3/DDR3L address 8

DDR3/DDR3L address 7

DDR3/DDR3L address 6

DDR3/DDR3L address 5

DDR3/DDR3L address 4

DDR3/DDR3L address 3

DDR3/DDR3L address 2

DDR3/DDR3L address 1

20 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

IDX

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Signal name

DDR0_CA0

DDR0_BA2

DDR0_BA1

DDR0_BA0

DDR0_RAS_N

DDR0_CAS_N

DDR0_DQ15

DDR0_DQ14

DDR0_DQ13

DDR0_DQ12

DDR0_DQ11

DDR0_DQ10

DDR0_DQ9

DDR0_DQ8

DDR0_DQ7

DDR0_DQ6

DDR0_DQ5

DDR0_DQ4

DDR0_DQ3

DDR0_DQ2

DDR0_DQ1

DDR0_DQ0

DDR0_DQS_P1

DDR0_DQS_P0

DDR0_DQS_N1

DDR0_DQS_N0

DDR0_DM1

DDR0_DM0

DDR0_CS_N

DDR0_WE_N

DDR0_VREF

DDR0_ODT

DDR0_RESET_N

DDR0_ZQ

In / out

Out

Out

Out

Out

Out

Out

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

Out

Out

Analog

Out

Out

Analog

Description

DDR3/DDR3L address 0

DDR3/DDR3L bank address 2

DDR3/DDR3L bank address 1

DDR3/DDR3L bank address 0

DDR3/DDR3L row address selection signal

DDR3/DDR3L column address selection signal

DDR3/DDR3L data bus 15

DDR3/DDR3L data bus 14

DDR3/DDR3L data bus 13

DDR3/DDR3L data bus 12

DDR3/DDR3L data bus 11

DDR3/DDR3L data bus 10

DDR3/DDR3L data bus 9

DDR3/DDR3L data bus 8

DDR3/DDR3L data bus 7

DDR3/DDR3L data bus 6

DDR3/DDR3L data bus 5

DDR3/DDR3L data bus 4

DDR3/DDR3L data bus 3

DDR3/DDR3L data bus 2

DDR3/DDR3L data bus 1

DDR3/DDR3L data bus 0

DDR3/DDR3L differential data strobe plus 1

DDR3/DDR3L differential data strobe plus 0

DDR3/DDR3L differential data strobe minus 1

DDR3/DDR3L differential data strobe minus 0

DDR3/DDR3L write data byte mask 1

DDR3/DDR3L write data byte mask 0

DDR3/DDR3L chip select

DDR3/DDR3L write enable

DDR3/DDR3L DQ reference voltage

DDR3/DDR3L ODT enable

DDR3/DDR3L reset output

DDR3/DDR3L reference resister input

Connect a bridge terminal resistor (recommended value: 220 Ω) between the DDR0_CK_P and the DDR0_CK_N.

2016-07-19

21 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

SPI Flash Memory Controller Interface

IDX

1

2

3

4

5

6

7

Signal name

SPIB0_CLK

SPIB0_IO0

SPIB0_IO1

SPIB0_IO2

SPIB0_IO3

SPIB0_CS0_N

SPIB0_CS1_N

In / out

Out

IO

IO

IO

IO

Out

Out

Description

SPIB0 clock output

SPIB0 serial data output

SPIB0 serial data input

SPIB0 quad data 2

SPIB0 quad data 3

SPIB0 chip select 0

SPIB0 chip select 1

Pin

share

yes

yes

yes

yes

yes

yes

yes

eMMC / SD card / SDIO Interfaces

IDX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

Signal name

SD0_CD

SD0_WP

SD0_V18EN

SD0_POWER

SD0_CLK

SD0_CLKB

SD0_CMD

SD0_DAT0

SD0_DAT1

SD0_DAT2

SD0_DAT3

SD1_CD

SD1_WP

SD1_V18EN

SD1_POWER

SD1_CLK

SD1_CLKB

SD1_CMD

SD1_DAT0

SD1_DAT1

SD1_DAT2

SD1_DAT3

EMMC0_CLK

EMMC0_CLKB

EMMC0_CMD

EMMC0_DAT0

EMMC0_DAT1

EMMC0_DAT2

EMMC0_DAT3

EMMC0_DAT4

EMMC0_DAT5

EMMC0_DAT6

EMMC0_DAT7

2016-07-19

In / out

In

In

Out

Out

Out

In

IO

IO

IO

IO

IO

In

In

Out

Out

Out

In

IO

IO

IO

IO

IO

Out

In

IO

IO

IO

IO

IO

IO

IO

IO

IO

Description

SD0 card detection

SD0 card write protection

SD0 card 1.8 V/3.3 V control

SD0 card power supply voltage control

SD0 clock output

SD0 timing control clock B

SD0 command

SD0 data 0

SD0 data 1

SD0 data 2

SD0 data 3

SD1 card detection

SD1 card write protection

SD1 card 1.8 V/3.3 V control

SD1 card power supply voltage control

SD1 clock output

SD1 timing control clock B

SD1 command

SD1 data 0

SD1 data 1

SD1 data 2

SD1 data 3

eMMC clock output

eMMC timing control clock B

eMMC command

eMMC data 0

eMMC data 1

eMMC data 2

eMMC data 3

eMMC data 4

eMMC data 5

eMMC data 6

eMMC data 7

22 / 64

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

Rev. 1.6

TZ2100 Series

Technical Data Sheet

External BUS interface

IDX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

Signal name

EB0_ADD26

EB0_ADD25

EB0_ADD24

EB0_ADD23

EB0_ADD22

EB0_ADD21

EB0_ADD20

EB0_ADD19

EB0_ADD18

EB0_ADD17

EB0_ADD16

EB0_ADD15

EB0_ADD14

EB0_ADD13

EB0_ADD12

EB0_ADD11

EB0_ADD10

EB0_ADD9

EB0_ADD8

EB0_ADD7

EB0_ADD6

EB0_ADD5

EB0_ADD4

EB0_ADD3

EB0_ADD2

EB0_ADD1

EB0_ADD0

EB0_DAT31

EB0_DAT30

EB0_DAT29

EB0_DAT28

EB0_DAT27

EB0_DAT26

EB0_DAT25

EB0_DAT24

EB0_DAT23

EB0_DAT22

EB0_DAT21

EB0_DAT20

EB0_DAT19

EB0_DAT18

EB0_DAT17

EB0_DAT16

EB0_DAT15

EB0_DAT14

EB0_DAT13

EB0_DAT12

EB0_DAT11

EB0_DAT10

EB0_DAT9

EB0_DAT8

2016-07-19

In / out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

Description

EBUS address 26

EBUS address 25

EBUS address 24

EBUS address 23

EBUS address 22

EBUS address 21

EBUS address 20

EBUS address 19

EBUS address 18

EBUS address 17

EBUS address 16

EBUS address 15

EBUS address 14

EBUS address 13

EBUS address 12

EBUS address 11

EBUS address 10

EBUS address 9

EBUS address 8

EBUS address 7

EBUS address 6

EBUS address 5

EBUS address 4

EBUS address 3

EBUS address 2

EBUS address 1

EBUS address 0

EBUS data 31

EBUS data 30

EBUS data 29

EBUS data 28

EBUS data 27

EBUS data 26

EBUS data 25

EBUS data 24

EBUS data 23

EBUS data 22

EBUS data 21

EBUS data 20

EBUS data 19

EBUS data 18

EBUS data 17

EBUS data 16

EBUS data 15

EBUS data 14

EBUS data 13

EBUS data 12

EBUS data 11

EBUS data 10

EBUS data 9

EBUS data 8

23 / 64

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

Rev. 1.6

TZ2100 Series

Technical Data Sheet

IDX

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

Signal name

EB0_DAT7

EB0_DAT6

EB0_DAT5

EB0_DAT4

EB0_DAT3

EB0_DAT2

EB0_DAT1

EB0_DAT0

EB0_CE3_N

EB0_CE2_N

EB0_CE1_N

EB0_CE0_N

EB0_BE3_N

EB0_BE2_N

EB0_BE1_N

EB0_BE0_N

EB0_AVD_N

EB0_WE_N

EB0_OE_N

EB0_WAIT_N

EB0_CLKI

EB0_CLKO

In / out

IO

IO

IO

IO

IO

IO

IO

IO

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

In

In

Out

Description

EBUS data 7

EBUS data 6

EBUS data 5

EBUS data 4

EBUS data 3

EBUS data 2

EBUS data 1

EBUS data 0

EBUS chip enable 3

EBUS chip enable 2

EBUS chip enable 1

EBUS chip enable 0

EBUS byte enable [31:24]

EBUS byte enable [23:16]

EBUS byte enable [15:8]

EBUS byte enable [7:0]

EBUS address validity detection output

EBUS write enable

EBUS output enable

EBUS wait input

EBUS clock input

EBUS clock

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

UART interface

IDX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Signal name

UA0_RXD

UA0_TXD

UA1_RXD

UA1_TXD

UA1_CTS_N

UA1_RTS_N

UA1_EXCLK

UA2_RXD

UA2_TXD

UA2_CTS_N

UA2_RTS_N

UA3_RXD

UA3_TXD

UA3_CTS_N

UA3_RTS_N

2016-07-19

In / out

In

Out

In

Out

In

Out

In

In

Out

In

Out

In

Out

In

Out

Description

UART0 serial data input

UART0 serial data output

UART1 serial data input

UART1 serial data output

UART1 CTS input

UART1 RTS output

UART1 external clock input

UART2 serial data input

UART2 serial data output

UART2 CTS input

UART2 RTS output

UART3 serial data input

UART3 serial data output

UART3 CTS input

UART3 RTS output

24 / 64

Pin

share

—

—

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

Rev. 1.6

TZ2100 Series

Technical Data Sheet

I2C bus interface

IDX

1

2

3

4

5

6

7

8

Signal name

I2C0_SDA

I2C0_SCL

I2C1_SDA

I2C1_SCL

I2C2_SDA

I2C2_SCL

I2C3_SDA

I2C3_SCL

Note:

2016-07-19

In / out

IO

IO

IO

IO

IO

IO

IO

IO

Description

I2C0 data

I2C0 clock

I2C1 data

I2C1 clock

I2C2 data

I2C2 clock

I2C3 data

I2C3 clock

Pin

share

—

—

yes

yes

yes

yes

yes

yes

Each pin has open drain type interface.

25 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

SPI Interfaces (for Master Controller)

IDX

1

2

3

4

5

6

7

8

Signal name

SPIM0_CLK

SPIM0_DI

SPIM0_DO

SPIM0_CS_N

SPIM1_CLK

SPIM1_DI

SPIM1_DO

SPIM1_CS_N

Note:

In / out

Out

In

Out

Out

Out

In

Out

Out

Description

SPIM0 clock output

SPIM0 serial data input

SPIM0 serial data output

SPIM0 chip select

SPIM1 clock output

SPIM1 serial data input

SPIM1 serial data output

SPIM1 chip select

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

The SPIM0 and the SPITX0 can NOT be used at the same time in an application, the SPIM1 and the

SPITX1 can NOT be used at the same time, too.

SPI Interfaces (Dedicated for Transmission)

IDX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

Signal name

SPITX0_CLK

SPITX0_DO

SPITX0_CS_N

SPITX1_CLK

SPITX1_DO

SPITX1_CS_N

SPITX2_CLK

SPITX2_DO

SPITX2_CS_N

SPITX3_CLK

SPITX3_DO

SPITX3_CS_N

SPITX4_CLK

SPITX4_DO

SPITX4_CS_N

SPITX5_CLK

SPITX5_DO

SPITX5_CS_N

SPITX6_CLK

SPITX6_DO

SPITX6_CS_N

Note:

2016-07-19

In / out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Out

Description

SPITX0 clock output

SPITX0 data output

SPITX0 chip select

SPITX1 clock output

SPITX1 data output

SPITX1 chip select

SPITX2 clock output

SPITX2 data output

SPITX2 chip select

SPITX3 clock output

SPITX3 data output

SPITX3 chip select

SPITX4 clock output

SPITX4 data output

SPITX4 chip select

SPITX5 clock output

SPITX5 data output

SPITX5 chip select

SPITX6 clock output

SPITX6 data output

SPITX6 chip select

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

yes

The SPIM0 and the SPITX0 can NOT be used at the same time in an application. The SPIM1 and the

SPITX1 can NOT be used at the same time, too.

26 / 64

Rev. 1.6

TZ2100 Series

Technical Data Sheet

SPI Interface (for Slave Controller)

IDX

Signal name

1

2

3

4

SPIS0_CLK

SPIS0_DI

SPIS0_DO

SPIS0_CS_N

Note:

In / out

In

In

Out

In

Description

SPIS0 clock input

SPIS0 serial data input

SPIS0 serial data output

SPIS0 chip select

Pin

share

yes

yes

yes

yes

Select one of pin combinations J5/J3/K1/J4 or H1/G3/G4/H2 in an application.

USB2.0 Host or Device Interface

IDX

1

2

3

4

Signal name

USB0_DP

USB0_DM

USB0_REXT

USB0_VBUS

5

USB0_CLK

6

USB0_TEST

Note 1:

In / out

IO

IO

Analog

Analog

In

Analog

Description

USB port I/O data (DP)

USB port I/O data (DM)

to connect an external resister (Note 1)

VBUS voltage detection (for device mode)

Input to the clock generator for USB (12 MHz)

* option for external oscillator connection

Test pin

Connect to GND with 174 Ω (±1%) resistor.

Ethernet MAC Interface

IDX Signal name

1

2

3

4

5

6

7

8

9

ETH0_TXD0

ETH0_TXD1

ETH0_TXEN

ETH0_RXD0

ETH0_RXD1

ETH0_CRSDV

ETH0_MDC

ETH0_MDIO

ETH0_REFCLK

2016-07-19

In / out

Out

Out

Out

In

In

In

Out

IO

In

Description

Ethernet RMII transmission data 0

Ethernet RMII transmission data 1

Ethernet RMII transmission enable

Ethernet RMII receiving data 0

Ethernet RMII receiving data 1

Ethernet RMII carrier sense / receiving data valid

Ethernet management data clock

Ethernet management data I/O

Ethernet RMII reference clock

27 / 64

Pin

share

yes

yes

yes

yes

yes

yes

yes

yes

yes

Rev. 1.6

TZ2100 Series

Technical Data Sheet

Camera Input

IDX

1

2

3

4

5

6

7

8

9

10

11

Signal name

CAM0_CLK

CAM0_VSYNC

CAM0_HSYNC

CAM0_DATA0

CAM0_DATA1

CAM0_DATA2