On-chip negative bias temperature instability sensor using slew rate

advertisement

On-chip Negative Bias Temperature Instability Sensor using Slew Rate

Monitoring Circuitry

Amlan Ghosh, *Rahul M. Rao, Richard B. Brown and *Ching-Te Chuang

University of Utah, Salt Lake City, UT 84112

*IBM Technical Contact - IBM TJ Watson Research Center, Yorktown Heights, NY 10598

{aghosh, brown@eng.utah.edu}, *{raorahul@us.ibm.com, ChingTe.Chuang@gmail.com}

Abstract

Negative Bias temperature Instability (NBTI) has become

one of the major sources of degradation in scaled PMOS

devices, affecting the yield and reliability of circuits as well

as the power and performance. As the oxide thickness

decreases with each technology generation, increased oxide

electric field and higher current densities degrade the

performance and lifetimes of devices (especially PMOS) due

to stress. Hence, it has become necessary to understand and

accurately measure the effect of NBTI in PMOS devices.

This paper proposes detection of PMOS threshold voltage

degradation using on-chip slew-rate monitor circuitry. The

increase in the PMOS threshold voltage is sensed with high

resolution using the change of rise time in a stressed ring

oscillator. Simulation results are shown for the detection

circuitry in a 65nm IBM CMOS process.

1. Introduction

With technology scaling, reliability has become a

serious challenge; the effects of process parameter variation

and degradation due to phenomena such as bias

temperature instability and hot carrier injection must be

mitigated. These sources of variation have caused the delay

and leakage of high-performance microprocessors to vary

significantly from their nominal values. Because supply

voltages have not been scaled as fast as device dimensions,

transistors see higher current densities and higher

temperatures, which aggravate the device degradation and

shorten lifetimes. At the same time, scaling of oxide

thickness has increased electric fields. The higher

temperatures and electric fields cause PMOS VT to

gradually shift to more negative values through negative

bias temperature instability (NBTI); this has become a

major issue in circuit lifetime for modern processes [1] –

[3].

NBTI is normally caused by the dissociation of Si-H

bonds along the silicon-oxide interface, and is more

problematic for PMOS than NMOS devices. In a PMOS

device, the holes from the inversion layers can enter into

the oxide through a tunneling process and interact with SiH bonds. This interaction may weaken the bonds, which

can break due to thermal excitation or otherwise. The

released Hydrogen (H) atoms move away from the

interface and generate Si dangling-bond interface traps [4].

The number of interface traps (NIT) is identical to the

displaced neutral H and is a strong function of gate voltage

(VG) and oxide electric field (EOX) [5].

The shift in

threshold voltage (∆VT) is proportional to the number of

interface traps (NIT). The impact of NBTI on PMOS also

depends on the duration of time the device is stressed vs.

relaxed [6].

There is a great need for accurate sensors to better

characterize the effects of NBTI on devices. With reliable

models of NBTI, circuits could be designed to minimize its

lifetime-limiting degradation. An efficient sensor might

even make it practical to correct for NBTI-induced

threshold shifts in certain sensitive circuits.

A few NBTI measurement techniques have been

proposed in recent years. Most of them require highly

specialized equipment and very precise control during

measurement. An on-the-fly measurement technique has

been described, which holds the gate voltage constant

during both stress and measurement to avoid recovery

before and during the characterization steps [7]-[8]. This

method uses drain current, threshold voltage and

transconductance as the extracted parameters. It requires

very careful measurement of every transistor current.

Another proposed on-chip NBTI degradation sensor uses

the beat frequency of two ring oscillators [9]. This

technique is useful because of its high resolution. A phase

comparator measures the difference between a stressed and

a reference ring oscillator. A limitation of this technique is

that the degradation information from the stressed ring

oscillator delay may be adulterated by some parameter shift

in the NMOS devices. Another technique has been

proposed that uses multiple delay-lock loops (DLLs) [10].

It requires significant area, and the output cannot be used

directly to drive any compensation scheme.

The scheme proposed in this paper is based upon

measuring the slew of certain signals in a circuit. This

approach is particularly area-efficient, and provides an

output voltage that is an indication of the extent of NBTI

degradation and can be used to directly drive a

compensation circuit. In Section 2, the basic NBTI

detection scheme is presented. Section 3 discusses the

design and implementation of the proposed circuits.

Simulation results are presented in Section 4, and

concluding remarks are made in Section 5.

2. NBTI Detection

The frequency of a signal in a CMOS circuit depends

upon the combined effects of rise and fall delay, which are

governed by the drive strengths of the PMOS and NMOS

networks. Hence, using frequency degradation of a stressed

circuit as an indicator of NBTI may not be a true

representation of the PMOS threshold voltage shift, since

the frequency information also includes the effects of

Positive Bias Temperature Instability (PBTI) in the NMOS

devices. The rise slew of a pulse is a strong function of the

drive strength of the PMOS circuit. Hence, the VTH shift of

a stressed PMOS transistor will be reflected in a change in

rise slew of the output signal, which is measured in the

proposed scheme. This approach decouples any effects due

to the NMOS network.

A basic block diagram of the proposed NBTI monitor

is shown in Fig.1. It consists of two ring oscillators, two

slew rate monitors, and a charge pump (CP). One ring

oscillator (Str ROSC in Fig.1) is stressed by applying a

higher supply voltage during the NBTI stress period.

Another ring oscillator is driven with the nominal 1V

supply. The en signal allows both of the oscillators to freerun during measurement periods. The rise slew of the Ref

ROSC and Str ROSC are measured by slew rate monitors

A and B [11]. Both of the slew monitors generate two

trains of pulses which are fed to charging and discharging

input lines of the charge pump. The output of the charge

pump indicates the difference in PMOS threshold voltage

between the two ring oscillators due to the stress voltage.

This output pulse train B1 charges the capacitor C

from voltage level ‘a’ to level ‘b,’ and output pulse train B2

discharges it back to final level ‘c’. Thus, the final output

level (c in Fig. 2) is proportional to the difference of rise

slews of the Pulses Under Test (PUT) from Str ROSC and

Ref ROSC.

A reset circuit sets the voltage level ‘a’ to VDD/2 before

the arrival of the en signal for the next measurement. By

setting the initial capacitor voltage to 500mV, the circuit

can determine the sign as well as the absolute magnitude of

the difference between the slews of the two ring oscillators.

A calibration of the two oscillators must be done before the

Str ROSC is stressed. Because the pre-stress slew of the

Str ROSC can be faster than that of the Ref ROSC, and will

certainly be slower post-stress, it is important for the circuit

to be able to detect differences of both polarities.

Fig. 2. Principle of NBTI detection circuit using slew

rate monitors.

3. Implementation of Proposed Scheme

Fig. 1. Block diagram of NBTI monitor.

The basic operation of the NBTI monitoring circuit is

shown in Fig 2. A1 and A2 are trains of pulses from the

stressed and reference ring oscillators. They consist of N

pulses, P1, P2 to PN. The number of pulses, N, can be

adjusted depending upon the required output sensitivity.

The en signal starts the ring oscillators in such a way that

they run 180o out of phase. Each slew rate monitor

generates pulses corresponding to each rise slew of P1, P2,

through PN. PR1, PR2, PR3, to PRN are the pulses

corresponding to the rise slew of Str. ROSC and Ref.

ROSC output signal (represented as B1 and B2 signal).

Pulse widths of PRi are dependent on the rise slew of P1, P2

to PN. As can be seen, PR1, PR2, PR3, PRN in B1 never

overlap with PR1, PR2, PR3, PRN in B2 during the

measurement period.

The design of slew rate monitor and charge pump are

described in this section.

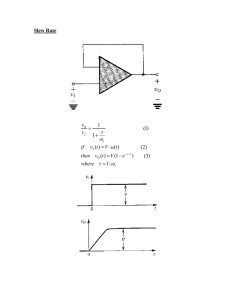

3.1 Slew Rate Monitor

Measuring the slew-rate of a gigahertz signal from a

free-running oscillator requires high-speed and precise

dynamic apparatus with sensitivity in the pico-second

range. The slew rate monitor block has been designed to

measure rise or fall slew of signals in IBM’s 65nm PD/SOI

CMOS process.

A simplified block diagram of the slew-rate monitor is

shown in Fig. 3. The pulse under Test (PUT) is connected

to two comparators, A and B. Comparator-A, composed

primarily of thick-oxide, long-channel NMOS devices,

compares the PUT level to a reference voltage equal to

80% of the supply voltage (VDD) [12]-[13]. Similarly,

Comparator-B, composed primarily of thick-oxide longchannel PMOS devices, compares the PUT level to a

reference voltage equal to 20% of the supply voltage. The

reference voltages of 20% and 80% were chosen to provide

sufficient noise margin against supply noise on the input

signal. This slew-rate monitor topology is applicable for

any set of two reference voltages. In a low-noise system,

10% to 90% reference voltages could be used in order to

improve the output sensitivity.

The output of one comparator switches before the

output of the other comparator, depending on the slew of

the signal and the direction of transition. Hence, the two

comparators generate two pulses of different width. These

two comparator output signals (U and V in Fig. 3) are fed

to an exclusive-or (XOR) gate that generates two pulses at

its output. The width of the first pulse (R in Fig. 3) is a

direct representation of the rise slew of the input, whereas

the width of second pulse (F in Fig.3) represents the fall

slew. The control logic multiplexes the R and F pulses to

generate two separate pulses PR and PF. The control logic

output is also generated from the input PUT pulse only. PR

and PF are the separated versions of the R and F pulses,

respectively. In this work, we are using PR pulses only as

the output of slew-rate monitor.

reasonably large W/L ratio was chosen for devices P2 and

N2 to obtain a small time-constant, while ensuring that the

integrator output will not saturate to the supply rail. The

final output voltage thus depends upon the difference in

pulse widths of PR from the B1 and B2 signals.

The reset circuit is implemented with a pair of series

connected NMOS devices that charge the output node to

half of the supply rail (500mV), as described earlier. The

Reset is de-asserted just prior to the application of the

enable signal, en of Fig. 2, which starts the next NBTI test.

Fig. 4. Schematic representation of charge pump.

4. Simulation Results

Sensor circuits have been designed and

implemented. Thick oxide devices were used throughout.

The input slew is varied from 25ps to 250ps. The simulated

output of the integrator is plotted in Fig. 5. As can be seen,

the slew-rate monitor exhibits an output sensitivity of

0.42mV/ps.

Fig. 3. Slew rate monitor.

3.2 Charge Pump

A simple charge pump circuit has been designed as

shown in Fig. 4 to change the voltage on a thick-oxide

capacitor. A doubly-balanced current mirror consisting of

appropriately sized P4, N1 and N4 provides identical

current flow through N2 and P2. P3 and N3 act as switches

[14]. The pulse, PR, from the B1 signal of Fig. 2 controls

the UP signal that drives the PMOS switch P3. Thus, for a

time equivalent to the pulse width of PR (see Fig.2), P3 is

on, and current flows from supply to the output node to

charge the capacitance C1. Similarly, pulse PR from the B2

signal of Fig.2 controls the DN signal that drives the

NMOS switch N3. When N3 is on, current flows from

output capacitance C1 to ground through the N3-N2 stack,

thereby discharging the output node in proportion to the

pulse width of PR from B2. The integrating time constant is

dependent upon the capacitance, C1, and the integrating

current, and can be tuned as required, depending on the

difference of input signal pulse widths. In this design, a

Normalized Output Voltage

1.13

1.11

1.09

1.07

1.05

1.03

1.01

0.99

0

50

100

150

200

250

300

Input slew(ps)

Fig. 5. Normalized output voltage of slew rate monitor

with input signal slew.

Output sensitivity is a strong function of the number

of pulses, N, and the integrating constant of the charge

pump (ratio of charging/discharging current to the value of

the output capacitor). Hence, we have investigated the use

of multiple pulses to enhance the sensitivity of the system .

Fig.6 shows the percent change in the output voltage with

percent change in the rise slew of the Str ROSC output

compared to the Ref ROSC output. Different curves

correspond to differnet number of input pulses. N_1

through N_5 in the plot represent the use of 1 to 5 input

pulses in the measurement. Sensitivity of the slew rate

monitor with number of pulses has been shown in Fig.7. As

can be seen, the sensitivity increases almost linearly with

the number of pulses. From this data, one can begin to

optimize the circuit performance and sensitivity.

%change in output voltage

30

20

10

The authors are grateful to IBM for offering

CMOS technology information. Thanks are due to Dr. Fadi

Gebara, Dr. Jae-Jung Kim and Dr. Aditya Bansal for advice

and helpful discussions. This work was supported by IBM

Research, and by the Engineering Research Centers

Program of the National Science Foundation under Award

Number EEC-9986866.

References

0

N_1

-10

N_2

-20

N_3

N_4

-30

N_5

-40

-60

-40

-20

0

20

40

60

%change in input pulse rise time

Fig. 6. Normalized output of slew rate monitor with

number of input pulses.

1.4

1.2

Sensitivity (mV/ps)

6. Acknowledgement

1

0.8

0.6

0.4

0.2

0

0

1

2

3

4

5

6

Number of Input Pulses

Fig.7. Sensitivity of slew rate monitor with number of

input pulses.

5. Conclusion and Future Work

In this work, a precise and area-efficient threshold

voltage degradation monitoring technique has been

proposed and simulated. This on-chip sensing technique

will help researchers to model the negative bias

temperature instability (NBTI) degradation of a PMOS

device more accurately, and hopefully, help the electronics

community avoid the requirement of using larger-width

transistors to mitigate the impact of NBTI.

The NBTI sensor was designed in a 65 nm CMOS

process with two ring oscillators and two slew rate

monitors. The simulation results are presented. As a part of

our continuing work, we will determine the sensitivity of

the NBTI monitor, and fabricate and test the sensing

circuit.

The circuit could potentially be used to extend the

lifetime of circuitry that is particularly sensitive to NBTI,

by using the sensor output signal to drive a compensation

circuit.

[1] V. Huard and M. Denais, “Hole Trapping Effect on

Methodology for DC and AC Negative Bias Temperature

Instability Measurements in PMOS Transistors,”,

IEEE

International Reliability Physics Symposium, pp. 40-45, April

2004.

[2] M. Denais, et al., “New Perspectives on NBTI in Advanced

Technologies: Modelling & Characterization,” European SolidState Device Research Conference, pp. 399-402, September 2005.

[3] R. Vattikonda, W. Wang, Y. Cao, “Modeling and

Minimization of PMOS NBTI Effect for Robust Nanometer

Design,” IEEE Design Automation Conference, pp. 1047-1052,

July 2006.

[4] S. Mahapatra, P. B. Kumar, and M. A. Alam, "Investigation

and Modeling of Interface and Bulk Trap Generation During

Negative Bias Temperature Instability of p-MOSFETs,”, IEEE

Toanscictions on Electronic Devices, pp. 13 1-1379, Septenber

2004.

[5] M. A. Alam and S. Mahapatra, "A Comprehensive Model of

PMOS NBTI Degradation," Jounal of Microelectronics

Reliability, vol. 45, pp. 71-81, August 2004.

[6] S. Kumar, C. Kim, S. Sapatnekar, “An Analytical Model for

Negative Bias Temperature Instability,” IEEE International

Conference on Computer-Aided Design, pp. 205-210 November

2006.

[7] M. Denais, et al., “On-the-fly characterization of NBTI in

ultra-thin gate oxide PMOSFET’s,” IEEE International Electron

Devices Meeting, pp. 109-112, December 2004.

[8] M. Denais, et al., “Paradigm Shift for NBTI Characterization

in Ultra-Scaled CMOS Technologies,” IEEE International

Reliability Physics Symposium, pp. 735-736, March 2006.

[9] T. Kim, et al., “Silicon Odometer: An On-Chip Reliability

Monitor for Measuring Frequency Degradation of Digital

Circuits,” IEEE Symposium on VLSI Circuits, pp.122-123 June

2007.

[10] J. Keane, T. Kim, and C.H. Kim, "An On-chip NBTI Sensor

for Measuring PMOS Threshold Voltage Degradation",

International Symposium on Low Power Electronics and Design,

Aug 2007

[11] A. Ghosh et. al. ,” On-Chip Process Variation Detection

using Slew-Rate Monitoring Circuit in Sub-100nm CMOS

Technology “,IEEE VLSI Design 2008

[12] J. M Rabaey. et. al.., “Digital Integrated Circuits (2nd

Edition)”, 2002

[13] S. Park et. al., “Low-power Transistor-String and new rail-torail comparator in A/D converter”, Proc. of Mid-West Symposium

on Circuits and Systems , Vol 1, pp. 194 - 197 , 1999

[14] R.J. Baker et. al.,”CMOS Circuit Design, layout, and

Simulation: Chap 26”, IEEE Press, 1996.