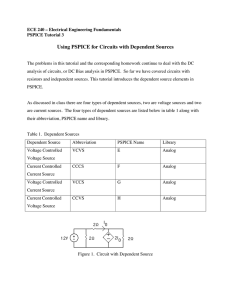

AMPLIFIER WITH A MOSFET. SOURCE FOLLOWER.

advertisement

Experiment 5 AMPLIFIER WITH A MOSFET. SOURCE FOLLOWER. OBJECTIVES. To study the large and small signal behaviour of a MOSFET. To design a current source. To design a common-drain amplifier (or source follower) and to measure its basic parameters. THE DEVICE. In this experiment, students will work with the M4007N n-MOSFET. This transistor has the following parameters: λ = 15 × 10−6 V−1 , threshold voltage Vtho = 0.7 V, transistor width W = 144µm, transistor length L = 8µm and process transconductance parameter kn′ = 33.33 × 10−6 A2 /V. The threshold voltage is controlled by the source-bulk voltage VSB as q q Vth = Vtho + γ[ 2φf + VSB − 2φf ] where 2φf = 0.6 V and γ is the fabrication process parameter. In this experiment, we consider two different values of γ, γ = 0 and γ = 1.8. The PSpice model is .model M4007N nmos(Level=1 Tox=300n KP=33.33u W=144u L=8u VTO= 0.7 +Lambda=15u Cbd=4p Cbs=4p GAMMA=0 (or 1.8)) 5.1. Biasing the MOSFET OBJECTIVES. To bias a transistor with a current mirror. To design a current mirror with n-MOSFETs Figure 5.1: Implementation of a constant-current source I using a current mirror. In this experiment VDD = 15 V and −VSS = −15 V. 1. Theoretical work 1 Consider the current mirror with n-MOSFETs of Figure 5.1. Find the value of the resistance R such that IREF = 1 mA. To do this, use the current-voltage expression for the saturation mode. The transistor Q1 fulfils the saturation condition (VDS > VGS − Vt ) because VDS1 = VGS1 . The transistor Q2 must operate in saturation in order to maintain constant the current I. Do not forget that this current source is designed to operate in an amplifier stage where changes in the value of VDS2 will be present. However, they must not alter the value of the current source. Assume that all the transistors used in the experiment are the same (M4007N). Ignore the Early effect in the theoretical DC calculations. Based on the values of the model parameters, justify that the Early effect can be neglected. Which are the values of VDS1 , VGS1 and VGS2 ? Which is the minimum value of the voltage VD (Figure 5.1) for the transistor Q2 to operate in saturation? 5.2. Common-drain amplifier OBJECTIVES. To design a basic amplifier configuration: the common-drain amplifier. To determine and measure its main parameters. VDD RS vS vi CC1 Q3 CC2 -VSS + RG - vo I -VSS Rin RL Rout Figure 5.2: Source follower amplifier. In this experiment VDD = 15 V, −VSS = −15 V and I = 1 mA. The current source I is created with the current mirror of Figure 5.1. The substrate of all the transistors must be connected to the lowest voltage of the entire circuit to prevent currents from flowing through the substrate. 1. Theoretical work The source follower of Figure 5.2 employs the current source designed in Figure 5.1. It is essential to connect the substrate of all the transistors to the lowest voltage found in the circuit. Otherwise, current would leak through the substrate. Use the following values for the coupling capacitors CC1 = CC2 = 10µF and the load resistance RL = 10 KΩ. DC analysis. In the first place, assume γ = 0. Find VGS3 , VDS3 , the source voltage of the transistor Q3 (VS3 ), VSB3 and the drain-source voltage of the transistor Q2 (VDS2 ). Find all the theoretical values of the variables in Table 5.1. In the second place, consider γ = 1.8. Use the previous value of VSB3 to calculate Vth . Then, recalculate the variables VGS3 , VDS3 and VSB3 . AC analysis. Assuming γ = 0, find the values of the gain voltage Av = vo /vi , the overall gain voltage Avs = vo /vs (consider RS = 1 K Ω), the input resistance Rin and the output resistance Rout . In the small-signal model, assume rO = ∞. (Suggestion: use the 2 T equivalent circuit model). Introduce the results in Table 5.2. Find the maximum possible positive-signal-swing P SSmax and the maximum possible negative-signalswing N SSmax at the source of the transistor Q3. 5.3. MOSFET modelling in PSpice OBJECTIVES. To modify existing PSpice models. To create a small signal model for the MOSFET to be used in PSpice. gmvgs G1 G D + gm ro S Figure 5.3: Small signal model for the n-MOSFET operating in the saturation mode. The Boby effect has not been included (γ = 0 or VSB = 0). G1 is a voltage controlled current source in PSpice where gm is its transconductance. 1. PSpice work. Changing a PSpice model. Draw the circuit of Figure 5.2 using the current source of Figure 5.1 and the values of the components employed in the theoretical part. Use a signal source VSIN with VAMPL = 10 mV and FREQ = 5 KHz. Use the transistor MbreakN and change the parameters of its model. To do this, click with the right bottom of the mouse on the transistor and select Edit PSpice model. Copy the PSpice model of the transistor M4007N defined above. Consider the two cases: γ = 0 and γ = 1.8. Place this transistor in the circuit the times you need. Define a transient analysis in the simulation profile. End the analysis at 1 ms. Place the Voltage Markers at the input (vs and vi ) and output of the circuit and run PSpice. Show the quiescent point of the circuit by selecting Enable Bias Current Display and Enable Bias Voltage Display. Complete the table 5.1. Determine the voltage gains in Spice A/D Lite. To do this open the option Evaluate Measurement and use the expressions vo /vi and vo /vs . Determine the input and output resistances following the procedure described in Experiment 4. Fill in the column PSpice 1 in Table 5.2 with these results. Consider the two cases: γ = 0 and γ = 1.8. 2. PSpice work. Creating your own small-signal model. Consider the small signal model for the n-MOSFET of Figure 5.3. Determine the value of rO and gm assuming the transistor M4007N and the bias point considered in the theoretical calculation with γ = 0. Draw in PSpice the small signal model of Figure 5.3. Load it in a page of a schematic. Subsequently, you can copy and paste it in a different schematic. You can also load the circuit in the library COMPONENTES.olb created in the Experiment 3. 3 Table 5.1: Table to be filled in after the theoretical and PSpice analysis of the circuit in Figure 5.2. Q1 Theory PSpice Q2 Theory PSpice Q3 Theory γ = 0 γ = 1.8 PSpice γ = 0 γ = 1.8 Q1 Q2 Q3 Laboratory Vth (V) VDS (V) VGS (V) VSB (V) ID (mA) If the second option is chosen follow the procedure described in Section 3.1 to define new models and to load them in libraries: Reference = M1N, Implementation name = MOSFET and Part Name = MOSFET. Use three pins named G, S y D. Load the component in the library COMPONENTES.olb, edit the symbol and draw the component. Draw in PSpice the small-signal equivalent circuit of the circuit represented in Figure 5.2. Replace the transistor with the small signal model of Figure 5.3. Use a signal source VSIN with VAMPL = 10 mV and FREQ = 5 KHz. Define a transient analysis in the simulation profile. End the analysis at 1 ms. Place the Voltage Markers at the input (vs and vi ) and output of the circuit and run PSpice. Determine the voltage gains in Spice A/D Lite. To do this open the option Evaluate Measurement and use the expressions vo /vi and vo /vs . Determine the input and output resistances following the procedure described in Experiment 4. Fill in the column PSpice 2 in Table 5.2 with these results. If you observe differences in the results of both models, describe the origin of such differences. 5.4. Laboratory practice Assemble the circuit of Figure 5.2 with commercial resistances close to the ones obtained in the theoretical part. In the Figure 5.4, the transistors and connections of the integrated component 4007 are shown. Before connecting the capacitors measure the drain current, gate-source voltage and drain source voltage in the three transistors. Introduce these values in Table 5.1 . Assemble the rest of the circuit and measure at 5 KHz: 1. The gain voltage Av = vo /vi . 2. The overall gain voltage Avs = vo /vs (consider RS = 1 K Ω). 3. The input resistance Rin 4. The output resistance Rout 5. Complete the Table 5.2 with the results of this experiment. Does the transistor Q3 show the Body effect? 4 Figure 5.4: Scheme with the transistors and connections of the integrated component 4007. Table 5.2: Table to be filled in with the results of this experience. Theory γ=0 Av Avs Ri Ro P SSmax N SSmax Q3 body effect? (Y/N) PSpice 1 γ=0 PSpice 1 γ = 1.8 PSpice 2 γ=0 —— —— —— —— —— —— Laboratory Increase the amplitude of the input signal until the output is saturated in both extremes. This situation defines the maximum allowable positive and negative voltage swings at he output. Which are these voltage swings? What is the origin of this effect? 5