Recommended Paper Format and Guidelines for ICPBAR

advertisement

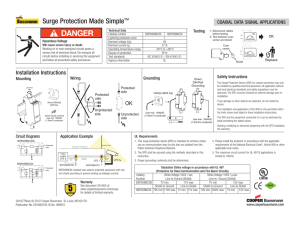

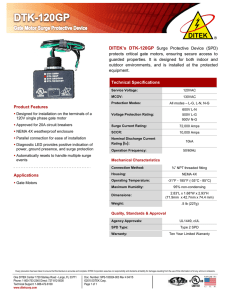

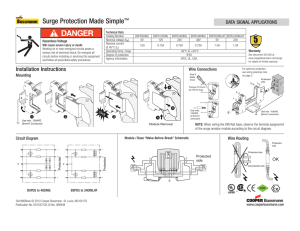

International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 37 The Development of Hybrid Surge Protection Circuit with Effect of Adding a Filter Amizah Md Ariffen , Mohd Zainal Abd Kadir & Wan Fatinhamamah Wan Ahmad Abstract – Surge protective device is a part of internal lightning protection and it crucially to divert the certain amount of surges to the ground before the protected load able to handle. Therefore, this paper studying the enhancement of SPD through the effect of adding a filter in hybrid surge protection circuit using simulation modeling. Ordinarily, filter is used as in eliminating noises in certain application such as electronic apparatus. Furthermore, an experiment testing is pursues in high voltage laboratory for comparison and to validate the simulation. The analysis involved the surge protector Class 3 according to IEC or Category A as referring to IEEE standards with a filter design involving the combination of inductor and capacitor. From this research is found that a significant improvement of about 38% obtain when filter is added in surge protective device. Index Term – surge protector, transient voltage suppressor diode, metal oxide varistor, hybrid protection, surges, EMI filter I. INTRODUCTION Surge protection device (SPD) is widely used these days to withstand surge in power line and telecommunication. Surge suppressors, surge diverters, surge arresters, transient voltage suppressors (TVSS) all are the SPD other names with the similar purpose [1]. SPD can be found from mostly utility type surge arrester to small suppressors install at equipment. The protection provided by SPD is attenuating the transient and their propagation to the ground before entering the protected load. However by installing the SPD cannot resolve all kinds of power system disturbances as notches, sags, harmonic, swells and etc. [2] as in Table I [3]. SPD functioning either divert to ground or clamp into safe level the surge before it impinges on the equipment thru the power system supply and only conduct under the surge condition by lowering its impedance. Hence, the current will past, rather than through the protected equipment [4]. Amizah Md Ariffen is with the School of Electrical System Engineering, Universiti Malaysia Perlis, P.O Box 77, Pejabat Pos Besar, 01000 Kangar, Perlis, Malaysia (e-mail: amizah@unimap.edu.my). Mohd Zainal Abd Kadir was with Faculty of Engineering, Universiti Putra Malaysia 43400 UPM Serdang, Selangor, Malaysia Wan Fatinhamamah Wan Ahmad was with Faculty of Engineering, Universiti Putra Malaysia 43400 UPM Serdang, Selangor, Malaysia Despite other power disturbances, SPD is still needed as a protection against surges origin either lightning or switching phenomenon. Bear in mind, an excellent protection from surges can only be accomplished if tremendous coordination all stages of SPD location category starting upstream until downstream are covered. In addition an equipotential bonding also must be accomplished according to the relevant standard available [2]. For ensuring an appropriate function of SPD, the evaluation must be done if use in the particular system or with any electrical equipment which applied [5]. i. Filter typology Filter’s function is to eliminate the excessive noise before entering the load which originated from power supply as its travel along electrical conductors, wires, and printed circuit board or electronics component for example transformers and semiconductors. The electrical noise is also in form of radiated electromagnetic interference (EMI) or radio frequency interference (RFI) which propagates through air and free space. Conducted EMI noise can be divided into two types as common-mode noise (CMN) and differential-mode noise (DMN) known as normal- mode noise (NMN). CMN is the noise signals on each of the current-carrying conductors are in phase and equal in magnitude while the DMN is the noise emerge between the current carrying conductors [6]. Both mode of noise as illustrated in Figure 1 [6]. A complete elimination of NM or DM noise can be accomplished by considering two parts which intrinsic differential mode (IDM) noise and mix-mode (MM) noise using typical EMI typology as in Figure 2 below [7]. II. STANDARD APPLIED There are various standards applied for the protection schemes involving the SPDs as from Institute of Electrical and Electronics Engineers (IEEE), International Electrotechnical Commission (IEC), National Lightning Safety Institute (NLSI), European Association for Electrical, Electronic and Information Technologies (VDE) and etc. General principles, design and installation requirements, testing of SPDs and risk management are overlay almost on these standards, specification, and guidelines. The IEC and IEEE standards implied for the requirement of designing and testing of SPD for low-voltage system is the following. 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 IEC 61643-1: Surge Protective Devices Connected to LowVoltage Power Distribution Systems, Part 1: Performance Requirements and Testing Methods: This standard describing the assessment method being made for evaluating the type and performance of SPD. IEC 61643-2: Surge Protective Devices Connected to LowVoltage Power Distribution Systems, Part 2: Selection and Application Principles: It specifies information on location and category of SPDs including their method of installation, and failure mode of SPDs. IEC 61000-4-5: Electromagnetic Compatibility (EMC) Testing and Measurement Techniques-Surge Immunity Test: It specifies the immunity test, test methods, and array of recommended test levels for devices to unidirectional surges due to overvoltages from switching and lightning transient. IEEE Std.C62.41.2: IEEE Recommended Practice on Characterization of Surges in Low-Voltage (1000V and less) AC Power Circuits: It present the designer an additional selection and specification of surge testing waveforms and stress levels at which described from surge environment that should be considered for specific equipment. IEEE Std.C62.42: IEEE Guide for the Application of Component Surge-Protective Devices for Use in Low-Voltage [Equal to or less than 1000V (ac) or 1200V (dc)] Circuits: It provides assistance in selecting the proper component for SPD or combination of devices used in surge protection, equipment or system application. IEEE Std.C62.45: IEEE Recommended Practice on Surge Testing for Equipment Connected to Low-Voltage (1000V and Less) AC Power Circuit: It concentrates on dealing with surges in low-voltage ac power circuit for testing procedure using a representative surge waveforms developed by the previous Std.C62.41.1. i. Surge Protective Device Category Each of SPD location is referring is known as category which each SPD are with different classification involving the rated current, voltage and specifically different testing waveform amplitude. As for IEC the classification of SPD is depending on the lightning protection zone concept applied consist of Class 1, 2, and 3. The highest exposure is the Class 1 followed by Class 2, and 3 for the least exposure. The IEEE concept is conveyed as location categories including A, B and C with A is the slightest exposure and C is the maximum exposure. The Table II below indicated the detail category of SPD depending from both standards and others. 38 crowbar types are gas discharge tube (GDT), spark-gaps, silicon-controlled rectifiers (triacs) or known as thyristor SPDs. The clamping type has a non linear characteristic, as the voltage across it increases when there is large increase in current flowing through SPD, then the energy is dissipated in the device. The benefits of this type are capable to response rapidly to withstand the high transient surges at same time maintaining the satisfactory lower clamping voltage [8]. Although it suffer from low energy handling capability but it’s still an efficient for power protection application. The crowbar type act contrast to the clamping type, it only operate when the voltage across their terminal exceed a certain value, triggered a spark over and therefore provide the low impedance path to ground during surge propagation. This is identified a volt-time characteristic as it takes time to perform. Hence it is also their disadvantage as slower in operation, other it has a high inrush current in conjunction with that it’s improper for power application but better for communication [1], [8]. By the way their energy withstand capability is excellent which it clamping the transient overvoltage at a relatively low residual voltage [8]. Connection element of SPD either consists of single element or multiple stages in parallel which has its own drawback. A single element connection disadvantage as when its dysfunctional due to burnout, TOV or else therefore a protection from surges is unachievable as there no other backup element to divert the surges. The multiple stages element connection has this benefit plus it can share all the surges current so their reliability is higher than single element connection [8]. Next hybrid connection is introduced which it can be both combination of either clamping or crowbar device with some inductive element in between stages. The examples its can include the GDT at first stage to clamp the high energy surges, at second stage is MOV to clamp the medium energy surges and SAD at last stage to clamp the least energy surges. The inductive element otherwise can be a series inductor or filter with inductor and capacitor as can also filtering harmonic or noise from harming any protected load. III. SIMULATION CIRCUIT OF SURGE PROTECTIVE DEVICE The simulation of surge protective device is starting with the modelling MOV and SAD using the Micro-Cap Spice simulator which is quite similar and compatible with PSPICE. The entire varistor SPICE model in Micro-Cap is based on the manufacturer datasheet of EPCOS and Littelfuse. ii. Surge Protection Device Technology The SPD component type used are clamping and crowbar or switching, with each has different characteristics and performances. The clamping components are MOV or varistor and silicon avalanche diode (SAD) or zener diode, whilst the 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 39 Table I Power system disturbance and SPD interaction Power system disturbances Surges Swells Temporary overvoltages (TOVs) Notches Sags Temporary undervoltages Harmonics Noise Effect on SPD Some Possibly adverse Possibly adverse SPD effect on disturbances Reduce Possibly reduce None None None None None None None Possibly adverse None None Possibly reduce L VNM Sensitive equipment N VCM VCM G Fig. 1. Common-mode (CM) and Normal-mode (NM) noise Fig. 2. Typical EMI typology Table II SPD comparison of location category and exposure Description Level of exposure IEC 61643 IEEE C62.41 DIN VDE Place of application SPD Category Low/Fine Medium High/Coarse Class 3 Class 2 Class 1 Category A Category B Category C Class D Distributed circuits, power outlets, long branch circuit, circuit remote from point-ofentry Class C Class B Sub circuits or near to point of entry, feeder, sub distribution board Point of entry inner city sites, incoming supply, main distribution board 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 40 Rs Ls Cp V = f(I) Fig. 3. Varistor equivalent model ideal diode Ld Rd Vd Fig. 4. Equivalent model of unidirectional silicon avalanche diode Element of filter MOV SAD L Input Output N Fig. 5. Circuit of hybrid protection In SPICE model varistor is signify in V/I characteristic curve with a shunt capacitance and series inductance. Below in Figure 3 [9] is a basic equivalent model for MOV, as Rs is the series lead resistant, Ls is the series lead inductance, Cp is the shunt capacitance and V = f(I) is the V/I characteristic. Model of V/I characteristic is implemented by a controlled voltage source V = f(I) with an insertion series resistance, Rs = 100μΩ to avoid occurring of impermissible state when a source is connected directly. The approximation mathematical expression is: log V b1 b2 . log( I ) b3 .e log( I ) b4 .e log( I ) I > 0 (1) The SAD basic form is a single semiconductor P/N junction consists of an anode (P) and a cathode (N). In SPICE model the entire SAD model is based on ST Microelectronics and Littelfuse manufacturers. In Figure 4 below is an equivalent model of SAD [10]. Rd is a resistance of SAD, and Ld is depending on the length of the leads connecting SAD to external circuit. While Vd, is the dc voltage source or breakdown voltage which if voltage across SAD is below the Vd, none current is conducting and vice versa [10]. The general circuit of hybrid protection which consists of MOV and SAD as the element of SPD with a inductorcapacitor (LC) as the element of filter for this paper as illustrated in Figure 5. LC as a filter is placed between the stages of MOV and SAD. The simulation of SPD circuit without a filter also is applying which the circuit diagram similar in Figure 5 except without the element of LC in between. i. Simulation of impulse voltage and current The simulation of SPD involving Class 3 (IEC) or Category A (IEEE), hence a combination waveform is applied for testing as according to both standard. The standard equation of impulse waveform for voltage as in mathematical expression below: V Vc e t e t (2) with front time 1.2s and duration 50s as the front voltage waveform is 1.67 (t90 – t30) which t90 and t30 are the times of 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 90% and 30% amplitude of the leading edge of waveform. The equation for current impulse waveform as: I A e t e t IV. ACTUAL EXPERIMENT OF SURGE PROTECTIVE DEVICE CIRCUIT The surge waveform is generated by modular impulse generator Haefely which has internal resistor of 2 ohm, beside other useful equipment are the high voltage probe, Le-Croy digital storage Oscilloscope and current clamper. Before proceed to the actual experiment testing, the fabricating of SPD circuit is needed and the component selections are based on the chosen type components on simulation earlier. Since described by IEEE [12] and IEC [13] [14], the procedure of testing equipment is thought according the guidance and meet the standard requirement to avoid the misleading results. Therefore, the standard of procedure defines the range of test levels, test equipment, test setup and test procedure. (3) which the front time 8s and duration of 20s as the front current waveform is 1.25 ( t90 – t10) with t90 and t10 are the times of 90% and 10% of amplitude. The amplitude for combination waveform tested in this simulation are 6kV/ 3kA as in normal nature despite the IEC suggesting the maximum amplitude can be reach are 20kV and 10kA. Figure 6 show the simulation of combination wave applied for testing in Class 3. ii. Element of filter In this simulation only a single inductor-capacitor (LC) filter is applied as using the X capacitor (CX) with a series of inductor as in Figure 7. The matrix equation described in equa. (4) is represent the simple L consists with a series inductor and a shunt capacitor that outline a simple chain matrix. The mathematical expression of inductive capacitive reactance can be finding by substituting equa. (5) into equa. (4) [11]. 2 JKRd V Vi 1 K o JK I I o 1 i R d R 1 C L d 2F0 Rd 2F0 41 i. Generation of Impulse voltage and current The modular impulse generator generates the combination waveform at 6kV (1.2/50µ) and 3kA (8/20µ) as shown in Figure 8. Each mode of SPD; Live, Neutral and Ground are injected with surge waveforms and the performance output is analyzed in term of let-through voltage. (4) (5) Fig. 6. Simulation of combination wave, open circuit voltage 6kV/3kA L C Fig. 7. LC Network Description for the above figure. 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 42 Fig. 8. Combination waveform testing Input of Combination wave 7 6.104 6 6.027 Exp: T 90% = 0.8µs Sim: T 90% = 0.6µs 5 Voltage (kV) 4 Exp: T 50% = 45µs Sim: T 50% = 49µs 3 2 Exp: T 30% = 0µs Sim: T 30% = 0µs 1 0 -10 0 10 20 30 40 50 -1 time (µs) experiment input simulation input Fig. 9. The comparison input of combination waveform 6kV/3kA Output at L-N 270 Exp: 251.95V Sim: 240.10V 230 voltage (V) 190 Exp: 162.00V Sim: 151.92V 150 110 70 30 -10 -10 0 Experiment (filter) 10 20 time (µs) Simulation (filter) 30 Experiment (no filter) 40 50 Simulation (no filter) Fig. 10. Output at Live to neutral for SPD with filter compare to SPD without filter 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 43 Output at L-E 290 Exp: 262.78V Sim: 260.48V 240 voltage (V) 190 Exp: 168.13V Sim: 158.92V 140 90 40 -10 -10 0 Experiment (filter) 10 20 time (µs) Simulation (filter) 30 Experiment (no filter) 40 50 Simulation (no filter) Fig. 11. Output at Live to earth for SPD with filter compare to SPD without filter Output at N-E 290 Exp: 253.19V Sim: 238.86V voltage (V) 240 190 Exp: 161.67V Sim: 151.02V 140 90 40 -10 -10 0 Experiment (filter) 10 20 time (µs) Simulation (filter) 30 Experiment (no filter) 40 50 Simulation (no filter) Fig. 12. Output at Neutral to earth for SPD with filter compare to SPD without filter V. RESULTS AND DISCUSSION i. Evaluation of input waveform The SPD circuit is being tested with by injecting the combination waveform of 6kV/3kA on each mode of protection which are Live to neutral (L-N), Live to earth (L-E) and Neutral to earth (N-E). The output after the SPD components clamping is measured for voltage difference between the output terminal which known the let-through voltage. Figure 9 show the input of both combination waveforms from simulation and experiment for first injection. As observe the different between the simulation input and the experiment input is faintly which is 1.26 %. While evaluation with the standards; IEC [4], [13] and IEEE [10], the requirement of open circuit voltage are the front time margin is T1 = 1.2µs ± 30% and time to half value, T2 = 50µs ± 20%. Hence, in analysis of experiment input the T1 is 1.34µs and T2 is 45µs, that both are within the margin time. Though the simulation time, T1 and T2 are 1 µs and 49µs respectively which within the proposed margin time. For that reason, the experiment and simulation input are accurate. Moreover, the value of Vpeak (Note 1) for simulation and experiment also is within 10% margin endowed that 6.027kV and 6.104kV correspondingly. ii. Live to neutral The graph in Figure 10 indicated the result when impulse voltage is injected at between Live and Neutral (L-N) line. The output result signifies after SPD clamping is known as the let-through voltage. Shown from the Figure 10 the let-through voltage for hybrid SPD with filter is much lower than without the filter whether in simulation or experiment. The let through voltage of SPD with filter added much lower than SPD without filter about 35.7% to 36.7% for both in experiment and simulation subsequently. As observe, the simulation result is predict a bit lower than the experiment but yet still tolerable which the difference is around 4.7% to 6.2% compare to the 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS International Journal of Engineering & Technology IJET-IJENS Vol: 11 No: 02 experiments’ result. Above all, the pattern of all output graphs is similar whether in actual experiment or forecasted in simulation. iii. Live to earth Let through voltage at the Live to earth is in Figure 11. In analysis, the results signify the let through voltage of SPD with filter is 36.02% lower than without filter in experiment and 38.99% much lower for filtered SPD than non filtered SPD in simulation. The dissimilarity of output for SPD with filter between simulation and experiment is 5.48%. While, for SPD without filter the difference is 0.88% comparing in experiment and simulation. iv. Neutral to earth Figure 12 demonstrates the results of let through voltage at the Neutral to earth mode. As analyze, the let through voltage of SPD with effect of filter has the 36.15% peak lower than non filter in actual experiment result. Moreover, in simulation the peak voltage lower than 36.78% for filtered SPD than the non- filtered. Hence, the dissimilarity among simulation and experiment results is minimal 5.65% and 6.59% for both types of SPDs. The entire the cases whether the surge is implied at L-N, L-E or N-E mode resulting the same lowers let-through voltage which represents the lower let-through voltage the improved protection as the supply voltage entering the load at safe level. This is indicated by more than 30% of less let through voltage of SPD with filter than the SPD without a filter being added. Thus, the simulation of the design hybrid SPD is effectively functioned by clamping the certain amount of surge voltages injected as well in the actual experiment implied which with a minimal error percentage and a parallel pattern of result graphs. Attributable to this, in addition filter also functioning as rejecting the higher frequency of current which in this case is more than 150 kHz as well as reduce the noises in power line. V. CONCLUSION It is proven that by adding a filter as element of inductive and isolating part between stages for hybrid SPD indeed has a excellent impact to assist a much lower let-through voltage after the surges impinges. In average, the SPD with added filter was obtain 38% reduce of let through voltage contrast to non added filter whether by experiment or simulation. Therefore the enhancement of SPD Class 3 for a better reliable protection is accomplished. Beside, the simulation as a tool for forecasting analysis of performance SPD circuit in further study is acknowledgeable as it resembles the actual experiment practice. 44 REFERENCES [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] S. Ioannou, E. K. Stefanakos, P. H. Wiley, (2007). New MOV Failure Mode Identification Invention, IEEE Transactions on Consumer Electronics, vol. 53 n.3, pp1068 – 1075. D. Kadar, F. Martzloff, (2006). Facts, Fiction, and Fallacies in SPD Design and Applications, IEEE, pp. 1- 8. IEEE Guide on Interactions between Power System Disturbances and Surge-Protective Devices, (2005). IEEE Standard C62.48. Low-Voltage Surge Protective Devices-Part 12: Surge Protective Devices Connected To Low-Voltage Power Distribution SystemSelection And Application Principles, (2002). IEC Standard 6164312. R. W. Hotchkiss, (2008). Application of Low-Voltage SPDs: Approach of he IEEE, IEEE. Dev Paul, (2001). Low Voltage Power System Surge Overvoltage Protection, IEEE Transaction on Industry Application, vol. 37 n. 1, pp. 223 – 227. Hung-I Hsieh, Jhong-Shu Li, Dan Chen, (2008). Effects of X Capacitors on EMI Filter Effectiveness, IEEE Transactions on Industrial Electronics, vol. 55 n. 2, pp. 949-955. K. Samaras, C. Sandberg, C. J. Salmas, A. Kaoulaxouzidis, (2005). Electrical Surge Protection Devices For Industrial Facilities (A Tutorial Review), IEEE, pp. 165 – 175. SIOV Metal Oxide Varistors, (2008). EPCOS Data Book. A. Beutel, J. V. Coller, (2005). The Application of Silicon Avalanche Diodes on Low Voltage Power Systems, IEEE Transactions on Industry Applications, vol. 41 n. 4, pp 1107-1112. R. L. Ozenbaugh,(2001). EMI Filter Design, (2nd ed. revised and expanded) New York: Marcel Dekker, Inc.(Chapter 18). IEEE Recommended Practice on Surge Testing for Equipment Connected to Low-Voltage (1000V and Less) AC Power Circuit, (2002). IEEE Standard C62.45. Electromagnetic Compatibility (EMC)-part 4-5: Testing and Measurement Techniques-Surge Immunity Test (First Revision), (2001). IEC Standard 61000-4-5. Low-voltage Surge Protective Devices-Part 1: Surge Protective Devices Connected to Low-Voltage Power Distribution SystemsRequirements and Tests (First Revision), (2005). IEC Standard 61643-1. IEEE Recommended Practice on Characterization of Surges in Low-Voltage (1000 V and less) AC Power Circuits, (2002). IEEE Standards C62.41.2. ACKNOWLEDGMENT This work was supported by Centre of Excellence on Lightning Protection (CELP). 113502-0909 IJET-IJENS @ April 2011 IJENS IJENS