ISSN 2319-8885

Vol.04,Issue.35,

August-2015,

Pages:7279-7282

www.ijsetr.com

Design and Analysis of High performance and High Slew Rate

Class AB Operational Amplifier

V. M. VINOD KUMAR

PG Scholar, Dept of ECE, RGM College, Andhrapradesh, India.

Abstract: This paper presents symmetrical and high slew rates in class AB operational amplifier using a low voltage sence

amplifier using cross coupled sence amplifier in two stage class AB op-amp. It will produce and the results are compared with the

existing methods.

Keywords: Class AB Operation, Operational Amplifiers, Symmetrical Slew Rate.

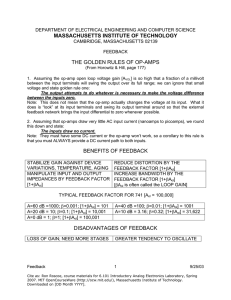

I. INTRODUCTION

It is commonly known that slew rate of an op-amp is

limited by the current drive capability of its input stage. For

class-A circuit, a maximum output current is limited by bias

current. On the contrary, class-AB input stage can provide

the output current much higher than its bias current. So, in

high speed application, the class-AB input stage has an

advantage. Various structures of class-AB op-amps have

been developed. In comparison between three techniques for

improving amplifier slew rate, namely dynamic frequency

compensation,

non saturated input stage and dynamic

biasing, have been reported. In the same year, the new classAB principle is proposed. It has high has high slew rate, But

it suffers from instability problem, which is caused by current

feedback loop. Subsequently, a class-AB CMOS op-amp

with novel self-biased input transistor was proposed in, its

characteristics are almost identical to those of the op-amp

proposed, but the instability problem is eliminated.

However, the entire reported high slew rate op-amps

mentioned above is single stage. Thus their open-loop gains

are not comparable to those of the traditional two stage opamps and the miller compensation technique cannot be

applied. As a result, some close-loop performances such as

accuracy, linearity, common mode rejection ratio (CMRR)

and bandwidth of these class-AB op-amps are restricted.

This paper proposes a novel input stage, which is

intended for two-stage high speed CMOS op-amp. The input

stage comprises a pair of a mixed CMOS Trans linear circuit

and provides dual outputs. Thanks to its class-AB structure,

the output current of the proposed input stage can be many

times higher than the bias current. Moreover, its symmetrical

architecture allows the CMRR to be as high as that of the

classical class-A differential pair. To verify the viability of

the proposed input stage, a high speed op-amp comprising

the proposed input stage and a simple complementary

common-source high-gain stage is demonstrated In singlestage op-amps achieves highly symmetrical slew rate by

using different efficient schemes. low open-loop gain(Aol)

disadvantage of a single stage op-amp. output cascading

transistors is used to increase the output resistances(Rout). it

limit the maximum output current and the slew rate

enhancement factor .In the conventional class-A two-stage

Miller-compensated op-amp is characterized by a highly

asymmetrical slew rate with large positive slew rate and

much lower negative slew rate .This much lower negativeslew rate is due to the output transistor (MoN) acts as a dc

current source with 2IB value and increase the static power

dissipation. To avoid this limitation some class AB two-stage

op-amps have been reported. feature models are relatively

modest effective slew rate improvement non negligible static

power dissipation require additional complex circuitry

increased supply requirements are the features of most

reported class AB op amps. current efficiency is decreased

by this and the expression for current efficiency is

CE=Ioutmax/Iqtotal where Ioutmax=maximum output

current, Iqtotal=total op-amp static current.

In Fig.1 (b) achieves class AB operation with additional

small hardware. It consists of a small capacitor C bat and

large resistive element Rlarge this combination operates as a

open battery that transfers ac variations taking place at the

gate of Mop to the gate of Mon transistors .The output stage

operates as a push-pull amplifier and provides dynamic classAB operation with large positive and negative output

currents. This does not increase supply requirements and

power dissipation but operates in only perticular frequencies

frequencies. In this brief, two-stage op-amps with mostly

symmetrical slew rate are presented. Class Ab Two-Stage

Op-Amps existed models remembered in Section II. In

Section III presents the Proposed and Existing Methods

.Sections IV deal with simulation and experimental results,

respectively. Finally, some conclusions are drawn in Section

V.

Copyright @ 2015 IJSETR. All rights reserved.

V. M. VINOD KUMAR

Vb triode=Vss+Vgs+VDSsat=VTH+2VDSsat is required at the

II. PREVIOUS CLASS AB TWO-STAGE OP-AMPS

gate of MoNR. Where VDSsat= Vgs-Vth is the minimum Vds

A. Op-Amp with Current Replication Branch

To achieve class AB operation, the output transistor MoN

voltage to operate in saturation region. This Vbtroide leaves a

can be turn into an active amplifying device by simply

quiescent drain-source voltage for MoNtriode with value

adding a current replicating branch formed by M2R and

VDSsat, which causes MoNtriode to operate between triode

MoNR as shown in Fig.1(c).This transfers current variations

and saturation regions boundaries. The circuit of Fig. 2 is

Ia in M1-M2 to the output transistor MoN and increases and

denoted as operational amplifier with current replicating

increases the maximum positive output current by 2IB. The

branch and adaptive loads. These topologies are not harmful

negative current is limited to 2IB.gain in the current

in terms of stability of the ac responses. The current

replicating branch is from gate to the drain of MoN The

replicating branch helps compensating the current through

current replicating branch does not require additional

the miller capacitor just as in other multipath miller zerocompensation circuit. the node Vx that become advantage by

cancellation scheme.

this additional compensation is not required for the current

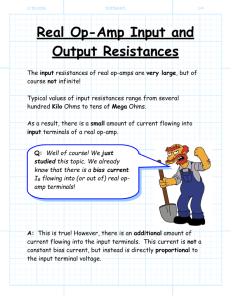

III. SYMMETRICAL AND HIGH SLEW RATE CROSS

replicating branch and miller compensation causes MoP to

COUPLED TYPE TWO STAGE OP-AMPS

behave as low impedance diode connected load at high

frequency.. The gain between the op-amps output terminal

and the gate of MoN reduced to closely a unity value. The

current replicating branch has small dimensions reducing

static power dissipation and area . For achieve large negative

output currents, non-linear adoptive load can be used similar

to the teqnique introduced.

Fig.2. symmetrical and high slew rate cross coupled type

two stage op-amps.

Fig.1. (a) Conventional two-stage Miller op-amp. (b)

Free-class AB op-amp. (c) Push pull op-amp with current

replication branch M2R, MoNR. (d) Class AB two-stage

op-amp with current replicating branch using adaptive

load II at the input stage. (e) Class AB two-stage op-amp

with current replicating branch using adaptive load I at

the input stage.

B. Class AB Two-Stage Op-Amp Using Adaptive Loads

By using an adaptive load at the input side in the circuit

we can achieve class AB operation efficiently. Two different

alternatives are shown in Fig.1 (d) and Fig.1 (e).In both

cases, the adoptive loads man oeuvre the large variation of

output resistance of transistors between triode and saturation

regions in quiescent conditions. In both schemes a current

increase in IA causes transistors to go in triode region and to

develop large drain-source voltages. These changes cause

large currents flow in the output transistors Mop and thanks

to the current replicating branch, A bias voltage with value

Sense amplifier which detects the voltage difference

on the bit lines is called voltage mode sense amplifier.

There are some different types voltage mode sense amplifiers

like single ended sense amplifiers, differential amplifiers

and Cross coupled sense amplifiers. Different types of

sense amplifier are used in different types of memory

cells

according to the proper design and efficient

performance. Cross coupled voltage mode SA. M1 and M2

are the access transistors, whereas M3-M6 forms crosscoupled inverters. When SAEN is low, M1 and M2 are turned

ON and voltage on BL and BLB will be transferred to SL

and SLB respectively. Due to positive feedback, higher

voltage level goes to VDD and other level goes towards zero.

the nodes SL and SLB are input and output terminals at the

same time In the basic cross-coupled SA. By the way circuit

cannot be connected directly to the bit line since the

circuit would attempt to discharge the bit line

capacitance during the decision phase and would increase

delay and power. A solution is either to separate the bit

line by forming a decoupling resistor with a multiplexer

or to use pass gates. Both cause a voltage drop that

deteriorates the available input voltage difference. By This

way the voltage swing at the bit lines can simply reduce

by half, then lower speed and noise margin as a resulting.

This sense amplifier form with strong positive feedback

with a high resistive input.

International Journal of Scientific Engineering and Technology Research

Volume.04, IssueNo.35, August-2015, Pages: 7279--7282

Design and Analysis of High performance and High Slew Rate Class AB Operational Amplifier

The current flow of the differential input transistors

voltage followers, and results are shown in Fig.4. The figure

M2 and M1 controls the serially connected latch circuit.

compares simulations of the current in the load capacitor of

A large output voltage comes by converts small difference

the conventional class A op-amp of Fig. 4(a) with the class

between the currents through M1 and M2 . During reset

AB op-amp of Fig. 3, and both class AB op-amps with

phase when SAEN=0V, the output nodes of the SA (O1 and

adaptive loads at the input stage of Fig. 4(d) and (e). The

O2) are reset to VDD through the reset transistors M6 and

unitary transistor dimensions are (W/L)N = 50/1 and (W/L)P =

M9. This current latched SA is faster compare to

140/1. IB = 100 μA, CL = 30 pF, VDD = 1.65V, VSS = −1.65V,

conventional cross coupled SA. During evaluation phase

Rc = 2 kΩ, Cc = 10 pF, and

when SAEN=VDD, M3 turns ON and the input transistors

M1 and M2 starts to discharge O1and O2 node voltages

to GND. NMOS transistors of the cross coupled inverters

turn ON initiating positive feedback. When any of these

node voltages falls from VDD to VDD-Vthn. Further

PMOS transistors of the inverters turns ON and further

enhances the positive feedback and converts a small input

voltage difference to large full scale output. when any of

output node voltage drops to VDD-Vthp. Inverters are

used further to speed up the sensing process.

A. Existing Method

Fig 3 shows the existed circuit in this adaptive load had

been added directly in current replicating branch for getting

large negative output current. it is based on diode connected

load in current replicating branch type modification by

adding transistor between MoNtriode, gate of MoNR and

lower supply rail. The minimum Vds voltage to operate in

saturation VDSsat = Vgs-Vth. The diode connected transistor

MBtriode W/L equal to ¼ of MoN tride and MoNR. by this

it achive double the VDS,sat and thus its VG1is required

Vbtriode. gives a quiescent drain source voltage ride and for

MoNtride with value VDS sat ,by this effect MoNtriode

operates between trode and saturation region boundaries.

Fig.3. (a) Vbtriode circuit generator and (b) class AB twostage op-amp with current replicating branch using an

adaptive load.

When increase in current Ia then increade gate source

voltage of MoNR, decrease drain-source voltage of Mon

triode then transistor goes into triode region at Vx large

voltage increase with respect of large optput current in

transistor MoN .the negative slew rate is improved with

almost equal to positive slew rate.

(e)

Fig.4. Output current transient responses for (a)

conventional operational amplifier, (b) operational

amplifier with current replicating branch and adaptive

load, (c) operational amplifier with adaptive load type I at

the input stage and current replicating branch, and (d)

operational amplifier with adaptive load type II at the

input stage and current replicating branch.fig 4(e) output

response of cross coupled two stage classAB op-amp.

Vbiastriode = VSS +1.25 V. The Miller compensation net is

the same in all of the four circuits. It can be seen that, while

the conventional op-amp works in class A, class AB

performance is achieved in the three proposed topologies

getting negative output currents much larger than IB and

approximately of the same order than the positive output

current. This result confirms the improvement in negative

slew rate achieved with these topologies.

IV. SIMULATION RESULTS

Transient post layout simulations have been made with the

operational amplifiers configured in unity-gain closed loop as

International Journal of Scientific Engineering and Technology Research

Volume.04, IssueNo.35, August-2015, Pages: 7279-7282

V. M. VINOD KUMAR

[10] J. Ramirez-Angulo, “A novel slew-rate enhancement

TABLE I: Positive Slew Rate and Negative Slew Rates

technique for one stage operational amplifiers,” in Proc.

Comparisons With Different Class AB Op-Amps

IEEE 39th Midwest Symp. Circuits Syst., vol. 1. Aug. 1996,

pp. 7–10.

[11] F. You, S. H. K. Embabi, and E. Sanchez-Sinencio,

“Low-voltage Class- AB buffers with quiescent current

control,” IEEE J. Solid-State Circuits, vol. 33, no. 6, pp. 915–

920, May 1998.

[12] J. Ramirez-Angulo, R.G. Carvajal, J. Tombs, and A.

Torralba, “Low-voltage CMOS op-amp with rail-to-rail input

and output signal swing for continuous-time signal

processing using multiple-input floating-gate transistors,”

IEEE Trans. Circuits Syst. II, Analog Digital Signal Process.,

vol. 48, no. 1, pp. 111–117, Jan. 2001.

V. CONCLUSION

Author’s Profile:

The different schemes of power-efficient class AB twostage op-amps are introduced by using a Cross coupled type

V. M.Vinod Kumar, was born in Kadiri

technique in two stage op-amps have been experimentally

Village, Anantapur District, in 1991. He

tested. They achieved approximately symmetrical and high

received the B.Tech degree in Electronics

slew rate with very small additional static power dissipation..

and Communication Engineering from

Furthermore due to its entire class-AB structure, the

JNTU Anantapur, in 2013 and M.Tech

presented op-amp is also power efficient.

Degree Specialization in Embedded

Systems from JNTU Anantapur, in 2015.

VI. REFERENCES

[1] Jesus Aguado-Ruiz, Antonio Lopez-Martin, Javier LopezLemus, and Jaime Ramirez-Angulo, “Power Efficient Class

AB Op-Amps With High and Symmetrical Slew Rate”, IEEE

Transactions on Very Large Scale Integration (VLSI)

Systems, Vol. 22, No. 4, April 2014.

[2] J. Ramirez-Angulo and M. Holmes, “Simple technique

using local CMFB to enhance slew rate and bandwidth of

one-stage CMOS op-amps,” Electron. Lett., vol. 38, no. 23,

pp. 1409–1411, Nov. 2002.

[3] A. J. Lopez Martin, S. Baswa, J. Ramirez-Angulo, and R.

G. Carvajal, “Low-voltage super class AB CMOS OTA cells

with very high slew rate and power efficiency,” IEEE J.

Solid-State Circuits, vol. 40, no. 5, pp. 1068–1077, May

2005.

[4] J. A. Galan, A. J. Lopez-Martin, R. G. Carvajal, J.

Ramirez-Angulo, and C. Rubia, “Super Class-AB OTAs with

adaptive biasing and dynamic output current scaling,” IEEE

Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 3, pp. 449–

457, Mar. 2007.

[5] W. Sansen, “Class AB and driver amplifiers,” in Analog

Design Essentials, W. Sansen, Eds., 1st ed. New York, NY,

USA: Springer-Verlag, 2006, pp. 337–362.

[6] C. K. Chava and J. Silva-Martinez, “A frequency

compensation scheme for LDO voltage regulators,” IEEE

Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 6, pp. 1041–

1050, Jun. 2004.

[7] D. M. Monticelli, “A quad CMOS single-supply op-amp

with rialto rail output swing,” IEEE J. Solid-State Circuits,

vol. 21, no. 6, pp. 1026–1034, Jun. 1986.

[8] K. J. De Langen and J. H. Huising, “Compact low-voltage

power efficient operational amplifier cells for VLSI,” IEEE J.

Solid-State Circuits, vol. 33, no. 10, pp. 1482–1496, Oct.

1998.

[9] J. Ramirez-Angulo, R. G. Carvajal, A. Lopez-Martin, and

J. A. Galan, “A free but efficient class AB two-stage

operational amplifier,” IEEE Trans. Circuits Syst. II, Exp.

Briefs, vol. 53, no. 7, pp. 568–571, Jul. 2006.

International Journal of Scientific Engineering and Technology Research

Volume.04, IssueNo.35, August-2015, Pages: 7279--7282