ISSN 2319-8885

Vol.03,Issue.44

December-2014,

Pages:8927-8932

www.ijsetr.com

Design and Simulation of Low Power and Area Efficient SQRT Carry

Select Adder with Modified Binary to Excess-1 Converter

B.BHUPAL1, S.K.SATYANARAYANA2

1

PG Scholar, Dept of ECE (DS & CE), SNIST, Hyderabad, India, Email: bhupal1533@gmail.com.

2

Asst Prof, Dept of ECE, SNIST, Hyderabad, India, Email: satyanarayanask@sreenidhi.edu.in.

Abstract: In the design of Integrated circuits, area occupancy and power consumption plays a vital role because of increasing

necessity of portable systems. Carry Select Adder (CSLA) is a fast adder used in data processing processors for performing fast

arithmetic functions. From the structure of the CSLA, it is clear that there is scope for reducing the area and power consumption

in the CSLA. This work uses a simple and efficient transistor level modification of EX-OR gate used in BEC-1 converter to

significantly reduce the area and power of the CSLA. Based on this modification 4, 8, 16-bit SQRT CSLA architecture have

been developed and compared with the SQRT CSLA architecture using AND, OR, INVERTER (AOI) implementation of EXOR gate used in BEC-1 converter. The proposed SQRT CSLA is designed in 130 nm technology. The proposed design has

reduced area and power as compared with the SQRT CSLA using ordinary BEC-1 converter. This work evaluates the

performance of the proposed designs in terms of area and power. The results analysis shows that the proposed SQRT CSLA

structure is better than the regular SQRT CSLA.

Keywords: Adder, CSLA, BEC.

I. INTRODUCTION

Addition is one of the fundamental arithmetic operations.

It is used extensively in many VLSI systems such as

microprocessors and application specific DSP architecture.

This module is the core of many arithmetic operations such

as addition/subtraction, multiplication, division and address

generation. In most of these systems the adder is part of the

critical path that determines the overall performance of the

system. In Present generation in VLSI system are more

concentrating in the reduction of area and power [1][2] and

increasing the speed of operation of the circuit. In digital

adders, the speed of addition is controlled by the time

required to propagate a carry through the adder. The sum for

each bit position in an elementary adder is generated

sequentially only after the previous bit position was summed

and a carry propagated into the next position. The CSLA is

used in many electronic applications to alleviate the problem

of carry propagation delay [3] by independently generating

the multiple carries and then select the carry to generate the

sum. However, the CSLA [4] is not area efficient [5] because

it contains multiple Pairs of cascaded Ripple Carry Adder

(RCA) with input Cin=0 and Cin=1, to generate partial sum

and carry, then the final sum and carry are selected by

multiplexers. This paper illustrates the SQRT CSLA with

modified Binary-to-Excess-I converter when Cin=1. The main

advantage of this modified BEC logic comes from the less

area than the n-bit full Adder structure. The proposed

structure reduces the area and power compare to regular

CSLA structure [6].

II. LITERATURE SURVEY

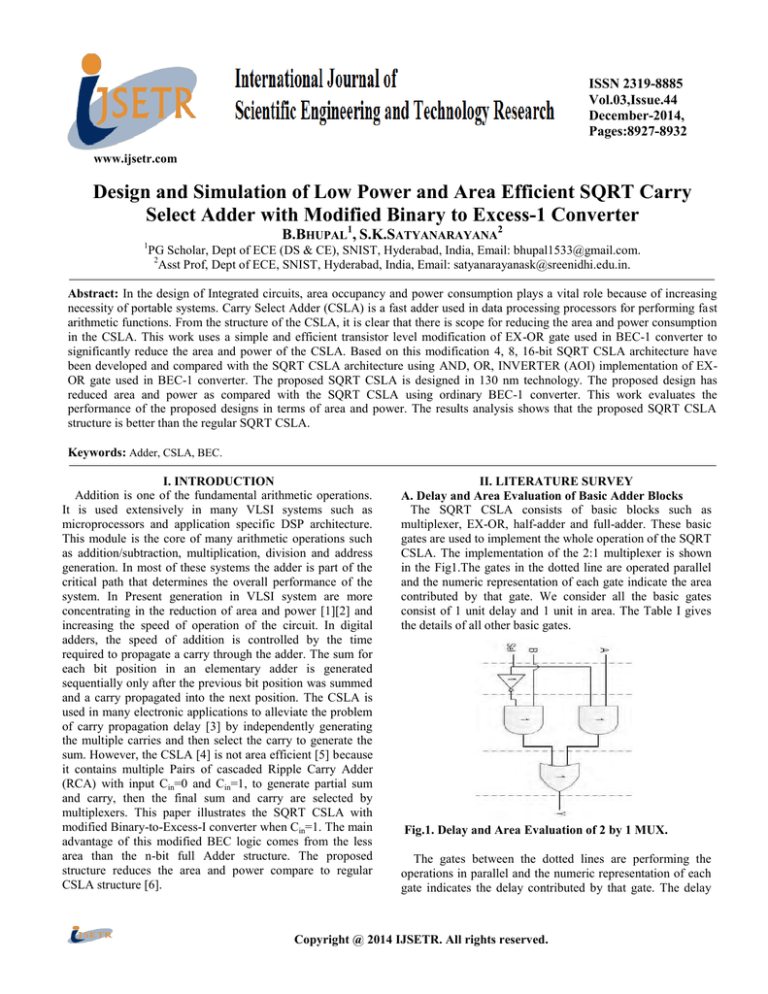

A. Delay and Area Evaluation of Basic Adder Blocks

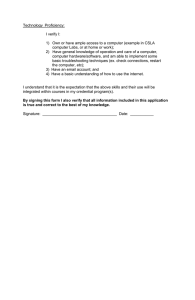

The SQRT CSLA consists of basic blocks such as

multiplexer, EX-OR, half-adder and full-adder. These basic

gates are used to implement the whole operation of the SQRT

CSLA. The implementation of the 2:1 multiplexer is shown

in the Fig1.The gates in the dotted line are operated parallel

and the numeric representation of each gate indicate the area

contributed by that gate. We consider all the basic gates

consist of 1 unit delay and 1 unit in area. The Table I gives

the details of all other basic gates.

Fig.1. Delay and Area Evaluation of 2 by 1 MUX.

The gates between the dotted lines are performing the

operations in parallel and the numeric representation of each

gate indicates the delay contributed by that gate. The delay

Copyright @ 2014 IJSETR. All rights reserved.

G.NALINI, KONDAVEETI SUDHARANI

and area evaluation methodology considers all gates to be

The Boolean expressions of the 4-bit BEC is listed as

made up of AND, OR, and Inverter, each having delay equal

X0 = ~ B0

to 1 unit and area equal to 1 unit. We then add up the number

X1 = B0 ^ B1

of gates in the longest path of a logic block that contributes to

X2 = B2 ^ (B0 & B1)

the maximum delay. The area evaluation is done by counting

X3=B3 ^ (B2 & (B1&B0))

the total number of AOI gates required for each logic block.

Table I Delay and area count of adder blocks

Delay and Area count of Basic blocks

Adder blocks

Delay

Area

2:1

MULTIPLEXER

EX-OR

3

4

3

5

HALF ADDER

3

6

FULL ADDER

6

13

B. Binary to Excess -1 Converter (BEC)

BEC-I is a circuit used to add 1 to the input numbers .A

circuit of 4-bit BEC [7] and the truth table is shown in Fig.2

and Table II respectively. The goal of addition is achieved

using BEC together with a multiplexer shown in Fig.3, one

input of the 8:4 multiplexer gets as it input (B3, B2, B1, and

B0) and another input of the multiplexer is the BEC output.

Fig2. 4-bit BEC-I.

Table II. Function table of the 4-b BEC

Fig3. BEC with MUX.

The main idea of this work is to use BEC instead of the

RCA with Cin=1 in order to reduce the area and power

consumption of the conventional CSLA. To replace the n-bit

RCA, an n+1 bit BEC is required.

C. Area Evaluation Methodology of Regular SQRT

CSLA.

The basic square root Carry select adder has a dual ripple

carry adder with 2: 1 multiplexer the main disadvantage of

regular CSLA is the large area due to the multiple pairs of

ripple carry adder. The regular 16-bit Carry select adder is

shown in Fig.4. It is divided into five groups with different

bit size RCA. From the structure of Regular CSLA [9], there

is scope for reducing area and power consumption. The carry

out calculated from the last stage i.e. least significant bit

stage is used to select the actual calculated values of the

output carry and sum. The selection is done by using a

multiplexer. Internal structure of the group 3 of regular 16-bit

CSLA is shown Fig.5.By manually counting the number of

gates used for group 3 is 87. One input to the multiplexer

goes from the RCA with Cin=0 and other input from the RCA

with Cin=1.

Fig.4. Regular 16-bit SQRT CSLA.

International Journal of Scientific Engineering and Technology Research

Volume.03, IssueNo.44, December-2014, Pages: 8927-8932

High Speed and Power Optimized Scalable Comparator using Parallel Prefix Tree

Fig5. Delay and area evaluation for group3.

Fig7. Group 3 for Modified SQRT CSLA.

Area count of Regular SQRT CSLA groups as follows in

the table III.

Comparing the group 3 of both regular and modified

CSLA, it is clear that BEC structure reduces the area and

power. Area count of Modified SQRT CSLA groups as

follows in the table IV.

Table IV. Area count of Modified SQRT CSLA

GROUP

AREA COUNT

Table III. Area count of Regular SQRT CSLA

GROUP

AREA COUNT

GROUP1

26

GROUP2

57

GROUP3

87

GROUP4

117

GROUP5

147

From Table III, the total number of gate counts in

group3 is determined as follows:

Gate count = 87 (HA + FA + Mux)

FA = 65 (5 * 13)

HA = 6 (1 * 6)

Mux = 16 (4 * 4)

D. Area Evaluation Methodology Of Modified SQRT

CSLA

The structure of the proposed 16-b SQRT CSLA using

BEC [7] for RCA with Cin=1to optimize the area and power

is shown in Fig. 6. We again split the structure into five

groups.

Fig6. Modified 16-bit SQRT CSLA.

GROUP1

26

GROUP2

43

GROUP3

66

GROUP4

89

GROUP5

113

From Table IV, the total number of gate counts in

group3 is determined as follows:

Gate count = 66 (HA + FA + Mux + BEC)

FA = 26 (2 * 13)

HA = 6 (1 * 6)

AND=2 (2 * 1)

NOT=1

Mux = 16 (4 * 4)

EX-OR=15(3*5)

Comparing Tables III and IV, it is clear that the 16 bit

modified SQRT CSLA has less area than the regular SQRT

CSLA.

III.PROPOSED METHOD

Though BEC technique reduces area and power but not up

to considerable amount. There is a scope to reduce the

number of transistors along with the area reduction and

power dissipation reduction by using proposed logic. The

modified SQRT CSLA using BEC is designed with AOI

implementation. The AND, OR, and Inverter (AOI)

implementation of an EX-OR gate is shown in Fig.8.

Schematic view of AOI implementation of EX-OR gate as

shown in the Fig 8.It consists 22 transistors. The area can be

considered as number of transistors. In the proposed design

EX-OR gate can be designed with 12 transistors, then area

and power dissipation will be decreased. The modified EXOR gate as shown in the Fig.9.

International Journal of Scientific Engineering and Technology Research

Volume.03, IssueNo.44, December-2014, Pages: 8927-8932

G.NALINI, KONDAVEETI SUDHARANI

The 4-bit proposed SQRT Carry Select Adder is designed

by using 2-bit Ripple carry adder and 3-bit modified Binary

to Excess-1 converter and multiplexer. The outputs of ripple

carry adder are given as inputs to the 3-bit modified Binary to

Excess-1 converter. The 4-bit proposed SQRT CSLA has one

2-bit Ripple Carry Adder for Cin=0. Instead of another 2-bit

Ripple Carry Adder with Cin=1, a 3-bit modified Binary to

Excess-1 converter is used which adds one to the output from

2-bit RCA. The Final sum will be selected from multiplexers

by the carry out generated by the pervious block. The

proposed 4-bit SQRT CSLA is designed in 130nm

technology. The Schematic view of 4-bit proposed SQRT

CSLA is shown in the Fig.11.

Fig8. Schematic view of AOI implementation of EX-OR

gate.

Fig9. Schematic view of modified EX-OR gate.

The Binary to Excess-1 converter is designed with modified

EX-OR gates, AND gates and Inverter gate, then the area and

power dissipation will be decreased compare to the Binary to

Excess-1 converter is designed with AOI implementation.

The modified BEC is designed in 130 nm technology. The

modified3-bit BEC is shown in the Fig.10.

Fig.10.Schematic view of modified 3-bit BEC-1 converter.

Fig11. Schematic view of 4 bit proposed SQRT CSLA.

Based on this modification 4, 8, 16-bit SQRT CSLA

architecture have been developed and compared with the

SQRT CSLA architecture using AOI implementation of EXOR gate used in BEC-1 converter. The proposed SQRT

CSLA is designed in 130 nm technology. The proposed

design has reduced area and power as compared with the

SQRT CSLA using ordinary BEC-1 converter. The proposed

SQRT Carry Select Adder is designed in 130 nm technology.

The proposed design has reduced area and power as

compared with the regular SQRT CSLA.

IV.RESULT

The Electric tool is used for the schematic generation and

also for the layout generation. By this we can generate the

spice netlist for the LT-SPICE code which is used for the

checking the waveforms and the generation of the results.

The proposed SQRT Carry Select Adder is designed in 130

nm technology. And also we can calculate the average power

of the circuit and the theoretical area used by the circuit.

International Journal of Scientific Engineering and Technology Research

Volume.03, IssueNo.44, December-2014, Pages: 8927-8932

High Speed and Power Optimized Scalable Comparator using Parallel Prefix Tree

A.3-bit Modified Binary to Excess-1 Converter LAYOUT

Design

Fig14.Timing diagram of 4-bit proposed SQRT CSLA in

130nm technology.

Fig12. Layout design of 3-bit Modified Binary to Excess-1

Converter in 130nm technology.

Fig.12 shows the layout design of modified 3-bit BEC in

130 nm technology. It consists two modified EX-OR gates,

one AND gate and one inverter. The advantages of modified

BEC are area and power consumption reduced compared to

the regular BEC.

B.4-bit Proposed SQRT CSLA LAYOUT Design

Fig15.Power analysis of 4-bit proposed SQRT CSLA in

130nm technology.

Table V. comparison of area and power consumption of

Regular SQRT CSLA, Modified SQRT CSLA, and

Proposed SQRT CSLA.

Fig13.Proposed layout design of 4-bit SQRT CSLA in

130nm technology.

Fig.13 shows the layout design of proposed 4-bit SQRT

CSLA in 130nm technology. It consists two 2-bit RCA, one

modified BEC and one 6:3 multiplexer. The power

dissipation of proposed 4-bit SQRT CSLA in 130nm

technology is 37.84µw is shown in the Fig.15.

International Journal of Scientific Engineering and Technology Research

Volume.03, IssueNo.44, December-2014, Pages: 8927-8932

G.NALINI, KONDAVEETI SUDHARANI

Table V. shows area and power consumed by the 4-bit, 8bit, 16-bit proposed SQRT Carry Select Adders. The

proposed SQRT CSLA is designed in 130nm technology has

less power consumption and less area compared to the

existence techniques.

V.CONCLUSION

A simple design is proposed for implementing the SQRT

Carry Select Adder with the help of Ripple Carry Adder for

Cin=0 and Binary to Excess-1 converter with 12 transistor

XOR gate. The SQRT Carry Select Adder is designed in

130nm technology. The reduction in the number of

transistors of this work offers great advantage in terms of

area and power. The proposed design has reduced area and

power as compared with the regular SQRT CSLA with dual

Ripple Carry Adders for Cin=0 and Cin=1 and modified Carry

Select Adder. This work evaluates the performance of the

proposed designs in terms of area and power. The results

analysis shows that the proposed CSLA structure is better

than the regular SQRT CSLA and modified SQRT CSLA.

This work can be further extended for higher number of bits.

New architectures can be designed with less number of

transistors and developed to achieve the better results in

terms of area, power and delay.

VI. REFERENCES

[1] Anantha P.Chandrakasan and Samuel Sheng “Low-Power

CMOS Digital Design” IEEE Journal Of Solid-State

Circuits.Vol.27, No.4, April 1992.

[2] E. Abu-Shama and M. Bayoumi “A New Cell for Low

Power Adders” IEEE 1996.

[3] Chetana Nagendra, Mary Jane Irwin, and Robert Michael

Owens “Area-Time-Power Trade-offs in Parallel Adders”

IEEE Transactions on Circuits and Systems-11: Analog And

Digital Signal Processing, Vol. 43, No. 10, October 1996.

[4]J. BEDRIJ “Carry Select Adder” IRE Transactions On

Electronic Computers.

[5] AKHILESTHY AG “A Reduced Area Scheme for CarrySelect Adders” IEEE 1990.

[6] Yotmgjoon Kim and Lee-Sup Kim “A Low Power Carry

Select Adder With Reduced Area” IEEE 2001.

[7] B. Ramkumar and Harish M Kittur “Low-Power and

Area-Efficient Carry Select Adder” IEEE Transactions On

Very Large Scale Integration (VLSI) Systems, VOL. 20, NO.

2, February 2012.

[8]. Shivani Parmar,Kirat Pal Singh “Design of high speed

hybrid carry select adder”IEEE 2012.

[9]. Partha Mitra1, Debarshi Datta “Low Power High Speed

SQRT Carry Select Adder” IOSR Journal of VLSI and Signal

Processing (IOSR-JVSP) Volume 1, Issue 3 (Nov. - Dec.

2012).

International Journal of Scientific Engineering and Technology Research

Volume.03, IssueNo.44, December-2014, Pages: 8927-8932