Physical Design of Digital Integrated Circuits (EN0291 S40)

advertisement

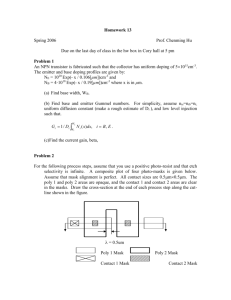

Physical Design of Digital Integrated Circuits (EN0291 S40) Sherief Reda Division of Engineering, Brown University Fall 2006 Lecture 01: the big picture • • • • Course objective Brief tour of IC physical design Projects overview Survey of papers and industry products Class objective(s): circuit (gates) → masks • Study various physical implementation methodologies • At 65nm and beyond, discuss some of the latest research challenges and techniques physical design • Survey the main industrial physical implementation tools • Conduct a research project on a recent, relevant problem [Photograph courtesy of AMD] Masks for manufacturing ICs What do designers really care about? • Design Objectives: – – – – Power (dynamic/static) Timing (frequency) Area (cost/yield) Yield (cost) • Challenges: – – – – – Manufacturing technology Leakage power Interconnect delay Variability Reliability Circuit entities eventually are either transistors or interconnects NMOS transistor Metal interconnects How do you manufacture them? How do ICs get manufactured? UV light Mask oxygen exposed exposed photoresist photoresist photoresist photoresist Silicon Silicon dioxide dioxide oxide oxide Silicon substrate Exposed Photoresist Mask-Wafer Coating Alignment and Exposure Photoresist rr w wee PPooo RFF R r we Po RF r we Po RF Ionized CF4 gas photoresist photoresist oxide oxide Dopant gas Ionized oxygen gas oxide oxide oxygen gate gate oxide oxide Oxide Etch Photoresist Strip Scanning ion beam Oxidation (Gate oxide) re sis t silicon silicon nitride nitride G ox S D Ion Implantation S D Active Regions S G D Nitride Deposition Ionized CCl4 gas Silane gas polysilicon polysilicon Polysilicon Deposition Contact holes top nitride G Photoresist Develop G D S G Contact Etch [Advanced Micro Devices from Quirck/Serda] ppoo llyy g gaa ttee Oxidation (Field oxide) oxide oxide Polysilicon Mask and Etch Metal contacts G G drain D S Metal Deposition and Etch [Check out this too http://www.appliedmaterials.com/HTMAC/animated.html] And the end result is: A very brief tour of physical design gate-level circuit floorplanning placement Timing analysis repeater insertion Parasitic extraction clock tree synthesis P/G network / routing Power analysis floorplanning placement Clock Tree Metal Wires mask mask after OPC Signal Integrity metal fill insertion mask generation / OPC reticles Class breakup Topic i main ideas and techniques (sreda) Topic i+1 main ideas and techniques (sreda) 5-10 minute break 5-10 minute break Topic i-1 papers / industrial tool survey (class participation) Topic i papers / industrial tool survey (class participation) • Class participation (30% of final grade) • Class project (70% of final grade) Lecture 01: the big picture • • • • Course objective Brief tour of IC physical design Projects overview Survey of papers and industry products Topic 01: CMOS scaling theory critical dimension Year CD (nm) ‘98 ‘00 ‘02 ‘04 ‘07 ‘10 ‘13 ‘16 ‘19 250 180 130 90 65 45 32 22 16 • How does scaling impact transistor and interconnect performance? • How does scaling continuously present new challenges to physical design? And how does it make some techniques obsolete • What is the fundamental limits to scaling (how far can we go)? Topic 01: CMOS scaling theory [ITRS’03] active [Moore, ISSCC’03] leakage global (no repeaters) gate delay local (scaled) global wires (repeaters) Topic 02: Process variability At 180nm and beyond, random sources of variation affect IC performance random sources process runtime dopant fluctuations temperature gate oxide thickness IR drop gate length/width variations 1.4 1.3 Normalized 1.2 Frequency 1.1 1.0 0.9 30% • 20x 0 5 15 20 10 Normalized Leakage [source: Intel @ 180nm] → Performance/power is no longer deterministic, but rather a random variable with an associated probability distribution Topic 03: Static timing analysis (STA) C17 from ISCAS’85 benchmarks I1 I2 O1 I3 I4 I5 I6 O2 • What is the worst delay of this circuit? → determines the frequency of operation • What are the critical path(s) that lead to this delay? → perhaps timing can be improved if we adjust them Topic 03: Static Timing Analysis (STA) hold time inputs Combinational logic outputs clock FFs FF input clock setup time • STA checks for any setup/hold time violations • At 130nm and below, transistor performance is no longer deterministic → gate delay is not exact → Statistical static timing analysis (academic papers survey) Topic 04: Power analysis and optimization • Total Power = static + dynamic + short factors voltage trans. time switching freq NMOS transistor Vdd A Z CMOS inverter factors capacitance switching frequency Leakage factors voltage transistor width/length, threshold Voltage Optimizations temperature tweak these factors to minimize power with little impact on performance Topic 05: Floorplanning and placement [IBM BigBlue4 2.1M instances] • A chip has only a limited resources of metal (for interconnects) ¾ minimizing placement total wirelength minimizes chip’s area • Delay is dominated by interconnects ¾ minimizing the wirelength of critical nets optimizes performance • Wire capacitance contributes to dynamic power ¾ minimizing the wirelength of high-frequency nets reduces power Topic 05: Floorplanning and placement rows I/O pads Floorplanning (chip outlining) is a small scale 2-D assignment problem ⇒ determines positions for large blocks of logic/memory [legal placement] [illegal placement] Placement of standard cells is a large-scale 2-D assignment problem ⇒ determines positions for thousands/millions of standard cells Topic 06: Clock tree synthesis • Clock net(s) → delivers the periodic generated clock signal to FFs • Design objectives: minimum (ideally zero) skew minimum wirelength minimize buffers for signal integrity data Minimum wirelength zero-skew tree for 64 FFs FF FF minimize demand on metal resources and reduces power extra delay clock minimize #buffers and maintain SI [Kahng et al., TCAS’92] skew can lead to setup/hold times violations Topic 07: Buffering (repeater insertion) for timing and signal integrity ¾ Delay of interconnect is a quadratic function in its length ¾ can be an unacceptable for global wires ¾ example: Itanium (180nm) requires 6 repeaters to span die ¾ Repeater insertion buffers wire capacitance and reduces overall delay x delay Distance x Topic 07: Buffering (repeater insertion) for timing and signal integrity The situation is complicated in case of multi-pin nets: sink What is the minimum number of repeaters to meet timing on this net? source Repeater estimation for Itanium sink Repeater Stations Topic 08: Design and analysis of power supply networks [Blaauw et al., DAC98] • Power supply network delivers Vdd/Gnd signals to all components. Main challenges: 1. IR drop: voltage at delivery point is degraded than the ideal voltage • performance drop • signal integrity problems PowerPC 750 power grid 2. electromigration PowerPC 750 IR-drop map Topic 09: Routing and parasitic extraction Objective: determine routes (tracks, layers, and vias) for each net such that the total wirelength is minimized. ¾ Be careful with routing critical nets and clock nets pin p1 cell congestion pin p2 Do you want this to happen to a net that belongs to the critical path?! Topic 09: Routing and parasitic extraction ¾ Multi-pin nets add more complexity in routing create vias sink map to layers source sink ¾ After all routes are determined, you can calculate the parasitic capacitance between each wire and its neighbors Topic 10: Design for manufacturability (DFM) Recent problems at manufacturing such as • variability (in polysilicon length control, oxide thickness, dopant) • chemical mechanical polishing alter design performance and calls for tighter integration between the manufacturing process and the design process design starting from 180nm manufacturing [Orshansky, TCAD00] ⇒ DFM is a probably misnomer! (since when were we physically designing circuits that are not for manufacturing!)` Topic 10: Design for Manufacturing example: fill insertion Downforce Wafer carrier • CMP (chemical mechanical Wafer polishing) is executed for each layer before buildup ofRotating platen other layers Polishing pad Slurry dispenser Polishing slurry • How can metal fill insertion helps in smoothing surfaces? Features Area fill features [(animation is not technically correct!] [Photos are form Quirk/Serda] Post-CMP ILD thickness Topic 11: mask preparation and resolution enhancement techniques (RET) MEBES original layout GDSII fractured layout fractured layout into polygons (rectangles and trapezoids) ¾ Did we just forget something?! [mask writer] Topic 11: mask preparation and resolution enhancement techniques (RET) Light source 193nm OPC increases the amount of data generated from fracturing 130nm feature [Schellenberg, IEEE Spectrum’03] Extra topics: • FPGA physical design • IO assignment and packaging • Design rule checking Lecture 01: the big picture • • • • Course objective Brief tour of IC physical design Projects overview Survey of papers and industry products Project slides omitted Lecture 01: the big picture • • • • Course objective Brief tour of IC physical design Projects overview Survey of papers and industry products Guidelines for academic paper reviews • Describe the problem the paper addresses – – – – – Why is the problem relevant (past/now/future)? Has this problem been addressed before? If yes, what is the new here? If no, is it meaningful? Assume you solve the problem, how will this change the world? • Describe the methodology of the solution – Why is this a good solution? – Are they are any wrong/good assumptions/constraints? – Are there any approximations? How good are they? • Describe the experimental framework – – – – Benchmark / tools used (academic / industrial) Are the results compelling and competitive? Are the results possible to duplicate? Did the results proof beyond doubt that this is a useful approach Guidelines for industry Industrial tool survey • Describe the purpose of the tool and how it helps the IC designer. • Describe the main inputs/outputs of the tool. • Possibly describe the methodology used by the tool (search product sheets / websites / US patent office) • Describe the possible options taken by the tool • Describe the main strengths/weakness of the tool. • (Compare the competitiveness of the tool to other tools.) • Be simple and only explain what you understood (product review can be frustrating) • Present the tool from a technology point of view, not a software (or marketing) point of view (avoid marketing propaganda) • Check the possibility of getting a trial version. Sources for information on tools • • • • • • Company websites US Patent office Google EEtimes Deepchip.com Edn.com References • EDA for Integrated Circuits Handbook (Volume 2), Scheffer/Lavagno/G. Martin, CRC Press. • Algorithms for VLSI Physical Design Automation, Sherwani, 3rd Edition, KAP • Design of High-Performance Microprocessor Circuits, Chandraksan/Bowhill/Fox, IEEE Press. • CMOS VLSI Design, Weste/Harris, 3rd edition, AddisonWesley. • Semiconductor Manufacturing Technology, Quirk/Serda, Prentice Hall. Key Websites • • • • • • • • http://www.google.com http://www.eetimes.com http://www.deepchip.com http://www.uspto.gov/patft/index.html http://www.synopsys.com http://www.cadence.com http://www.dac.com http://www.itrs.net/