Critical Path Delay and Net Delay Reduced Tree Structure for

advertisement

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

Critical Path Delay and Net Delay Reduced

Tree Structure for Combinational Logic Circuits

Padmanabhan Balasubramanian, and R.T. Naayagi

the technology-mapping phase. A number of techniques

mentioned in [7] [8] [9] are technology-independent and aim

at reducing the depth of the networks by restructuring. Even

extraction of kernels, that can be shared, may lead to an

increase in the depth of the network as an associated effect.

This makes it clear that sharing logic is not always deemed to

be a good approach, when considering the issue of timing

optimization. A technique that performs logic decomposition

during technology mapping has been proposed in [10] [11].

However, the accuracy of this approach is traded off for a

higher computational cost. A recent activity [12] addresses the

issue of delay improvement through functional decomposition.

It actually builds on logic bi-decomposition of Boolean

functions [13] [14] and also uses weak algebraic factorization

operations. It implicitly relies upon OR disjunction for

functional bi-decomposition. Then it combines this strategy

with tree-height reduction of resulting Boolean expressions.

Though it results in timing optimization, vis-à-vis achieving

logic depth reduction, the quasi-algebraic decomposition was

normally performed on the minimized Disjunctive Normal

Form (DNF) [15], by recursively applying a combination of

Associative, Distributive and Commutative (ACD) laws.

This work considers another dimension, where a combine

operation is performed on the reduced Conjunctive Normal

Form (CNF) [15] of the original Boolean expression. The

combine operation is basically carried out as a post-processing

step after identifying the appropriate terms. We basically

combine the terms using the distributive axiom of Boolean

algebra (also known as D rule). We introduce a new

terminology to identify the terms, which when combined,

would result in compact tree structure for the sub-functions

composing the original function. Subsequently, this will

translate into a simple and compact logic tree construction for

the desired functionality. In view of the above, it becomes

clear that this method is clearly contrary to decompose and

factoring operations, which are performed on the reduced

DNF expression as in [12]. The latter method is extensively

used to a great advantage in [12], while we find that the

former provides much better optimization results, not only in

terms of logic depth and the delay component, but

subsequently with a simultaneous reduction in the resource

utilization factor as well, for various logic functions belonging

to different categories. Hence, here, the design space has been

much more thoughtfully and thoroughly exploited to include

another critical objective of utilizing lesser technology

resources for implementing the requisite Boolean

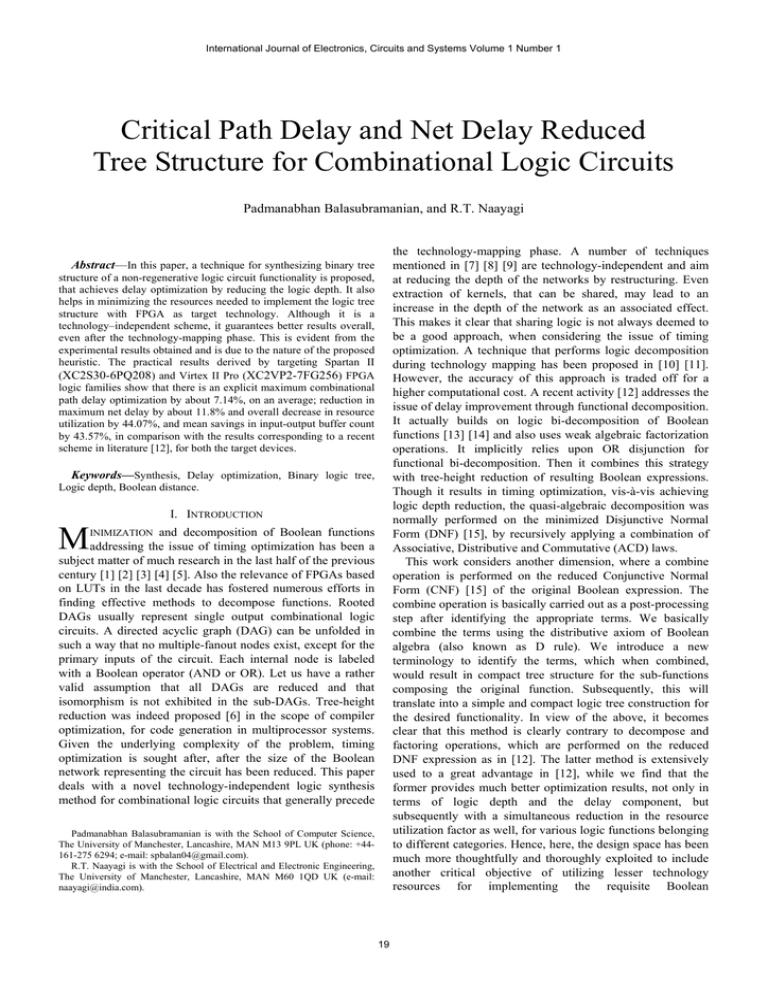

Abstract—In this paper, a technique for synthesizing binary tree

structure of a non-regenerative logic circuit functionality is proposed,

that achieves delay optimization by reducing the logic depth. It also

helps in minimizing the resources needed to implement the logic tree

structure with FPGA as target technology. Although it is a

technology–independent scheme, it guarantees better results overall,

even after the technology-mapping phase. This is evident from the

experimental results obtained and is due to the nature of the proposed

heuristic. The practical results derived by targeting Spartan II

(XC2S30-6PQ208) and Virtex II Pro (XC2VP2-7FG256) FPGA

logic families show that there is an explicit maximum combinational

path delay optimization by about 7.14%, on an average; reduction in

maximum net delay by about 11.8% and overall decrease in resource

utilization by 44.07%, and mean savings in input-output buffer count

by 43.57%, in comparison with the results corresponding to a recent

scheme in literature [12], for both the target devices.

Keywords—Synthesis, Delay optimization, Binary logic tree,

Logic depth, Boolean distance.

M

I. INTRODUCTION

INIMIZATION and decomposition of Boolean functions

addressing the issue of timing optimization has been a

subject matter of much research in the last half of the previous

century [1] [2] [3] [4] [5]. Also the relevance of FPGAs based

on LUTs in the last decade has fostered numerous efforts in

finding effective methods to decompose functions. Rooted

DAGs usually represent single output combinational logic

circuits. A directed acyclic graph (DAG) can be unfolded in

such a way that no multiple-fanout nodes exist, except for the

primary inputs of the circuit. Each internal node is labeled

with a Boolean operator (AND or OR). Let us have a rather

valid assumption that all DAGs are reduced and that

isomorphism is not exhibited in the sub-DAGs. Tree-height

reduction was indeed proposed [6] in the scope of compiler

optimization, for code generation in multiprocessor systems.

Given the underlying complexity of the problem, timing

optimization is sought after, after the size of the Boolean

network representing the circuit has been reduced. This paper

deals with a novel technology-independent logic synthesis

method for combinational logic circuits that generally precede

Padmanabhan Balasubramanian is with the School of Computer Science,

The University of Manchester, Lancashire, MAN M13 9PL UK (phone: +44161-275 6294; e-mail: spbalan04@gmail.com).

R.T. Naayagi is with the School of Electrical and Electronic Engineering,

The University of Manchester, Lancashire, MAN M60 1QD UK (e-mail:

naayagi@india.com).

19

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

functionality.

The remaining part of this paper is organized as follows. In

Section 2, we discuss the motivation for this work through an

illustrative example. We also introduce a new definition in

this section. In Section 3, we present our proposed heuristic

for construction of a tree structure representing the binary

DAG (BDAG) of the logic circuit. Section 4 depicts the

simulation results obtained for several Unate, Binate, Sum of

Disjoint Products (SoDP) and Product of Disjoint Sums

(PoDS) Boolean functions. The timing report description and

design summary is also listed in this section. We briefly

discuss the results in section 5 and conclude in section 6.

II. MOTIVATION FOR THE WORK

We highlight the inspiration behind this work by first

introducing a new definition and then explain the rationale

behind our approach with an illustrative example.

Fig. 1 BDAG created using ACD rules for (1)

III. PROPOSED BDAG CONSTRUCTION

A. Description of a Boolean term

A new terminology is proposed, namely the description set

of a Boolean term (sum term or product term). The description

set of a sum term [product term], shall be represented by the

notation D(Si) [D(Pi)]. D(Si) specifies the set of all literals in

their actual form, that the particular sum term Si is dependent

upon for its evaluation to a logic value of ‘0’ and D(Pi)

indicates the set of all literals in their respective actual form,

that a product term Pi depends upon for its evaluation to a

logic value of ‘1’.

For e.g.: If F = A’BD + B’CD’, where P1 = A’BD and P2 =

B’CD’ are two product terms; then D(P1) = {A’,B,D} and

D(P2) = {B’,C,D’}. Hence the description of a Boolean

function would be the union of the description sets of all its

individual terms. For the above example, it is given by,

D(F) = D(P1) ∪ D(P2).

The algorithm proposed for constructing a delay optimized

compact tree structure by means of reducing the network

depth of an arbitrary Boolean function, is given below.

A. Algorithm –Delay_Depth_Resources

Given a Boolean function F;

Minimize F into two-level logic;

Obtain the reduced product-of-sums-form, FPOS;

•

{Step 1: Let FPOS = (S1)

(S2)

….

(SN);

N → number of sum terms

Step 2: initialize I = 1, J = 2;

Step 3: Create an array of order [I:J], where I =

1,2,….,N-1 and J = 2,3,….,N

Step 4: Compute D(SI) ∪ D(SJ) | I ≠ J, I and J are

constants

Step 5: Enumerate | D(SI) ∪ D(SJ) | and save it in the

array file with index I and J;

Step 6: J = J+1;

Step 7: if J ≤ N then go to step 4

Step 8: else, I = I+1;

Step 9: if I > (N-1) then go to step 12

Step 10: else J = I+1;

Step 11: go to step 4;

Step 12: else, terminate the loops;

Step 13: if all elements in the array [I:J] = 0, then go to

step 26

Step 14: else, initialize I = 1, J = 2;

Step 15: sort the array element in the array [I:J]

Step 16: J = J + 1;

Step 17: if J ≤ N, then go to step 15

Step 18: else, find the array element with the maximum

value

Step 19: combine that SI with the corresponding SJ

using D rule [(a+b) (a+c) = a + bc]

Step 20: I = I+1;

Step 21: if I > (N-1) then go to step 24

Step 22: else, J = I+1;

•

•

•

•

B. Illustrative Example

Let us consider an example problem to tag our theoretical

observation with experimental result. We will characterize the

synthesized tree structure using a quadruple valued metric

(QVM) denoted by, QVM(MPD,MND,LD,BEL). MPD

represents the maximum path delay (in ns), MND refers to the

maximum net delay (in ns), LD denotes the logic depth of the

binary tree and BEL stands for the basic logic elements (LUTs

of FPGA) utilized for implementation of the logic tree. The

symbols

and

denote logical multiplication (AND)

and logical addition (OR) respectively and we will refer to

these as atomic operators (AO) [16].

Consider a reduced Boolean function, F(Q,R,S,T,U,V,W,X)

obtained using a two-level logic minimizer [17] as follows,

F = QRS + QT +QU + RWS + RWT + RWU

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

(1)

•

The logic tree structure for (1), created as per [12], is shown

in fig. 1. The quadruple valued metric for the same is denoted

by

QVMF(9.06,0.97,4,4)

for

Spartan

II

and

F

QVM (9.97,1.00,4,3) for Virtex II Pro FPGA logic families.

•

•

•

20

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

•

•

•

•

BDAG representation for the combinational circuits were

realized using the ACD rules employed by [12]. VHDL

coding were done for the functionalities using structural

modeling style and the design summary and timing report was

obtained after the place and route stage. The reduced

conjunctive normal forms for the functions can be obtained by

two methods; either by running a sum-of-products to productof-sums subroutine or by considering the complementary

phase of the function and a straightforward conversion to

reduced product-of-sums expression could be done. Next, the

terms were grouped in the manner based on our proposed

algorithm and distributive axiom was applied, so that the

functions now tend to comprise non-repetitive tree

functionality. Then the gate level netlist was created using the

atomic operators and VHDL coding in structural modeling

style was done. The design summary and timing reports were

extracted after post placement and routing phase. The

simulations were performed with Xilinx project navigator

suite targeting Spartan II and Virtex II Pro FPGA boards.

Table 1 gives a description of the comparison between the two

schemes in terms of atomic operators required and literal cost.

Table 2 shows the maximum combinational path delay or

critical path delay for the synthesized tree according to the

two different methods for Spartan II and Virtex II Pro logic

families. Table 3 mentions the maximum net delay values

obtained for the logic trees constructed according to the two

techniques for Spartan II and Virtex II Pro FPGA logic targets

respectively. Table 4 highlights the amount of basic logic

elements utilized (BEL) for the different techniques with

Spartan II and Virtex II Pro FPGA targets, while Table 5

gives an account of the input-output buffers required for the

two methods for realization with two different FPGA families.

Step 23: go to step 15

Step 24: obtain new FPOS;

Step 25: go to step 1;

Step 26: end of algorithm };

The heuristic given above can be used for obtaining a

factored sum-of-products form with the only exception being

that the D rule [ab + ac = a(b+c)] is used instead of that

mentioned in step 19. It is found that this heuristic when used

with a minimized sum-of-products expression results in the

same structure, as that which is obtained by [12]. The literal

cost of the final product-of-sums expression obtained from the

heuristic is estimated and the logic tree representing the

BDAG of the function is also created to determine the logic

depth. It is then compared with similar parameters of a

factored sum-of-products expression to arrive at a decision in

choosing the compact expression.

Based on the above heuristic for BDAG construction,

the resulting tree realization would be as shown in fig. 2. The

tree structure is characterized by: QVMF(7.90,0.89,4,2) for

Spartan II, and QVMF(9.03,0.89,4,2) for Virtex II Pro FPGA

logic family targets.

TABLE I

ATOMIC OPERATORS AND LITERAL COST COMPARISON

ACD_BDAG

P_BDAG

Function ID

Fig. 2 BDAG obtained using proposed algorithm for (1)

Z15

Z27

Z39

Z411

Z58

Z69

Z77

Z88

Z96

Z108

Z115

Z127

Z136

Z149

Z158

Z166

Z1711

Z1810

Z199

Z209

Z218

Z2210

The percentage improvement in critical path delay for the

above function (1), based on the proposed method, after the

technology mapping stage is found to be 12.8% and 9.43% for

implementation with Spartan II and Virtex II Pro

programmable logic families respectively. In terms of

maximum interconnect delay, the savings for the proposed

method compared with [12] was calculated and found to be

8.25% and 11% for the above logic families in order.

IV. SIMULATION METHODOLOGY AND RESULTS

A significant number of combinational logic functions in

canonical form of various types were considered to validate

and substantiate the theoretical conclusions with simulation

results. The functionalities in PLA format were first

minimized using a standard two-level logic minimizer,

ESPRESSO [17] and listed in Table 6 (made available in the

Appendix). Then the binary tree structures highlighting the

21

NAO

NIL

NAO

NIL

3

5

6

6

6

5

5

5

4

5

4

5

3

5

5

5

6

7

6

5

4

5

8

12

18

24

17

14

10

15

10

17

7

15

8

16

18

8

24

26

13

20

7

15

3

3

4

4

4

4

4

4

3

4

3

3

3

4

4

4

4

4

4

4

3

3

6

8

10

12

9

10

10

9

7

9

6

8

7

10

9

7

12

11

10

10

6

8

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

Z2310

Z2411

Z2512

Z2612

Z2714

Z2816

Z2912

Z3010

Z318

Z3211

Z3310

Z3412

Z3510

Z3615

Z3711

Z3811

Z3913

Z4014

TABLE III

MAXIMUM NET DELAY FOR SPARTAN II AND VIRTEX II PRO FPGA FAMILIES

Spartan II

Virtex II Pro

Function ID

(XC2S30-6PQ208)

(XC2VP2-7FG256)

ACD_BDAG P_BDAG ACD_BDAG P_BDAG

(in ns)

(in ns)

(in ns)

(in ns)

Z15

0.92

0.89

0.78

0.95

Z27

1.02

0.97

1.01

1.00

Z39

1.18

0.94

1.35

0.84

Z411

1.12

1.12

1.14

1.09

Z58

1.19

0.97

1.03

0.99

Z69

1.10

1.19

1.04

0.94

Z77

1.13

0.97

1.11

1.00

Z88

1.14

1.10

0.94

0.99

Z96

0.97

0.89

1.00

0.89

Z108

1.13

1.10

0.97

0.95

Z115

0.89

0.89

0.89

1.00

Z127

1.14

0.97

1.00

0.97

Z136

0.97

0.89

1.03

0.84

Z149

1.13

0.94

1.24

0.99

Z158

1.11

0.97

1.06

0.89

Z166

0.92

0.89

1.34

1.01

Z1711

1.22

1.17

0.94

1.29

Z1810

1.05

1.14

1.04

1.27

Z199

1.17

1.08

1.03

1.27

9

Z20

1.19

1.12

1.16

0.99

Z218

1.42

0.99

1.22

1.00

Z2210

1.33

1.00

1.38

0.84

Z2310

1.18

1.15

1.06

0.84

Z2411

1.39

1.01

1.22

1.29

Z2512

1.38

1.06

0.77

1.02

Z2612

1.00

0.97

1.19

1.02

Z2714

1.12

0.94

1.19

1.25

Z2816

1.06

0.94

1.65

1.12

Z2912

1.39

0.87

1.00

1.08

Z3010

1.15

1.17

1.29

0.84

Z318

1.54

1.17

0.93

1.00

Z3211

1.33

1.19

1.22

1.29

Z3310

1.52

1.14

1.38

0.84

Z3412

1.25

1.12

0.77

1.20

Z3510

1.13

0.94

1.29

0.84

Z3615

1.13

0.97

1.52

1.05

Z3711

1.39

0.87

1.48

1.20

Z3811

1.38

0.94

1.69

1.02

Z3913

1.16

1.00

1.24

1.25

Z4014

1.13

0.94

1.16

1.11

3

8

3

7

5

16

4

10

5

18

4

9

5

8

4

7

6

24

4

12

7

26

4

11

6

13

4

10

5

20

4

10

3

8

3

6

5

12

3

8

6

18

4

10

6

24

4

12

6

17

4

9

5

14

4

10

5

10

4

10

5

15

4

9

4

10

3

7

5

17

4

9

ZIN; I – Function identity, N – Number of inputs;

NAO – Number of atomic operators; NIL – Number of input literals

TABLE II

MAXIMUM COMBINATIONAL PATH DELAY FOR SPARTAN II AND VIRTEX II PRO

FPGA LOGIC FAMILY TARGETS

Spartan II

Virtex II Pro

Function ID

(XC2S30-6PQ208)

(XC2VP2-7FG256)

ACD_BDAG P_BDAG ACD_BDAG P_BDAG

(in ns)

(in ns)

(in ns)

(in ns)

Z15

8.00

7.75

9.38

8.86

Z27

9.45

9.35

9.57

9.87

Z39

10.37

9.23

9.53

9.65

Z411

9.93

9.17

9.61

9.97

Z58

10.19

9.07

10.15

9.62

Z69

9.66

8.27

9.99

9.43

Z77

8.31

9.35

10.21

9.87

Z88

9.55

8.27

9.73

9.43

Z96

9.06

7.90

9.97

9.03

Z108

9.69

8.27

9.11

8.86

Z115

7.97

7.77

10.10

9.87

Z127

9.61

9.35

9.87

9.11

Z136

9.35

7.97

9.93

9.65

Z149

9.68

9.23

9.79

9.62

Z158

10.27

9.07

9.21

9.03

Z166

8.00

7.90

10.77

9.69

Z1711

10.56

9.24

10.23

10.33

Z1810

10.79

8.68

10.11

10.40

Z199

9.86

8.80

9.94

10.39

Z209

10.37

8.38

9.74

9.43

Z218

11.50

9.25

10.44

9.87

Z2210

9.74

9.45

9.94

9.65

Z2310

10.98

9.26

10.07

9.65

Z2411

9.97

9.95

10.49

10.38

Z2512

10.69

9.77

9.67

9.83

Z2612

9.51

9.35

12.44

9.93

Z2714

10.36

9.23

10.20

10.64

Z2816

9.63

9.23

12.44

10.42

Z2912

10.62

8.47

10.22

9.60

10

Z30

10.26

9.44

10.31

9.65

Z318

11.46

9.47

9.98

9.87

Z3211

10.21

9.76

10.49

10.38

Z3310

10.92

9.69

10.39

9.65

Z3412

11.24

9.05

9.67

10.19

Z3510

9.68

9.23

10.31

9.65

Z3615

9.70

9.35

12.23

9.37

Z3711

10.62

8.47

9.93

10.19

Z3811

10.63

9.23

12.22

9.91

Z3913

10.35

9.45

10.37

9.67

Z4014

9.68

9.23

9.91

9.75

ACD_BDAG – ACD rules based BDAG construction [12] and

P_BDAG – Proposed BDAG realization

TABLE IV

BASIC LOGIC ELEMENTS UTILIZATION WITH SPARTAN II AND VIRTEX II PRO

TARGETS

Function ID

Z15

Z27

Z39

Z411

Z58

Z69

Z77

Z88

Z96

Z108

Z115

Z127

Z136

Z149

Z158

Z166

22

Spartan II

(XC2S30-6PQ208)

ACD_BDAG P_BDAG

3

6

7

9

7

5

4

6

4

7

2

6

3

7

7

3

2

3

5

5

3

3

3

3

2

3

2

2

2

5

3

2

Virtex II Pro

(XC2VP2-7FG256)

ACD_BDAG P_BDAG

3

6

7

9

7

5

4

6

4

7

2

6

3

7

7

3

2

3

5

5

3

3

3

3

2

3

2

2

2

5

3

2

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

Z1711

Z1810

Z199

Z209

Z218

Z2210

Z2310

Z2411

Z2512

Z2612

Z2714

Z2816

Z2912

Z3010

Z318

Z3211

Z3310

Z3412

Z3510

Z3615

Z3711

Z3811

Z3913

Z4014

9

11

5

5

13

7

12

8

10

6

8

7

9

8

12

9

13

12

7

6

9

8

8

7

5

5

4

3

5

5

5

7

7

3

5

5

5

5

5

6

5

4

5

3

5

5

5

5

9

11

5

5

13

7

12

8

10

6

8

7

9

8

12

9

13

12

7

6

9

8

8

7

Z3913

Z4014

5

5

4

3

5

5

5

7

7

3

5

5

5

5

5

6

5

4

5

3

5

5

5

5

9

15

19

25

18

15

11

16

11

18

8

16

9

17

19

9

25

27

14

21

37

19

33

21

24

16

24

18

22

20

33

23

37

34

18

16

22

24

7

9

11

13

10

11

9

10

8

10

7

9

8

11

10

8

13

12

11

11

17

13

13

15

16

9

11

11

12

13

12

15

17

13

11

9

12

11

9

15

19

25

18

15

11

16

11

18

8

16

9

17

19

9

25

27

14

21

37

19

33

21

24

16

24

18

22

20

33

23

37

34

18

16

22

24

13

11

20

18

13

11

V. DISCUSSION OF RESULTS

At the technology independent stage, we find that with

respect to the atomic operators and literal cost, the proposed

method enabled savings of 26.73% and 40% respectively.

From the experimental results obtained, we find that the

average improvement in critical path delay or longest path

delay for the proposed method has been 9.81% and 4.48% for

Spartan II and Virtex II Pro FPGA logic families respectively;

while the mean reduction in maximum net delay for the

proposed algorithm over the ACD rules based heuristic has

been 13.79% and 9.81% for Spartan II and Virtex II Pro

technology targets. The corresponding decrease in resource

utilization (BEL) for the logic families, stated in the above

order has been same and is around 44.07%, which is

significant. Even with respect to the number of input-output

buffers required for implementation of the functionality, the

proposed method effects considerable savings to the tune of

43.57% for both Spartan II and Virtex II Pro FPGA targets.

Fig. 3 and fig. 4 show the comparison in the number of

atomic operators and literal count needed for implementing

the Boolean tree structure corresponding to a combinational

logic functionality. Fig. 5 and fig. 6 depict the difference in

the maximum combinational path delay between the two

methods with Spartan II and Virtex II Pro as FPGA target

families; fig. 7 and fig. 8 show the variation in maximum net

delay for comparison of a similar sort as above. Fig. 9

graphically depicts the number of basic logic elements (BEL LUTs of a FPGA) for the two schemes with Spartan II and

Virtex II Pro targets, while fig. 10 highlights the input-output

buffer requirement for a similar comparison.

TABLE V

INPUT-OUTPUT BUFFER COUNT COMPARISON WITH SPARTAN II AND VIRTEX II

PRO FPGA LOGIC TARGETS

Spartan II

Virtex II Pro

Function ID

(XC2S30-6PQ208)

(XC2VP2-7FG256)

ACD_BDAG P_BDAG ACD_BDAG P_BDAG

Z15

Z27

Z39

Z411

Z58

Z69

Z77

Z88

Z96

Z108

Z115

Z127

Z136

Z149

Z158

Z166

Z1711

Z1810

Z199

Z209

Z218

Z2210

Z2310

Z2411

Z2512

Z2612

Z2714

Z2816

Z2912

Z3010

Z318

Z3211

Z3310

Z3412

Z3510

Z3615

Z3711

Z3811

20

18

7

9

11

13

10

11

9

10

8

10

7

9

8

11

10

8

13

12

11

11

17

13

13

15

16

9

11

11

12

13

12

15

17

13

11

9

12

11

VI. CONCLUSION

This work primarily focuses on a technology-independent

synthesis technique for non-regenerative logic circuits [18]

that typically precedes the technology-mapping phase. An

effective technique to address the important issue of timing

improvement by means of reducing the logic depth in a binary

logic tree realization is discussed in this paper. A good degree

of correlation exists between the depth of the Boolean

network at the technology-independent stage represented by a

tree and the practical worst case delay value obtained

experimentally; though it turns out to be contrary in very few

cases after the technology-mapping phase. The approach

seems to yield optimization in results for a wide variety of

functions which tend to have compact conjunctive normal

forms in comparison with disjunctive normal forms, in terms

of literal count. We have been able to obtain good

optimization with respect to critical delay by reducing the

logic depth and subsequently lesser resource utilization when

mapped onto a technology target. The effectiveness of our

contribution is supported by improved results of reachability

along the computationally intensive path. From extensive

simulation studies, we infer that the proposed algorithm is

promising, as it enables good timing optimization by means of

23

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

depth reduction in parallel. So far we have succeeded in

addressing some of the concerns raised in [12], by exploring

the available design space and achieved optimization in delay

by means of reducing logic depth and resources required for

physical realization of the desired non-regenerative logic

functionality.

Z39

Z37

Z35

Z39

Z33

Z37

Z31

Z35

Z29

Z33

Z27

Z31

Z25

Z27

Z23

F u n ctio n ID

Z29

Z25

Function ID

Z23

Z21

NIL : P_BDAG

NIL : ACD_BDAG

Z19

NAO : P_BDAG

Z21

Z17

NAO : ACD_BDAG

Z19

Z15

Z17

Z13

Z15

Z13

Z11

Z11

Z9

Z9

Z7

Z7

Z5

Z5

Z3

Z3

Z1

Z1

0

0

2

4

6

10

20

30

8

Literal cost comparison

Atom ic Operators com parison

Fig. 3 Comparison in terms of logical operators required

Fig. 4 Comparison with respect to number of input literals

24

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

We observe that a prudent decision would be to consider

the function representation corresponding to both the

minimized forms, factorize them according to the proposed

algorithm and then make a choice based on literal cost and

logic depth at the technology independent stage. For functions

with DNF forms more compact than its CNF forms, the

proposed heuristic returns the same results as that of [12],

while for the contrary, the approach enables decent delay

optimization whilst ensuring minimum resource utilization.

Our approach is pragmatic and promises improved

performance, evident from the practical results obtained for

the various sample cases considered for simulation studies.

Z39

Z37

Z35

Z33

Z31

Z29

Z39

Z37

Z27

Z35

Z25

Z33

Z23

Function Id

Z31

Z29

Z27

Z21

P_BDAG

ACD_BDAG

Z19

Z25

Z17

Function ID

Z23

P_BDAG

Z21

Z15

ACD_BDAG

Z19

Z13

Z17

Z15

Z11

Z13

Z9

Z11

Z7

Z9

Z7

Z5

Z5

Z3

Z3

Z1

Z1

0

5

10

0

15

5

10

15

Maxim um Com binational Path

Delay (in ns)

Maxim um Com binational Path

Delay (in ns)

Fig. 5 Critical path delay (in ns) for Spartan II FPGA target

Fig. 6 Critical path delay (in ns) for Virtex II Pro FPGA target

25

Z39

Z39

Z37

Z37

Z35

Z35

Z33

Z33

Z31

Z31

Z29

Z29

Z27

Z27

Z25

Z25

Z23

Z23

Z21

Function ID

Function ID

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

P_BDAG

ACD_BDAG

Z19

Z21

ACD_BDAG

Z19

Z17

Z17

Z15

Z15

Z13

Z13

Z11

Z11

Z9

Z9

Z7

Z7

Z5

Z5

Z3

Z3

Z1

Z1

0

0.5

1

1.5

2

P_BDAG

0

Maxim um Net Delay (in ns)

0.5

1

1.5

2

Maxim um Net Delay (in ns)

Fig. 8 Worst case net delay (in ns) with Virtex II Pro as target family

Fig. 7 Worst case net delay (in ns) with Spartan II as target family

26

Z39

Z39

Z37

Z37

Z35

Z35

Z33

Z33

Z31

Z31

Z29

Z29

Z27

Z27

Z25

Z25

Z23

Z23

Z21

F u n ctio n ID

Function ID

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

P_BDAG

ACD_BDAG

Z19

Z21

ACD_BDAG

Z19

Z17

Z17

Z15

Z15

Z13

Z13

Z11

Z11

Z9

Z9

Z7

Z7

Z5

Z5

Z3

Z3

Z1

Z1

0

5

10

15

P_BDAG

0

BEL utilization

10

20

30

40

Input-Output Buffers requirement

Fig. 9 Basic logic elements (LUTs in a FPGA) utilized for Spartan II and

Virtex II Pro families

Fig. 10 Input-Output buffer requirement for the two methods with Spartan II

and Virtex II Pro FPGA families as technology targets

27

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

Padmanabhan Balasubramanian received his B.E degree in Electronics and

Communication Engineering discipline from University of Madras, TN, India

in 1998 and his M.Tech in VLSI System from National Institute of

Technology, Tiruchirappalli, TN, India in 2005. He was earlier Lecturer in the

School of Electrical Sciences at Vellore Institute of Technology (University

and IET, UK Accredited), Vellore, TN, India. He is working towards his PhD

in the School of Computer Science at The University of Manchester,

Lancashire, UK. His research interests are in logic synthesis for low power,

asynchronous design; CMOS based design and timing optimization issues.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

R. Ashenhurst, “The decomposition of switching functions,” Proc. of

International Symosium. on Switching Theory, 1959, pp. 74-116.

J. Baer, and D. Bovet, “Compilation of arithmetic expressions for

parallel computations,” Proc. of IFIP Congress, 1968, pp. 340-346.

J. Beatty, “An axiomatic approach to code optimization for expressions,”

Journal of ACM, vol. 19(4), 1972, pp. 613-640.

R. Brayton, and C. McMullen, “The decomposition and factorization of

Boolean expressions,” Proc. of International Symposium on Circuits and

Systems, 1982, pp. 49-54.

J. Vasudevamurthy, and J. Rajski, “A method for concurrent

decomposition and factorization of Boolean expressions,” Proc. of

International Conf. on Computed-Aided Design, 1990, pp. 510-513.

D. Kuck, The Structure of Computers and Computation, Wiley, 1978.

K. Singh, A. Wang, R. Brayton, and A. Sangiovanni-Vincentelli,

“Timing optimization of combinational logic,” Proc. of IEEE/ACM

International Conf. on Computer-Aided Design, 1988, pp. 282-285.

K. Chen, and S. Muroga, “Timing optimization for multi-level

combinational circuits,” Proc. of ACM/IEEE Design Automation Conf.,

1990, pp. 339–344.

H.Touati, H.Savoj, and R.Brayton, “Delay optimization of

combinational circuits by clustering and partial collapsing,” Proc. of

IEEE/ACM International Conf. on Computer-Aided Design, 1991, pp.

188-191.

Eric Lehman, and Yosinori Watanabe, “Logic Decomposition during

Technology Mapping,” Proc. of IEEE/ACM International Conf. on

Computer-Aided Design, 1995, pp. 264-271.

E. Lehman, Y. Watanabe, J. Grodstein, and H. Harkness, “Logic

decomposition during technology mapping,” IEEE Transactions on CAD

of Integrated Circuits and Systems, vol. 16(8), August 1997, pp. 813834.

J. Cortadella, “Timing-Driven Logic Bi-Decomposition,” IEEE

Transactions on CAD of Integrated Circuits and Systems, vol. 22(6),

June 2003, pp. 675–685.

S. Yamashita, H. Sawada, and A. Nagoya, “New methods to find optimal

nondisjoint bi-decompositions,” Proc. of ACM/IEEE Design Automation

Conf., 1998, pp. 59-68.

A. Mishchenko, B. Steinbach, and M. Perkowski, “An algorithm for bidecomposition of logic functions,” Proc. of ACM/IEEE Design

Automation Conf., 2001, pp. 282-285.

Zvi Kohavi, Switching and Finite Automata Theory, McGraw Hill, 1999.

Srinivas Devadas, Abhijit Ghosh, and Kurt Kuetzer, Logic Synthesis

McGraw-Hill series on Computer Engineering, 1994.

P.C. McGeer, J.V. Sanghavi, R.K. Brayton, and A.L. SangiovanniVincentelli, “ESPRESSO-SIGNATURE: a new exact minimizer for

logic functions,” IEEE Transactions on VLSI Systems, vol. 1(4),

December 1993, pp. 432-440.

M.Fujita, and R.Murgai, “Delay estimation and optimization of logic

circuits: a survey,” Proc. of Asia South Pacific Design Automation

Conference, 1997, pp. 25-30.

R.T. Naayagi received her B.E degree in Electrical and Electronics

Engineering from Bharathidasan University, TN, India by securing University

I Rank with Gold Medal in 2000. She was conferred the T.R. Rajagopalan

Award for the Best Outgoing Female Graduate of her batch (1996-2000). She

completed her M.Sc in Information Technology from Alagappa University,

TN, India in 2003. She subsequently obtained her M.E degree with

specialization in Power Electronics and Drives from Anna University, TN,

India in 2005, by securing University II Rank. She has received several

scholarships and merit certificates in her academics for outstanding

performance. She also received the Best Outstanding Master’s Student Award

in 2005 in her institution. She secured the Dorothy Hodgkin Postgraduate

Award in the School of Electrical and Electronic Engineering of The

University of Manchester, Lancashire, UK to pursue her PhD programme. Her

research interests include power electronic circuits and systems, special

machines and digital design.

28

International Journal of Electronics, Circuits and Systems Volume 1 Number 1

APPENDIX

Function ID

TABLE VI

BOOLEAN FUNCTION IDENTITY AND MINIMIZED FUNCTION DESCRIPTION

Reduced two-level logic from ESPRESSO [17]

Z15

agb+agc+abf+fc

Z2

7

Z39

Z4

11

Z58

Z69

Z77

Z88

Z96

Z108

Z115

Z127

Z136

Z149

Z158

Z166

Z1711

Z1810

Z199

Z209

Z218

Z2210

Z2310

Z2411

Z2512

Z2612

Z2714

Z2816

Z2912

Z3010

Z318

Z3211

Z3310

Z3412

Z3510

Z3615

Z3711

Z3811

Z3913

Z4014

afe+afd+afg+aec+cd+cg+abe+bd+bg

dbfcg+dbfgh+dbfi+dceg+eh+ei+adcg+ah+ai

mnqst+mnqu+mnqv+mnqw+msto+uo+vo+wo+mstp+up+vp+wp+mstr+ur+vr+wr

ijn+ijo+ijp+kin+ko+kp+inl+ol+pl+min+mo+mp

pqrsuvw+pqrsx+puvwt+xt

mnpq+mnpr+mnqo+ro

qrwx+qru+qrv+qwxs+su+sv+qwxt+tu+tv

bgc+bgd+bge+abc+ad+ae

abe+abf+abg+abh+aec+fc+gc+hc+aed+fd+gd+hd

stw+s’vu+uw

tru+trv+t’ws+us+vs+t’wq+qu+qv

pmr+p’qn+nr+p’qo+or

abch+abci+a’fgh+dh+di+a’fge+eh+ei

pmx+pmy+qp’v+qx+qy+p’vw+wx+wy+p’vu+ux+uy

mnr+m’pqo+or

ijkq+ijkr+ijks+i’opl+ql+rl+sl+i’opm+qm+rm+sm+i’opm+qn+rn+sn

mnv+mnw+mnx+m’uq+vq+wq+xq+m’ur+vr+wr+xr+m’us+vs+ws+xs+m’ut+vt+wt+xt

abci+a’ghd+di+a’ghe+ei+a’ghf+fi

wxn+wxo+wxp+wxq+w’my+ny+oy+py+qy+w’mz+nz+oz+pz+qz

pqrsm+pqrsn+pqrso+pqrsp+p’xyzt+mt+nt+ot+pt+p’xyzu+mu+nu+ou+pu+

p’xyzv+ mv+nv+ov+pv+p’xyzw+mw+nw+ow+pw

defgl+defgk+d’onmh+lh+kh+d’onmi+li+ki

ijp+ijq+ijr+ijs+i’ok+pk+qk+rk+sk+i’ol+pl+ql+rl+sl+i’om+pm+qm+rm+sm+

i’on+pn+qn+rn+sn

cdefgn+cdefgo+c’jklmh+nh+oh+c’jklmi+ni+oi

fghijq+fghijr+fghijs+f’mnopk+qk+rk+sk+f’mnopl+ql+rl+sl

a’be’f+a’bg+a’bh+ce’f+cg+ch+de’f+dg+dh

m’nr’s+m’nt+m’nu+m’nv+r’so+to+uo+vo+r’sp+tp+up+vp+r’sq+tq+uq+vq

i’jkn’op+i’jkq+i’jkr+n’opl+ql+rl+n’opm+ qm+rm

p’qrv’wx+p’qry+p’qrz+v’wxs+sy+sz+v’wxt+ty+tz+uv’wx+uy+uz

a’bcdg’hij+a’bcdk+a’bcdl+g’hije+ke+le+g’hijf+kf+lf

r’sx’y+r’sz+r’sm+r’sn+r’so+x’yt+zt+mt+nt+ot+x’yu+zu+mu+nu+ou+x’yv+

zv+mv+nv+ov+x’yw+zw+mw+nw+ow

c’defgjklmn+c’defgo+c’defgp+j’klmnh+ho+hp+j’klmni+io+ip

p’qrsx’yzm+p’qrsn+p’qrso+p’qrsk+p’qrsl+x’yzmt+nt+ot+kt+lt+x’yzmu+nu+

ou+ku+lu+x’yzmv+nv+ov+kv+lv+x’yzmw+nw+ow+kw+lw

i’jo’p+i’jq+i’jr+i’js+i’jt+o’pk+qk+rk+sk+tk+o’pl+ql+rl+sl+tl+o’pm+qm+

rmsm+tm+o’pn+qn+rn+sn+tn

a’bcf’gh+a’bci+a’bcj+f’ghd+id+jd+f’ghe+ie+je

g’hk’l+g’hm+g’hn+k’li+mi+ni+k’lj+mj+nj

o’pqu’vw+o’pqx+o’pqy+u’vwr+rx+ry+u’vws+xs+ys+u’wvt+xt+yt

e’fj’k+e’fl+e’fm+e’fn+j’kg+lg+mg+ng+j’kh+lh+mh+nh+j’ki+li+mi+ni

d’efgo’nml+d’efgk+d’efgj+o’nmlh+kh+jh+o’nmli+ki+ij

q’rsv’wx+q’rsy+q’rsz+v’wxt+yt+zt+v’wxu+uy+uz

ZXN; X – function ID, N – number of inputs

29