TSM2N100CP N-Channel Power MOSFET

advertisement

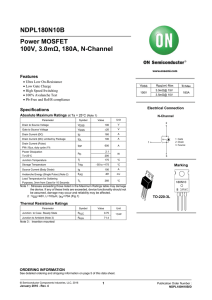

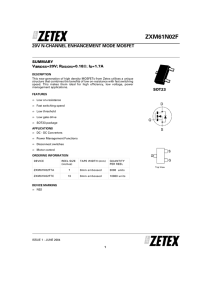

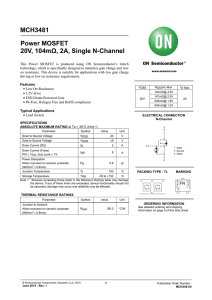

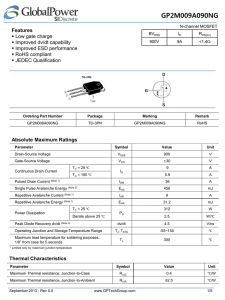

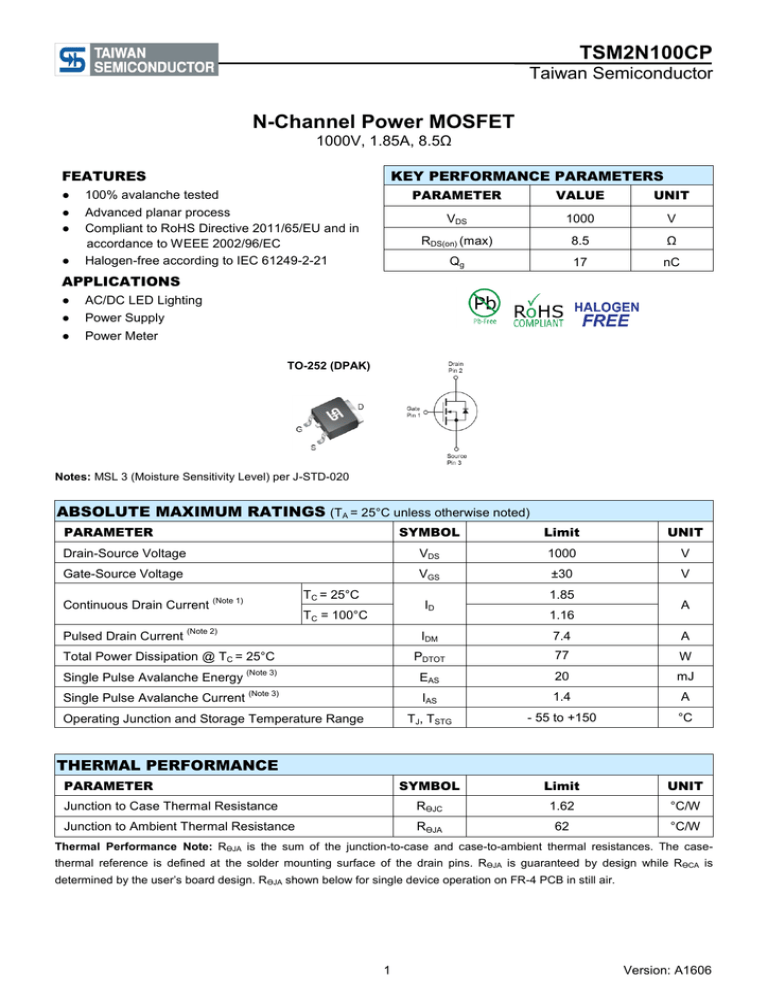

TSM2N100CP Taiwan Semiconductor N-Channel Power MOSFET 1000V, 1.85A, 8.5Ω FEATURES KEY PERFORMANCE PARAMETERS ● 100% avalanche tested ● ● Advanced planar process Compliant to RoHS Directive 2011/65/EU and in accordance to WEEE 2002/96/EC Halogen-free according to IEC 61249-2-21 ● PARAMETER VALUE UNIT VDS 1000 V RDS(on) (max) 8.5 Ω Qg 17 nC APPLICATIONS ● AC/DC LED Lighting ● Power Supply ● Power Meter TO-252 (DPAK) Notes: MSL 3 (Moisture Sensitivity Level) per J-STD-020 ABSOLUTE MAXIMUM RATINGS (TA = 25°C unless otherwise noted) PARAMETER SYMBOL Limit UNIT Drain-Source Voltage VDS 1000 V Gate-Source Voltage VGS ±30 V Continuous Drain Current Pulsed Drain Current TC = 25°C (Note 1) ID TC = 100°C (Note 2) 1.85 1.16 A IDM 7.4 A PDTOT 77 W Single Pulse Avalanche Energy (Note 3) EAS 20 mJ Single Pulse Avalanche Current (Note 3) IAS 1.4 A TJ, TSTG - 55 to +150 °C SYMBOL Limit UNIT Junction to Case Thermal Resistance RӨJC 1.62 °C/W Junction to Ambient Thermal Resistance RӨJA 62 °C/W Total Power Dissipation @ TC = 25°C Operating Junction and Storage Temperature Range THERMAL PERFORMANCE PARAMETER Thermal Performance Note: RӨJA is the sum of the junction-to-case and case-to-ambient thermal resistances. The casethermal reference is defined at the solder mounting surface of the drain pins. RӨJA is guaranteed by design while RӨCA is determined by the user’s board design. RӨJA shown below for single device operation on FR-4 PCB in still air. 1 Version: A1606 TSM2N100CP Taiwan Semiconductor ELECTRICAL SPECIFICATIONS (TA = 25°C unless otherwise noted) PARAMETER CONDITIONS SYMBOL MIN TYP MAX UNIT Static Drain-Source Breakdown Voltage VGS = 0V, ID = 250µA BVDSS 1000 -- -- V Gate Threshold Voltage VDS = VGS, ID = 250µA VGS(TH) 3.5 4.5 5.5 V Gate Body Leakage VGS = ±30V, VDS = 0V IGSS -- -- ±100 nA Zero Gate Voltage Drain Current VDS = 1000V, VGS = 0V IDSS -- -- 1 µA RDS(on) -- 6 8.5 Ω Qg -- 17 -- Qgs -- 5 -- Qgd -- 9 -- Ciss -- 625 -- Coss -- 38 -- pF Ω Drain-Source On-State Resistance (Note 4) Dynamic VGS = 10V, ID = 0.9A (Note 5) Total Gate Charge VDS = 800V, ID = 1.85A, Gate-Source Charge VGS = 10V Gate-Drain Charge Input Capacitance VDS = 25V, VGS = 0V, Output Capacitance f = 1.0MHz Reverse Transfer Capacitance Gate Resistance Switching Crss f = 1.0MHz, open drain nC 15 Rg -- 2.2 -- td(on) -- 31 -- tr -- 14 -- td(off) -- 78 -- tf -- 44 -- VSD -- -- 1.4 V (Note 6) Turn-On Delay Time Turn-On Rise Time VDD = 500V, RG = 25Ω, Turn-Off Delay Time ID = 0.9A, VGS = 10V Turn-Off Fall Time ns Source-Drain Diode Forward Voltage (Note 4) IS = 1.85A, VGS = 0V Reverse Recovery Time VR = 100V, IS = 1.85A trr -- 359 -- ns Reverse Recovery Charge dIF/dt = 100A/μs Qrr -- 1.34 -- μC Notes: 1. Current limited by package 2. Pulse width limited by the maximum junction temperature 3. L = 20mH, IAS = 1.4A, VDD = 50V, RG = 25Ω, Starting TJ = 25 C 4. Pulse test: PW ≤ 300µs, duty cycle ≤ 2% 5. For DESIGN AID ONLY, not subject to production testing. 6. Switching time is essentially independent of operating temperature. o ORDERING INFORMATION PART NO. TSM2N100CP ROG PACKAGE PACKING TO-252 (DPAK) 2,500pcs / 13” Reel 2 Version: A1606 TSM2N100CP Taiwan Semiconductor CHARACTERISTICS CURVES (TC = 25°C unless otherwise noted) Transfer Characteristics ID, Continuous Drain Current (A) ID, Continuous Drain Current (A) Output Characteristics VGS, Gate to Source Voltage (V) On-Resistance vs. Drain Current Gate-Source Voltage vs. Gate Charge VGS, Gate to Source Voltage (V) RDS(on), Drain-Source On-Resistance (Ω) VDS, Drain to Source Voltage (V) Qg, Gate Charge (nC) ID, Continuous Drain Current (A) Source-Drain Diode Forward Current vs. Voltage IS, Body Diode Forward Current (A) RDS(on), Drain-Source On-Resistance (Normalized) On-Resistance vs. Junction Temperature VSD, Body Diode Forward Voltage (V) TJ, Junction Temperature (°C) 3 Version: A1606 TSM2N100CP Taiwan Semiconductor CHARACTERISTICS CURVES (TC = 25°C unless otherwise noted) BVDSS vs. Junction Temperature VDS, Drain to Source Voltage (V) BVDSS (Normalized) Drain-Source Breakdown Voltage (V) C, Capacitance (pF) Capacitance vs. Drain-Source Voltage TJ, Junction Temperature (°C) ID, Continuous Drain Current (A) Maximum Safe Operating Area VDS, Drain to Source Voltage (V) Continuous Drain Current (A) Normalized Effective Transient Thermal Impedance Normalized Thermal Transient Impedance, Junction-to-Case 101 SINGLE PULSE RӨJC=1.62˚C/W 100 10-1 Duty=0.5 Duty=0.2 Duty=0.1 Duty=0.05 Duty=0.02 Duty=0.01 Single pulse 10-2 10-3 -5 10 10-4 10-3 Notes: Duty = t1 / t2 TJ = TC + PDM x ZӨJC x RӨJC 10-2 10-1 Square Wave Pulse Duration (s) 4 Version: A1606 TSM2N100CP Taiwan Semiconductor PACKAGE OUTLINE DIMENSIONS (Unit: Millimeters) TO-252 SUGGESTED PAD LAYOUT MARKING DIAGRAM Y = Year Code M = Month Code O =Jan P =Feb S =May T =Jun W =Sep X =Oct L = Lot Code (1~9, A~Z) Q =Mar U =Jul Y =Nov R =Apr V =Aug Z =Dec 5 Version: A1606 TSM2N100CP Taiwan Semiconductor Notice Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies. Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC’s terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right. The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale. 6 Version: A1606