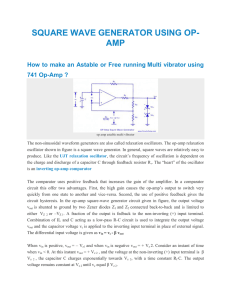

Design of an Op-Amp Gain Compensator for Switched

advertisement