MOS Field-Effect Transistors (MOSFETs) Review

advertisement

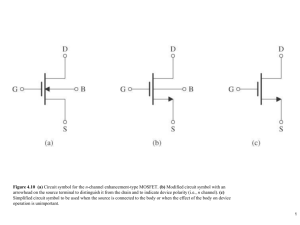

MOS Field-Effect Transistors (MOSFETs) Review 4.1 Device Structure and Physical Operation Figure 4.1 shows the physical structure of the n-channel enhancement-type MOSFET. Figure 4.1 Physical structure of the enhancement-type NMOS transistor: (a) perspective view; (b) cross-section. Typically L = 0.1 to 3 mm, W = 0.2 to 100 mm, and the thickness of the oxide layer (tox) is in the range of 2 to 50 nm. The transistor is fabricated on a p-type substrate. The notation n+ indicates 2 heavenly doped n-type regions. A thin layer of silicon dioxide (SiO2) of thickness tox (typically 2-50nm) which is an excellent insulator is grown on the surface substrate, covering the area between source and drain. Next metal is deposited to from a 4 terminal device: Terminals are labeled Source (S), Gate (G), Drain (D) and Body (B). Note that this configuration forms 2 back to back diodes. With no bias voltage applied to the gate, the back to back diodes prevent current conduction from drain to source when a voltage VDS is applied. Next consider the situation shown in Figure 4.2 Figure 4.2 The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate. Positive voltage applied at vGS causes the free holes (positive charge) to be repelled from the region of the substrate under the gate. These holes are push downward into the substrate, creating a carrier depletion region (depletion region is populated by negative charge due to the neutralizing holes that have been pushed down). In addition, the positive gate voltage attracts electrons from the n+ wells, creating an n region (channel) connecting the source and drain. Thus current can flow through this induced region. The MOSFET of figure 4.2 is referred to as a n-channel MOSFET (Note ann-channel MOSFET is formed in a p-type substrate. The value of vGS at which a sufficient number of mobile electrons accumulate in the channel region to form a conducting channel is called the threshold voltage and is denoted as (Vt). Vt ranges between 0.5 to 1.0V. Having induced a channel and applying a positive voltage vDS, between the drain and source (Figure 4.3) causes a current iD to flow through the induced channel. Figure 4.3 An NMOS transistor with vGS > Vt and with a small vDS applied. The device acts as a resistance whose value is determined by vGS. Specifically, the channel conductance is proportional to vGS – Vt’ and thus iD is proportional to (vGS – Vt) vDS. Note that the depletion region is not shown (for simplicity). Current is carried by free electrons from source to drain, thus by convention current flow iD is from drain to source. The magnitude of iD depends on the density of electrons in the channel, which depends on vGS>Vt. As vGS exceeds Vt, the channel increases and the resistance across the channel is reduced (or conductance increases). In fact, the conductance of the channel is proportion to the excess gate voltage (vGS-Vt), also known as the effective voltage or overdriven voltage. Thus the current iD increases and is proportional to (vGS-Vt) and vDS (Figure 4.4). Figure 4.4 The iD–vDS characteristics of the MOSFET in Fig. 4.3 when the voltage applied between drain and source, vDS, is kept small. The device operates as a linear resistor whose value is controlled by vGS. From Figure 4.4 it is seen that the resistance is infinite when vGS<Vt and its value decreases as vGS exceeds Vt. Increasing vGS above Vt enhances the channel, hence the name enhancementmode operation and enhancement-type MOSFET. Figure 4.5 illustrates the operation of the NMOS transistor as vDS is increased. For this purpose vGS let be held constant. Figure 4.5 Operation of the enhancement NMOS transistor as vDS is increased. The induced channel acquires a tapered shape, and its resistance increases as vDS is increased. Here, vGS is kept constant at a value > Vt. As we travel along the channel from source to drain, the voltage increases from 0 to vDS. The voltage between the gate and source is vGS, while the voltage between the gate and drain is vGS-vDS. The channel depth depends on this voltage, thus the channel is no longer of uniform depth. As vDS is increased the channel becomes more tapered and its resistance increases correspondingly. Thus the iD- vDS curve does not continue as a straight line but bends as shown in Figure 4.6 Figure 4.6 The drain current iD versus the drain-to-source voltage vDS for an enhancement-type NMOS transistor operated with vGS > Vt. When vGD=Vt or vGS - vDS = Vt or vDS= vGS – Vt: the channel depth at the drain end decreases to almost zero, and the channel is said to be pinched off. Increasing vDS beyond this point has little effect (theoretically) on the channel shape and the current iD remains constant. The transistor is turned off when vGS < Vt (cutoff region). When vGS > Vt, the transistor is on. The transistor is said to be in the triode region when vDS< vGS – Vt. The transistor is said to be in the saturation region when vDS>= vGS – Vt. (Note: Saturation in BJT means something completely different from that in a MOSFET. The saturation mode of BJT is analogous to the triode region of the MOSFET. The saturation region of the MOSFET corresponds to the active mode of BJT. 4.1.6 Relationship between iD-vDS. The relationship between iD-vDS based on the first order approximation is: W 1 2 i D n Cox (v GS Vt )v DS v DS (Triode region) L 2 1 W i D n C ox (v GS Vt ) 2 (Saturation region) 2 L or 1 i D K ( vGS Vt ) v DS v 2DS (Triode region) 2 1 i D K (v GS Vt ) 2 (Saturation region) 2 (Eq1) (Eq2) W . L C ox is capacitance per unit gate defined as C ox ox / t ox , where ox is the permittivity of the silicon oxide and t ox is the oxide thickness determined by the process technology. n is the mobility of the electrons in the channel called surface mobility. It is a physical parameter that depends on the process technology. L is the channel length and W is the channel width. The ratio of W/L is know as the aspect ratio of the MOSFET. The L and the W are selected by the circuit designer to obtain desired i– v characteristic. where K is a constant K n Cox Note when vDS is small (Eq1) becomes i D K (vGS Vt )v DS . This linear relationship was discussed in Figure 4.4 and represents the operation of the MOS transistor as a linear resistance as v 1 1 rDS DS K (VGS Vt ) K (VOV ) iD where VOV VGS Vt , and VOV is referred to as the gate-to-source overdrive voltage. 4.2.1 Circuit Symbol The circuit symbols for an NMOS transistor are shown in Figure 4.10. Figure 4.10 (a) Circuit symbol for the n-channel enhancement-type MOSFET. (b) Modified circuit symbol with an arrowhead on the source terminal to distinguish it from the drain and to indicate device polarity (i.e., n channel). (c) Simplified circuit symbol to be used when the source is connected to the body or when the effect of the body on device operation is unimportant. The polarity of the transistor is determined by the arrow. Circuit symbol a): Arrow at the body (B) indicates a p-type substrate (body), thus NMOS transistor. Circuit symbol b): Although a MOSFET is symmetrical device, it is often useful in circuit design to designate one terminal as the source and the other as the drain. To achieve this circuit symbol b is used. The arrow is placed on the source terminal and indicates an NMOS transistor. Circuit symbol c): The source is connected to the body. 4.2.2 The iD-vDS Characteristic. Figure 4.11 shows an n-channel enhancement-type MOSFET with voltages vGS and vDS applied. Figure 4.11b) shows 3 distinct regions of operations: The transistor is turned off when vGS < Vt. (cutoff region). When vGS > Vt, the transistor is on. The transistor is said to be in the triode region when vDS< vGS – Vt. The transistor is said to be in the saturation region when vDS>= vGS – Vt. Figure 4.11 (a) An n-channel enhancement-type MOSFET with vGS and vDS applied and with the normal directions of current flow indicated. (b) The iD–vDS characteristics for a device with k’n (W/L) = 1.0 mA/V2. The saturation region of the FET is used to operate as an amplifier. For operation as a switch, the cutoff and triode regions are utilized. In saturation mode, the MOSFET provides a drain current whose value is independent of the drain voltage vDS and is determined by the gate voltage vGS according to the square law relationship (i.e. i D ( K / 2)(vGS Vt ) 2 ). A sketch is shown in Figure 4.12. Figure 4.12 The iD–vGS characteristic for an enhancement-type NMOS transistor in saturation (Vt = 1 V, k’n W/L = 1.0 mA/V2). The large signal circuit equivalent model based on i D ( K / 2)(vGS Vt ) 2 is shown in Figure 4.13. Figure 4.13 Large-signal equivalent-circuit model of an n-channel MOSFET operating in the saturation region. 4.2.3 Finite Output Resistance in Saturation The large signal model of Figure 4.13 indicates that in saturation iD is independent of vDS. This implies that the resistance looking into the drain is infinite. However, this is based on the premise that once the channel is pinched off at the drained end and further increases in vDS have no effect on the channel’s shape. However increasing vDS in saturation mode, the channel pinch-off point is moved slightly away from the drain toward the source (Figure 4.15). The channel length is in effect reduced from L to L-L, a phenomenon known as channel-length modulation. Figure 4.15 Increasing vDS beyond vDSsat causes the channel pinch-off point to move slightly away from the drain, thus reducing the effective channel length (by DL). Since iD is inversely proportional to the channel length, iD increases with vDS. 1 W i D nC ox (v GS Vt ) 2 2 L To account for the dependence of iD on vDS 1 W i D n C ox (v GS Vt ) 2 (1 v DS ) 2 L where is a process-technology parameter with dimensions V-1. A typical set of iD-vDS characteristics showing the effect of channel-length modulation is shown in Figure 4.16. Figure 4.16 Effect of vDS on iD in the saturation region. The MOSFET parameter VA depends on the process technology and, for a given process, is proportional to the channel length L. To account for the dependence of iD on vDS the large signal model includes an output resistance ro, as shown in Figure 4.17. Figure 4.17 Large-signal equivalent circuit model of the n-channel MOSFET in saturation, incorporating the output resistance ro. The output resistance models the linear dependence of iD on vDS and is given by Eq. (4.22). The output resistance is defined as r0 V 1 A I D I D where ID 1 W n C ox (VGS Vt ) 2 2 L VA 1 4.1.7 The p-channel MOSFET. A p-channel enhancement-type MOSFET (PMOS), operates in the same manner as the n-channel device except that vGS and vDS are negative and the threshold voltage Vt is negative. Also, the current iD enters the source terminal and leaves through the drain terminal. For PMOS transistor The transistor is turned off when vGS > Vt (cutoff region). The transistor is on when vGS < Vt. The transistor is said to be in the triode region when vDS> vGS – Vt. The transistor is said to be in the saturation region when vDS<= vGS – Vt. The relationship between iD-vDS for the PMOS transistor is the same as the NMOS transistor: 1 i D K ( vGS Vt ) v DS v 2DS (Triode region) 2 1 i D K (vGS Vt ) 2 (Saturation region) 2 1 i D K (v GS Vt ) 2 (1 v DS ) (Saturation region [channel length modulation]) 2 W where K p Cox . For PMOS vGS, Vt, and vDS are all negative. L The circuit symbols for a PMOS transistor are shown in Figure 4.18. Figure 4.18 (a) Circuit symbol for the p-channel enhancement-type MOSFET. (b) Modified symbol with an arrowhead on the source lead. (c) Simplified circuit symbol for the case where the source is connected to the body. (d) The MOSFET with voltages applied and the directions of current flow indicated. Note that vGS and vDS are negative and iD flows out of the drain terminal. 4.2.5 The Role of the Substrate – Body Effect In many applications the source terminal S is connected to the substrate (or body) terminal B. In such a case the substrate does not play any role in circuit operation. If there is voltage difference between the source and the body VSB then this changes the threshold voltage Vt. Specifically, it has been shown that increasing the reverse substrate bias voltage VSB results in an increase in Vt as Vt Vto ( 2 f VSB 2 f ) where Vto is the threshold voltage for VSB=0 f is a physical parameter (typically 2 f =0.6V) is known as the body-effect parameter and is a fabrication-process parameter This phenomenon is known as body effect. The Junction Field Effect Transistor (JFET) As with other FET types, the JFET is available in 2 polarities: n-channel and p-channel. The basic structure of a n channel JFET is shown in Figure 5.2. The p-channel can be fabricated simply by reversing all the semiconductor types. The n region is the channel and the p-type regions are electrically connected together the gate. Thus the JFET is a 3 terminal device. When vGS=0V, the application of vDS causes current to flow from the drain to the source. When a negative vGS is applied, the depletion region of the gate-channel junction widens and the channel becomes correspondingly narrower; thus the channel resistance increases and the current iD decreases for a given vDS. One way to think of a JFET is as a resistance whose value is controlled by vGS. If vGS is increased in the negative direction, eventually a value is reached at which the depletion region occupies the entire channel. The channel has in effect disappeared (i.e. the channel is pinched), as shown in Figure 5.7. The JFET characteristics are displayed in Figure 5.10 and Figure 5.14, for threshold voltage Vt=Vp=-4V, IDSS=8mA. Although Figure 5.10, shows iD to be independent of vDS in the saturation region, this is an ideal situation. In fact JFETs also suffer from channel-length modulation. For JFETs the threshold voltage is usually called the pinch-off voltage and is denoted by Vp, thus Vp=Vt. For n-channel JFET Vp is negative. The JFET characteristics can be described by the same equations used for MOSFETs. The n-channel transistor is turned off (cutoff region) when vGS <= Vp. When 0 >= vGS > Vp, and vDS is positive the transistor is on. The transistor is said to be in the triode region when vDS< vGS – Vp. The transistor is said to be in the saturation region (pinch-off) when vDS>= vGS – Vp The equations relating iD and the applied voltages are 1 2 i D K ( vGS VP )v DS v DS (Triode region) 2 1 i D K (v GS VP ) 2 (Saturation region) 2 1 i D K ( vGS VP ) 2 (1 v DS ) (Saturation region [channel length modulation]) 2 where K 2 I DSS / VP2 . The current IDSS is the drain current when vGS=0V. 4.3 MOSFET Circuits at DC To keep the DC analysis simple the following assumptions Neglect channel-length modulation, (assume =0) Example 4.5 Determine the voltages at all nodes and currents through all branches. Let Vt=1V and K n Cox mA/V2. Assume =0 W =1 L Figure 4.23 (a) Circuit for Example 4.5. (b) The circuit with some of the analysis details shown. Example 4.6 Design the circuit so that the transistor operates in saturation with ID = 0.5mA and VD=3V. What is the largest value that RD can have while maintaining saturation region. Assume =0 Figure 4.24 Circuit for Example 4.6. Example 4.7 W W p Cox =1 mA/V2. Vtn=-Vtp=1V. L L Assume =0 for both devices. Find the drain currents iDN and iDP as well as the voltage vo for vI = 0V, -2.5V and 2.5V. The NMOS and PMOS transistors are matched K n Cox Figure 4.25 Circuits for Example 4.7. Example 4.9 Design a circuit to establish ID=0.5mA. Vt=1V, K n Cox supply 15V. W =1 mA/V2. Assume =0. Use power L Figure 4.31 Circuit for Example 4.9. 4.6 Small Signal Operation and Models Consider the circuit in Figure 4.34 Figure 4.34 Conceptual circuit utilized to study the operation of the MOSFET as a small-signal amplifier. The DC current ID is found by setting vgs=0. Thus 1 i D K (vGS Vt ) 2 2 Here, we have neglected the channel-length modulation (i.e. =0). The DC voltage VD is V D VDD R D I D To ensure the saturation region V D VGS Vt In addition, the total voltage at the drain will have an AC signal superimposed on VD. Thus VD has to be sufficiently greater than (VGS Vt ) to allow for the required signal swing. Next consider the situation with the input signal vgs applied. vGS VGS v gs The total current iD becomes 1 1 1 i D K (VGS v gs Vt ) 2 K (VGS Vt ) 2 K (VGS Vt )v gs K (v gs ) 2 2 2 2 The first term on the RHS can be recognized as the DC bias current ID. The second term is a current component that is directly proportional to the input signal vg. The third term is a current component that is proportional to the square of the input signal vg. Assume that vgs is kept small such that the second term is much greater that the third term. 1 K (VGS Vt )v gs K (v gs ) 2 2 resulting v gs 2(VGS Vt ) If this small-signal condition is satisfied, we can neglect the third term and iD can be expressed as i D I D id where i d K (VGS Vt )v gs and the MOSFET transconductance gm is gm iD K (VGS Vt ) v gs Substituting K for 2 I D /(VGS Vt ) 2 in g m yields 2I D VGS Vt Figure 4.35 presents a graphical interpretation of the small-signal operation g m K (VGS Vt ) The total voltage at vD is v D V D v d V DD R D ( I D i d ) Thus V D V DD RD I D v d R D i d g m v gs RD The small signal voltage gain is vd g m RD v gs A graphical illustration of the voltages is shown in Figure 4.36. Av Figure 4.35 Small-signal operation of the enhancement MOSFET amplifier. Figure 4.36 Total instantaneous voltages vGS and vD for the circuit in Fig. 4.34. 4.6.5 Small Signal Equivalent Models From the above analysis, small signal models for the FET transistor are shown in Figure 4.37. Figure 4.37 Small-signal models for the MOSFET: (a) neglecting the dependence of iD on vDS in saturation (the channel-length modulation effect); and (b) including the effect of channel-length modulation, modeled by output resistance ro = |VA| /ID. Figure 4.37b includes the effect of the channel-length modulation which is modeled by the output resistance ro. V 1 r0 A I D I D 4.6.7 The T Equivalent Model. The development of the T equivalent model is shown in Figure 4.39. Figure 4.39b adds a second current source in series (this does not change the terminal currents and is equivalent to Figure 4.39a). Then node X is joined to the gate terminal G in Figure 4.39c (this connection also does not change the terminal currents and is equivalent to Figure 4.39a). Next the controlled source between node X and S can be replaced by a resistance 1/gm as shown in Figure 4.39d. Figure 4.39d is referred to as the T model. Figure 4.40 shows various T models which include the effect of the channel-length modulation. Figure 4.39 Development of the T equivalent-circuit model for the MOSFET. For simplicity, ro has been omitted but can be added between D and S in the T model of (d). Figure 4.40 (a) The T model of the MOSFET augmented with the drain-to-source resistance ro. (b) An alternative representation of the T model. 4.6.8 Modeling the Body Effect The body effect occurs in a MOSFET when the source is not tied to the substrate. Thus the signal voltage between the body (B) and source (S) vbs gives rise to a drain current component which can be modeled as gmvbs, where the body transconductance is defined as g mb g m where 2 2 f V SB The small signal model including the body effect is shown in Figure 4.41 Figure 4.41 Small-signal equivalent-circuit model of a MOSFET in which the source is not connected to the body.