operational amplifiers part iii dynamic response

advertisement

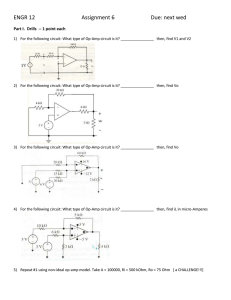

77 ELECTRICAL CIRCUITS 6. OPERATIONAL AMPLIFIERS PART III DYNAMIC RESPONSE Introduction In the first 2 handouts on op-amps the focus was on DC for the ideal and non-ideal opamp. The perfect op-amp assumptions were used to develop all the standard forms. A qualitative discussion described the how op-amps deviate from the ideal. The application of gain offset designs for transducer interfaces to data acquisition systems was explored with several design examples. Finally, we quantitatively investigated op-amp limitations for input resistance, output resistance, gain and steady state DC errors. In this handout we will investigate in detail small signal and large signal op-amp dynamic behavior. A Small Signal SPICE Model It is not our purpose in this handout to derive a detailed dynamic model of every transistor within an Integrated Circuit (IC) op-amp, but rather present an equivalent circuit model that is representative of the observed dynamic behavior. The IC op-amp contains many transistors and each transistor’s small signal model has performance over a frequency range. Figure 1 illustrates the small signal equivalent circuit model of a transistor. Figure 1 small signal frequency model of a Transistor As seen in Figure 1 the parasitic capacitors CCB and CBE of the many transistors in the IC interact with the equivalent circuit resistance and stage gains to cause a complex myriad of break frequencies that will force the circuit gain to roll off with frequency at eventually a very high order. Because of this behavior, what is done to enable stability of the dynamic response for most applications, is to deliberately add a compensation capacitor that starts the roll off very early (~10Hz) well before any of the transistor 78 frequency cutoffs start to take effect. Equation 1 gives a simple gain model in Laplace notation that fits this behavior. A( s) AO s s 1 1 5 2 10 2 10 (1) As seen in Equation 1 the DC gain is AO , the first break frequency is at 10Hz and the second break is at 105Hz. Actually, all of the parasitic break frequencies start shortly after this but, the gain has been rolled off to such an extent that all of the high order parasitic break frequencies are no longer relevant. In circuits where one must consider the input, output impedances and the frequency dependant gain we can configure the SPICE equivalent circuit model of Figure 2. Figure 2 SPICE small signal op-amp frequency model In Figure 2: R1 , is the input impedance typical value 1Meg R2 , C1 sets the 1st break frequency 10Hz R3 , C2 sets the 2nd break frequency 105Hz G , is the gain set to 100k and the inversion is in this stage R4 , is the output impedance 100 ohms Equation 3 sets the break frequencies. 1 fO 10 Hz 2 R2C1 1 f1 105 Hz 2 R3C2 (3) Formula 3 can be used to scale the model to any pair of break frequencies. Most op-amp data sheets provide data for the DC gain, the break frequencies and the input, output impedances. Additionally, many SPICE programs have a model for the op-amp (by part #) that includes all these effects. However, configuring your own as per Figure 2 you will 79 know exactly what you used rather than some “Typical Values” unknown to you. This small signal frequency model can be used for SPICE analysis to obtain transient or AC bode response of very complicated circuits. For simple circuits where input and output impedances can be neglected the control system analysis approach from the previous handout (“Operational Amplifiers Part II DC Errors”) can be used. The expression can for many cases (as shown in that handout) be written by inspection and after some clean up algebra the closed loop system function will be obtained. Consider for example the inverting amplifier finite gain expression developed in that hand-out as Equation 12 and repeated here as Equation 4. VOUT AR F VIN RIN RF AR IN (4) If we plug in Equation 1 for the gain A in Equation 4 we have the closed loop inverting op-amp response for frequency dependant gain, neglecting input and output impedances effects. VOUT VIN AO RF s 1 s 1 2 10 2 105 AO RIN RIN RF s 1 s 1 2 10 2 105 After some clean up algebra we obtain Equation 5. VOUT VIN RF 4 2106 RIN RF AR s 2 s 2 10 2 105 1 0 IN RIN RF A0 2 6 4 10 (5) Another very interesting point is what happens to the common mode gain as a function of frequency. In the last handout (“Operational Amplifiers Part II DC Errors”) we developed the common mode gain for the differential amplifier configuration (see Figure 10 of that handout). That expression was given by Equation 36 (un-simplified) and Equation 37 (simplified) both from that handout. We will consider the simplified case where we repeat Equation 37 here as Equation 6. VOUTCM Va Vb ACM RF 2 ADM RIN ACM RF VCM ADM RIN (6) 80 Now we will do the same as before, we will plug in Equation 1 for ADM in Equation 6: VOUTCM VCM VOUTCM VCM ACM RF AO RIN s 1 s 1 2 10 2 105 ACM RF s s 1 1 5 AO RIN 2 10 2 10 (7) Observe how the op-amp poles have turned into ZEROS in the common mode gain, which corrupt the common mode rejection as frequency increases. Equation 7 clearly tells us that the ability of the differential amplifier to reject common mode goes away with increasing frequency starting at the compensation pole with +20db/dec. Positive Feedback In the previous handout (“Operational Amplifiers Part II DC Errors”) Figure 3 illustrated a control system block diagram that was used to develop an analysis approach for op-amp circuits. That Figure is repeated here also as Figure 3. Figure 3 block diagram of the basic control system Observe in Figure 3 the signal VFB is input to the summer block with a plus sign. This is positive feedback. Also from that handout the system function is given by Equation 6 repeated here as Equation 8. 81 VOUT G VIN 1 GH (8) The only hint in Equation 8 about problems with the system function is if the “Loop Gain” were to become equal to 1. There would then be division by zero and the system function would blow up (saturate at the power supply limit). It would appear that if the loop gain is not equal to 1 that there would be no problems. Simple analysis on op-amp circuits would appear to confirm this. Consider the inverting amplifier with the op-amp modeled as finite gain but otherwise ideal except that we implement with positive feedback. Figure 4 illustrates the schematic and Figure 5 illustrates the equivalent circuit. Figure 4 the inverting op-amp configured with positive feed-back Figure 5 the equivalent circuit of Figure 4 This circuit can be analyzed with the control system approach. By inspection the “Straight through Gain” is given by Equation 9 and the “Loop Gain” is Equation 10: Straight Thru Gain A Loop Gain A RIN RIN RF RF RIN RF (9) (10) 82 Plugging Equations 9 and 10 into Equation 7 of the previous handout (“Operational Amplifiers Part II DC Errors”) we obtain Equation 11. VOUT ARF VIN RIN RF ARIN (11) In Equation 11 if we let the gain A get very large we obtain the ideal inverting op-amp gain: VOUT R F VIN RIN (12) These results would indicate that as long as in Equation 11 you avoid division by zero that positive feedback is not an issue. NOT TRUE! Let’s revisit the simple control system block diagram of Figure 3 and let gains G and H be given as follows: G AO , H 1 s 1 (13) O Now let’s plug Equation 13 into Equation 6 of the previous handout (“Operational Amplifiers Part II DC Errors”) and we obtain the system function: VOUT AOO VIN s O (1 AO ) (14) The inverse Laplace transform of Equation 14 is the impulse response of this circuit: h(t ) AOOet (O (1 AO ) (15) Equation 15, the impulse response, is a positive growing exponential as the gain AO is bigger than 1. Thus if such a circuit was quiescent at the “right” answer, then, the tiniest noise spike would drive it to saturate at the power supply limit. If more complicated models of the op-amp were used the results are still unstable. Thus, for op-amp circuits requiring conventional linear gains positive feedback is not used. However, there is another wide application of op-amps where positive feedback is used to obtain a toggle operation whereby the output toggles from minus saturation to plus saturation when an input signal varies relative to a reference signal. These are called comparators. There will be a future hand out that explores in depth this application. Full Power Bandwidth and Slew Rate 83 There is another IC op-amp performance specification that can restrict performance beyond all the previous limitations. The specification is called Slew Rate. Slew Rate is the maximum limit on the time derivative of the output voltage. For no distortion to occur the output voltage must comply with Equation 16: dVOUT (t ) SR, Slew Rate Spec dt (16) For example if the maximum +/-voltage at DC from the op-amp is: VO and we output a sine wave: VOUT VO sin 2 f mt (17) If we plug Equation 17 into Equation 16: VO 2 f m cos(2 f mt ) SR Now set the peak value equal to the slew rate spec: SR VO 2 Where: f m is the maximum frequency for no distortion, Hz VO is the maximum output voltage swing SR is the slew rate specificationVolts/sec fm (18) Frequency Model for Common Mode of Op-amp The previous op-amp hand-out investigated the common mode behavior of an op-amp. We now combine that effect with the inherent bandwidth of differential gain. Figure 6 illustrates a simple diagram of how common mode and differential gains combine. Figure 6 Simple model of common mode and differential gain op-amp The common mode gain is typically assumed flat at a very low gain of just 0db. For the differential gain the 2 pole model is typically used: 84 A0 s s 1 1 0 1 The Spice model that combines Figure 6 and Equation 19 is given by: ADM V V Op-amp VOUT V 0 V 1 AD M AC M AD M poles V V 2 Spice common mode model of op-amp with poles in differential gain Figure 7 Spice common mode model of op-amp with poles in differential gain Figure 8 illustrates a differential amplifier and Figure 9 illustrates the Spice model to evaluate common mode rejection. Figure 8 Differential amplifier for common mode analysis (19) 85 In the spice analysis VC M would be an AC source set to 1 volt. A Bode plot of VOUT would be the frequency response of the common mold rejection. Figure 9 gives the Spice circuit that, with appropriate values would yield a bode plot of the common mode rejection. Figure 9 Spice common mode model of differential amplifier Phase Gain Margin for Stability Analysis Even though an op-amp circuit doesn't have positive feedback it could still get in trouble with instability oscillations. Consider the standard simple feedback block diagram. Figure 10 standard simple feedback block diagram As seen before the Closed Loop Gain (GLG) is given by: CLG G 1 GH (20) 86 The negative in the denominator is inherent to the feedback analysis and the inclusion of a negative sign in either G or H, but not both then Equation 20 becomes: CLG G G 1 GH 1 GH (21) This is the desired result from negative feedback. This will be true as long as the 2 negative signs are present. The first negative is always present as it is from the feedback process. However, the second negative is dependant upon the frequency response of GH the loop gain. For many applications the sign of GH at low frequency will start negative and at higher frequency will phase shift to zero to yield positive feedback. For a good design when the phase shift of GH does hit positive, the magnitude of GH is significantly less than unity. One analysis tool used to assess this condition is Bode plots of GH. The criteria for good stability is: 1. When GH falls to unity, the phase of GH , GH , still has not reached positive feedback. How much is left is "Phase Margin" (PM) 2. When the phase GH , does reach positive feedback, the GH 1 and how much less is the "Gain Margine"(GM). 3. Typical design guidelines are for GM GH 0.1 and PM at least 30o left before positive feedback. GH 0o PM f GH f 0db GM Figure 11 PM and GM on an illustration of a Bode plot of GH.