Electrical and dielectric properties and intersection behavior of G/ω

advertisement

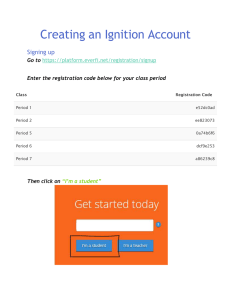

Journal of the Korean Physical Society, Vol. 65, No. 12, December 2014, pp. 2082∼2089 Electrical and Dielectric Properties and Intersection Behavior of G/ω-V Plots for Al/Co-PVA/p-Si (MPS) Structures at Temperatures below Room Temperature İbrahim Yücedağ Department of Computer Engineering, Technology Faculty, Duzce University, Duzce, Turkey Ahmet Kaya∗ Department of Opticianry,Vocational School of Medical Sciences, Turgut Ozal University, Ankara, Turkey Şemsettin Altındal Department of Physics, Faculty of Science and Arts, Gazi University, Ankara, Turkey İbrahim Uslu Department of Chemistry, Faculty of Science and Arts, Gazi University, Ankara, Turkey (Received 13 June 2014, in final form 17 September 2014) Both the electrical and the dielectric properties of the Al/Co-doped polyvinyl alcohol/p-Si metal-polymer-semiconductor (MPS) structure have been studied using temperature-dependent admittance-voltage (C/G-V ) measurements at temperatures below room temperature at 300 kHz. The C-V plot indicates two peaks for each temperature corresponding to inversion and accumulation regions, respectively. The first peak was attributed to a particular distribution of interface traps (Dit ), and the second was attributed to the series resistance (Rs ) and interfacial polymer layer. G/ω-V plots show almost U-shape behavior for all temperatures and a crossing at almost 3 V. Such behavior of the G/ω-V plots may be attributed to the lack of free charge at low temperatures. After this intersection point, while the value of the capacitance (C ) starts decreasing, the G/ω continues to increase. The temperature-dependent real and imaginary parts of the dielectric constant (ε , ε ) and of the electric modulus (M , M ), as well as the ac electrical conductivity (σac ), of structure were obtained using C and G data before and after the intersection point (at 2 and 6 V), respectively. Experimental results show that the ε , ε , loss tangent (tanδ), σac , M , and M values were strong functions of the temperature and the applied bias voltage. In addition, G/ω-T and ε -T plots show two different behaviors, one before and the other after the intersection point. PACS numbers: 77.84.Jd, 77.22.Ch, 77.22.Gm Keywords: Metal-polymer-semiconductor (MPS) structures, Temperature dependence of electric and dielectric properties, Intersection behavior in G/ω-V-T plots DOI: 10.3938/jkps.65.2082 I. INTRODUCTION In the last two decades, polymeric materials have attracted much attention in both academic and industrial research fields because of their extensive applications. This is primarily on account of their light weight, good mechanical strength, and optical properties, which make them multifunctional materials [1–3]. The behaviors of the electrical characteristics of metal-polymersemiconductor (MPS) structures are similar to those ∗ E-mail: of metal/insulator/semiconductor (MIS) structures, and many in the field think that they will shape the next generation of cheap and disposable electronic inventions [4–7]. The electrical and the dielectric properties of the metal-semiconductor (MS) structure can be modified by using metal-doped (Co, Ni, Zn) polymer materials. Pure polymers are well known to have poor electrical conductivities, but their conductivities can be improved by blending and doping them with some metals that can induce modifications in the molecular structure and, hence, in the micro-structural properties of the polymer. Among the various conducting polymers, poly-vinyl al- ahmetkaya0107@hotmail.com -2082- Electrical and Dielectric Properties and Intersection Behavior · · · – İbrahim Yücedağ et al. cohol (PVA), polyaniline, poly (alkylthiophene) polypyrrole, polyophene and poly (3-hexylthiophene) have become attractive research topics for chemists, physicists and electrical engineers due to their potential applications and interesting properties [8–11]. The performance and the quality of MS, MIS, and MPS structures depend on various parameters, such as the interfacial layer’s thickness and its homogeneity, the shape and height of the barrier, the density distribution of interface traps (Dit ) at the M/S interface, the series resistance (Rs ) of the device, the concentration of acceptor or donor atoms, and the samples temperature. Traditionally, SiO2 is used an interfacial layer at the M/S interface in these devices, but it cannot completely passivate the active dangling bonds at the semiconductor’s surface. Therefore, in recent years, metal-doped polymer materials have been examined as potential materials for replacing SiO2 in these devices [12–15]. PVA, as one of the most important polymers, recently received considerable attention due to its numerous potential applications in electronic devices. The electrical and the dielectric characteristics of the MS, MIS, and MPS with an interfacial insulator or polymeric layer are generally determined by the quality of the interface, the distribution of interface states (Nss ) at the PVA/Si interface, the homogeneity of the interfacial layer (PVA), the barrier homogeneity at the M/S interface, the substrate temperature and the Rs of the structures. The investigation of the electric and the dielectric properties is one of the most convenient and sensitive methods for studying polymer-based devices. Especially, PVA nanofabrics have attracted much attention for decades because of their unmatched chemical and physical properties and their industrial applications [16–18]. Such interfacial layers not only can prevent reactions and inter-diffusion between the metal and the semiconductor substrate but also can improve the electric-field reduction issue in these structures. Because a dc bias voltage is applied across these devices, the interfacial layer, the depletion layer and the Rs of the device will share the applied voltage [19–27]. In addition, the C-V and the G/ω-V characteristics depend considerably on the temperature, especially at low temperatures. When these measurements are carried out only at room temperature, they cannot provide sufficient information on the electrical and the dielectric properties. On the other hand, when they are carried out over a wide temperature range, especially at temperatures below room temperature, they provide more information about the conduction mechanism in these devices. In this work, a PVA film was used as an interfacial layer between the metal and the semiconductor, and the electrical and the dielectric properties of Al/Co-doped PVA/p-Si (MPS) structures were studied by C-V and G/ω-V measurements at temperatures below room temperatures and at voltage between −5 V and 6 V in 50 mV steps by using an HP-4192A impedance analyzer at 300 kHz. The variations in the real (ε ) and imaginary (ε ) -2083- Fig. 1. (Color online) Measured capacitance C(V, T) for the Al/Co-doped PVA/p-Si (MPS) structure at 300 kHz. parts of the dielectric constant, the loss tangent (tanδ, the real (M ) and the imaginary (M ) parts of the electric modulus, and the ac conductivity (σac ) with temperature and voltage were investigated. II. EXPERIMENTAL PROCEDURE The Al/PVA (Co-doped)/p-Si structures were fabricated on the 2-inch (5.08-cm)-diameter B-doped Si wafers having a thickness of 350 μm and a resistivity of approximately 0.04 Ωcm. The structure of Al/PVA (Codoped)/p-Si structure and the details of its fabrication have been given in our previous study [7]. The capacitance-voltage (C-V ) and the conductancevoltage (G/ω-V ) measurements of the Al/PVA (Codoped)/p-Si structures were performed in the temperature range of 80 − 300 K at 300 kHz by using an HP 4192A LF impedance analyzer (5 Hz − 13 MHz) and a test signal of 50 mVrms . All measurements were carried out in a Janes vpf-475 cryostat, which enabled us to make measurements in the temperature range of 77 − 450 K. The samples, temperatures were controlled by using a Lake Shore model 321 auto-tuning temperature controller with a sensitivity better than ±0.1 K. In addition, all measurements were carried out with the help of a microcomputer with an IEEE-488 ac/dc converter card. III. RESULTS AND DISCUSSION 1. Electrical Measurements The temperature-dependent capacitance-voltage (CV ) and conductance-voltage (G/ω-V ) characteristics of the Al/Co-PVA/p-Si structure were measured in the -2084- Journal of the Korean Physical Society, Vol. 65, No. 12, December 2014 Fig. 4. Measured G/ω-T for the Al/Co-doped PVA/p-Si (MPS) structure at 300 kHz for 2 V and 6 V. Fig. 2. (Color online) Measured conductance G/ω(V, T) for the Al/Co-doped PVA/p-Si (MPS) structure at 300 kHz. Fig. 3. (Color online) Voltage-dependent capacitance (C) and conductance (G/ω) at 300 kHz for the MPS structure at 80 K and 300 K. temperature range of 80 − 300 K at 300 kHz, and the applied bias voltage range was −5 to +6 V in 50-mV steps. These results obtained are given in Figs. (1) and (2), respectively. As shown in Fig. 1, the values the C increase with increasing bias voltage and have two peaks, one in the inversion region and the other in the accumulation region. The first peak stems from the charges localized at interface traps (Dit ) at the M/S interface, but the second peak stems from both the interfacial Co-doped PVA layer and the Rs of structure [7,19–22]. As shown in Figs. (1) and (2), both the C and the G/ω values increase with increasing temperature in the forward bias region, but clearly their behaviors are different, especially in the inversion and the accumulation regions. The G/ω-V plots exhibit a nearly U-shape behavior for each temperature, and such a behavior can be attributed to the increased number of charges under an applied bias voltage and depends on the relaxation time of the charges at interface traps. In order to show these contrasts, we have plotted the C-V and the G/ω-V plots for 300 kHz at 80 and 300 K together in Fig. 3. As can be seen in Fig. 3, both in the inversion and the accumulation regions, the minimum C value corresponds to the maximum conductance value. When the temperature is increased, the generation of thermal carriers (electrons or holes) in the semiconductor is enhanced for both positive and negative bias conditions. Thus, the change in the C values increasing the temperature, especially in the depletion and the accumulation regions, can be understood through charge storage (C = Q/V ). These behaviors of the C-V and the G/ω-V plots show that the material displays an inductive behavior [19,28]. In addition, the injection of charge carriers is believed to involve a process of hopping to localized interface traps/states, but the detailed physical mechanisms of injection are still not fully understood. In addition, while the G/ω-V plots cross at a nearly common forward bias voltage (∼3 V), the C-V plots give a peak and then become decreasing. This intersecting behavior of the G/ω-V plots can be attributed to the insufficient free charge at low temperatures. After this intersection point, while the value of C starts decreasing, the G/ω continues to increase. In order to see these opposing behaviors, we have plotted the temperature-dependent G/ω values both before and after the intersection point for 2 V and 6 V, respectively, in Fig. 4. As shown in this figure, the G/ω values while increasing for 2 V decreasing for 6 V. Such abnormal behavior of the C-V and the G/w plots with temperature can be explained by the existence of localized Nss at M/S interface and the Rs result in a charge at traps/surface states due to temperature and applied-bias-voltage effects [19]. On the other hand, Schottky barrier diodes (SBDs) comprise a semiconductor between the rectifier and the ohmic contacts, but with Nss and bulk traps, where the charges can be stored and released; when the appropriate forward applied bias voltage and external oscillation voltage are applied, a large effect can be produced in the structure [20]. Although, the injection of charge carriers is believed to involve a process of hopping to localized Nss , the detailed physical mechanism of injection is not well understood yet. Both the voltage and the temperature dependences of Electrical and Dielectric Properties and Intersection Behavior · · · – İbrahim Yücedağ et al. Fig. 5. Variation of the series resistance with forward bias voltage for the Al/Co-doped PVA/p-Si (MPS) structure at temperatures below room temperature. the resistance of the MPS structure (Ri ) can be obtained from the experimental C and G/ω data by using [23] Ri = Gmi , G2mi + (ωCmi )2 (1) where ω is the angular frequency, and Cmi and Gmi are the capacitance and the conductance values for any voltage. Figure 5 shows Ri -V plots for various temperatures. The fact that the value of Ri is significant means that special attention has to be paid to the effect of Ri in the application of capacitance-conductance-based measurements. In Fig. 5, clearly, the plots have a peak (∼0 V) for each temperature due to the particular density distribution of Dit . The Ri values in the strong accumulation region correspond to the real value of Rs for the MPS structure. As can be seen in Fig. 4, before the intersection point (at 2 V), the value of Gi /ω increase with increasing temperature, in accordance with the literature, but it decreases after the intersection point (at 6 V). Such a behavior of Gi after the intersection point is in obvious disagreement with the reported negative temperature coefficient of resistance (R = 1/G) or the positive temperature coefficient of conductance (G) because increases in temperature lead to a decrease of the forbidden band gap of the semiconductor [21,23]. Thus, many more electrons are expected to be stimulated to the conductance band and, thus, lead to an increase in the conductance or a decrease in the resistance [21,23]. Such a variation of Gi /ω with temperature (after the intersection point) is expected for semiconductors in the temperature region where there is no freezing behavior of the carriers. We believe that the trapped charges have enough energy to escape from traps located at the M/S interface in the Si band gap. In Fig. 6, the C−2 -V plots are presented for low temperatures. As can be seen in the figure, the C−2 -V plots at 300 kHz give a straight line in the inversion region. The diffusion potential is obtained by extrapolating these -2085- Fig. 6. C−2 -V characteristic for the Al/PVA (Codoped)/p-Si (MPS) structure at low temperatures. straight lines to the voltage axis, and the values are given in Table 1. The linear behavior of the C−2 -V curves can be entirely explained on the basis of the assumption that the interface states and the inversion layer charges cannot follow the ac signal, especially in the strong accumulation regions; consequently they do not contribute appreciably to the capacitance of the Al/Co-PVA/p-Si (MPS) structure. The depletion layer capacitance can be expressed as follow [24–27]: C −2 = 2(VR + V0 ) , qεs ND A2 (2) where V0 and NA are the intercept voltage and the doping concentration of acceptor atoms, respectively. The values of V0 were determined from extrapolations of the linear parts of the C−2 vs. V (Fig. 6) plots to the bias axis. Thus, the values of the Fermi energy level (EF ) and the NA were calculated as follow: V0 = VD − kT , q (3) where VD is the diffusion potential at zero bias and EF is the Fermi energy level and was obtained from NV kT Ln EF = , (4a) q NA with (4b) NV = 4.82 × 1015 T 3/2 (m∗h /m0 )3/2 where NV is the effective density of states in the Si valence band, mh ∗ = 0.16 mo is the effective mass of holes [28,29] and mo is the rest mass of the electron. Thus, the barrier height ΦB (C-V) was calculated at each temperature by using the relation kT = EF . (4c) ΦB (C − V ) = V0 + Q -2086- Journal of the Korean Physical Society, Vol. 65, No. 12, December 2014 Table 1. Values of the doping concentration of acceptor atoms (NA ), the Fermi energy (EF ), the diffusion potential (VD ), the barrier height (ΦB (C-V)), and the series resistance (Rs ) for the Al/PVA (Co-doped)/p-Si (MPS) structure determined from the C −2 -V characteristics at 300 kHz and low temperatures. T (K) 80 120 160 200 NA × 1015 (cm−3 ) 2.62 3.06 3.81 4.84 EF (eV) 0.065 0.061 0.055 0.049 VD (eV) 0.933 0.925 0.915 0.912 ΦB (C-V) (eV) 0.998 0.986 0.970 0.961 Rs (at 6 V) (Ω) 7.33 7.18 6.98 6.95 The values of NA , EF , VD , and ΦB (C-V) determined from the reverse bias C −2 vs. V plots at low temperatures are given in Table 1. As shown in Table 1, while the values of EF , VD , Rs , and ΦB (C-V) decrease with increasing temperature, only the value of NA decreases. The value of ΦB (C-V) a function of temperature is given by ΦB (C −V ) = ΦB (0K)+αT = 1.023−3.78×10−4 T, (5) where α is the temperature coefficient of the barrier height (BH) and ΦB (0 K) is the value of the BH at zero temperature. Clearly, the obtained negative value of the temperature coefficient (−3.78 × 10−4 eV/K) for the BH is very close to the negative value of the temperature coefficient for the energy band-gap of Si (−4.73 × 10−4 eV/K). 2. Dielectric Measurements The temperature-dependent ε , ε , tan δ, σac , M , and M were evaluated from the C and the G/ω data for the MPS structure in the temperature range of 80 − 280 K at 300 kHz. By using the measured values of C and G/ω at 2 and 6 V, we determined the ε , ε , tanδ and σac values of the MPS structure by using the following expressions [30,31]: C d C= , ε0 A C0 G d G= , ε = ε0 Aω ωC0 ε tan δ = , ε σac = ωC tan δ(d/A) = ε ωε0 , ε = (6) (7) Fig. 7. Temperature dependences of the (a) ε , (b) ε , and (c) tanδ for the Al/PVA (Co-doped)/p-Si (MPS) structure at 300 kHz for 2V and 6V. F/m). Many authors prefer to describe the dielectric properties of these devices by using the electric-modulus formalizm. The complex impedance or the complex permittivity (ε∗ = 1/M ∗ ) data can be transformed into the M ∗ formalism by using the following relation [30,32]: (8) (9) where Co is the capacitance of an empty capacitor (Co = ε0 (A/d)), A is the rectifier’s contact area in cm−2 , d is the interfacial polymer layer’s thickness and εo is the permittivity of free-space charge (εo = 8.85 × 10−12 M∗ = ε ε 1 = M + jM = 2 + j 2 . (10) ∗ 2 ε ε +ε ε + ε2 The real and the imaginary components of the electric modulus (M and the M ”) were also calculated using the ε and the ε values for each temperature. The temperature dependences of the ε , ε and tanδ values of Electrical and Dielectric Properties and Intersection Behavior · · · – İbrahim Yücedağ et al. Fig. 8. Temperatures dependences of the ac conductivity (σac ) for the Al/PVA (Co-doped)/p-Si (MPS) structure at 300 kHz for 2 V and 6 V. perature before and after the intersection points at 300 kHz by using Eq. 9 and are presented in Fig. 8. Clearly, the conductivity increases with increasing temperature before the intersection point, but decreases after the intersection point. The suggests that the process of dielectric polarization in the MPS structure takes place through a mechanism similar to the conduction process [35–40]. The increase in the σac with increasing temperature can be attributed to the impurities or dislocations that reside at the grain boundaries [40]. These impurities, which are called interface traps or surface states, lie above the top of the valence band; thus, they have a small activation energy. Therefore, these traps/states are called acceptor-type surface states in p-type semiconductors. This means that the contribution to the conduction mechanism comes from the grain boundaries at low temperatures while it mainly results from the grains at higher temperature. In addition, as can be seen in Fig. 9, there is almost a linear relation between the conductivity and the inverse absolute temperature [39–42]; σ = σ0 exp(−Ea /kT ), Fig. 9. Arrhenius plots of the ac electrical conductivity for the Al/PVA (Co-doped)/p-Si (MPS) structure at 300 kHz for 2 V and 6 V. the MPS structure are presented in Figs. 7(a), (b), and (c), respectively. As can be seen in these figures, the values of the ε , ε and tan are strong functions of the temperature and the applied bias voltage. As can be seen from Figs. 7(a) and (c), while the value of ε increases, tan decreases with increasing temperature. On the other hand, ε -T plots show two different behaviors, one before and one after the intersection point, as in the G/ω-T plots (Fig. 4). These results confirm that the changes in the electrical and the dielectric parameters become more important at low temperatures due to the lack of free charges. As the temperature rises, imperfections/disorders are created in the lattice, and the mobility of the majority charge carriers (ions and electrons) increases. The combined effect gives an increase in the value of ε with the increasing temperature. This may possibly be due to the ion jump, the orientation, and the space charge effect resulting from the increased concentrations of charge carriers. In the other word, the increased concentrations of charge carriers lead to an increase in the ε of the dielectric material [30,32–34]. The values of σac ac were calculated for each tem- -2087- (11) Using the Arrhenius plots (Fig. 9) for the MPS structure for 2 and 6 V at 300 kHz, and an exponential fit to the data, we found the activation energy (Ea ) to be 7 meV (at 6 V) and −16.3 meV (at 2 V). Such small activation energies show that the bulk trap levels lie above the intrinsic Fermi level and close to the valence band edge. Figures 10(a) and (b) depict the real (M ) and the imaginary (M ) parts of the complex electric modulus (M ∗ ) versus temperature for the samples at two voltages, one before and the other after the intersection point (2 V and 6 V), at 300 kHz. Clearly, the value of M increases with increasing temperature, especially at 6 V. On the other hand, the value of M decreases with increasing temperature [42]. All of these obtained results confirm that the changes in the electric and the dielectric parameters are very large. In the other word, at low temperatures, the conduction mechanism is very different from that at high temperatures. Therefore, in our opinion, this study is valuable became it was carried out at lower temperatures below room temperature. IV. CONCLUSION The electrical and the dielectric properties of the Al/Co-PVA/p-Si (MPS) structure have been investigated by using data on the temperature and the voltage dependences of C and G in the temperature range of 80 − 300 K at 300 kHz. The experimental results indicated that both the electrical and the dielectric properties of the MPS structure were quite sensitive to the temperature and the applied bias voltage. While the G/ω-V -2088- Journal of the Korean Physical Society, Vol. 65, No. 12, December 2014 from their ideal values. ACKNOWLEDGMENTS This work is supported by Duzce University BAP research project number 2013.07.02.204. REFERENCES Fig. 10. Real (M ) and imaginary (M ) parts of the complex electric modulus (M ∗ ) vs. temperature for the Al/PVA (Co-doped)/p-Si (MPS) structure at 300 kHz for 2 V and 6 V. plots cross at a nearly common forward bias voltage (∼3 V), the C-V plots show a peak and then decrease. This intersection behavior of the G/ω-V plots was attributed to the lack of free charge at low temperatures. The C-V plot has two distinct peaks for each temperature corresponding to the inversion and the accumulation regions, respectively. While the density distribution of interface traps (Dit ) is the cause of the first peak, the Rs value and the interfacial polymer layer cause the second peak. Contrary to the C-V plots, the G/ω-V plots exhibit an almost U-shape behavior, and they cross at about 3 V. After this intersection point, while the value of C starts to decrease, G/ω continuously increases. The ε , ε , M , M , and σac values of the MPS structure were obtained by using C and G data before and after the intersection point (at 2 V and 6 V), respectively. Clearly, the G/ωV, σac -T and ε -T plots show two different behaviors, one before and one after the intersection point. In conclusion, the changes in the electrical and the dielectric parameters become more important at low temperatures due to the lack of free charges. In addition, the existence of an interfacial polymer or insulator layer can cause deviations in the electrical and the dielectric characteristics [1] L. Beecroft and C. K. Ober, Chem. Mater. 9, 1302 (1997). [2] R. V. Kumar, R. Elgamiel, Y. Diamant and A. Gedanken, Langmuir 17, 1406 (2001). [3] A. Anis and A. K. Banthia, Mater. Manufact. Proces. 22, 737 (2007). [4] M. E. Aydin and F. Yakuphanoglu, Microelectron. Eng. 85, 1836 (2008). [5] R. Şahingöz, H. Kanbur, M. Voigt and C. Soykan, Synth. Met. 158, 727 (2008). [6] A. A. M. Farag, E. A. A. El-Shazly, M. Abdel Rafea and A. Ibrahim, Sol. Ener. Mat. Solar Cells 93, 1853 (2009). [7] İ. Yücedağ, A. Kaya, Ş. Altındal and I. Uslu, Chin. Phys. B 23, 047304 (2014). [8] P. Syed Abthagir and R. Saraswathi, Organ. Electron. 5, 299 (2004). [9] Y. O. Yakovlev and V. F. Zolin, Synth. Met. 91, 205 (1997). [10] F. Garten, J. Vrijmoeth, A. R. Schlatmann, R. E. Gill, T. M. Klapwijk and G.Hadziioannou, Synth. Met. 76, 85 (1996). [11] A. Bohler, S. Dirr, H. H. Johannes, D. Ammermann and W. Kowalsky, Synth. Met. 91, 95 (1997). [12] N. B. Ukah, D. Adil, J. Granstrom, R. K. Gupta, K. Ghosh and S. Guha, Org. Electron. 12, 1580 (2011). [13] S. Guha, D. Adil, N. B. Ukah, R. K. Gupta and K. Ghosh, Appl. Phys. A 105, 547 (2011). [14] X. Huang, C. Zhi, P. Jiang, D. Golberg, Y. Bando and T. Tanaka, Nanotechnology 23, 455705 (2012). [15] T. A. Hanafy, J. App. Poly. Sci. 108, 2540 (2008). [16] H. Guan, C. Shao, S. Wen, B. Chen, J. Gong and X. Yang, Mater. Chem. Phys. 82, 1002 (2003). [17] J. S. Lee, K. H. Choi, H. D. Ghim, S. S. Kim, D. H. Chun, H. Y. Kim and W. S. Lyoo, J. Appl. Poly. Sci. 93, 1638 (2004). [18] I. Uslu, B. Başer, A. Yaylı and M. L. Aksu, e-Polymers 145, 1699 (2007). [19] E. Arslan, Y. Şafak, Ş. Altındal, Ö. Kelekçi and E. Özbay, J. Non-crystalline Solids 356, 1006 (2010). [20] P. Cattopadyay, Solid State Electron. 37, 1759 (1994). [21] E. H. Rhoderick and R. H. Williams, MetalSemiconductor Contacts, 2nd ed. (Clarendon, Oxford, 1978). [22] P. Chattopadhyay and B. Raychaudhuri, Solid State Electron. 35, 1023 (1992). [23] E. H. Nicollian and J. R. Brews, MOS (Metal-OxideSemiconductor) Physics and Technology (Bell Laboratories Murray Hill, New Jersey, 1982). [24] H. C. Card and E. H. Rhodercik, J. Phys. D 4, 1589 (1971). Electrical and Dielectric Properties and Intersection Behavior · · · – İbrahim Yücedağ et al. [25] M. K. Hudait and S. B. Krupanidhi, Solid-State Electron. 44, 1089 (2000). [26] P. Cahttopadhyay and A. N. Daw, Solid-State Electron. 29, 555 (1986). [27] İ. Yücedağ, Optoelectron. and Adv. Mater. Rapid Comm. 3, 612 (2009). [28] P. L. Hanselaer, W. H. Laflére, R. L. Van Meirhaeghe and F.Cardon, J. Appl. Phys. 56, 2309 (1984). [29] Ş. Altındal, S. Karadeniz, N. Tuğluoğlu and A. Tataroğlu, Solid-State Electron. 47, 1847 (2003). [30] P. B. Macedo, C. T. Moyniham and R. Bose, Phys. Chem. Glass. 13, 171 (1972). [31] Y.-S. Jin, G.-J. Kim and S.-G. Jeon, J. Korean Phys. Soc. 49, 513 (2006). [32] P. Pissis and A. Kyritsis, Solid State Ionics 97, 105 (1997). [33] V. Singh, A. R. Kulkarni and T. R. Rama Mohan, J. Appl. Polym. Sci. 90, 3602 (2003). [34] D. Maurya, J. Kumar and D. Shripal, J. Phys. Chem. -2089- Solids 66, 161 (2005). [35] A. Eroğlu, A. Tataroğlu and Ş. Altındal, Microelectro. Eng. 91, 154 (2012). [36] T. Tunc, I. Uslu, I. B. Dökme, Ş. Altındal and H. Uslu, Int. J. Polym. Mat. 59, 739 (2010). [37] P. P. Sahay, R. K. Mishra S. N. Pandey, S. Jha and M. Shamsuddin, Cur. Appl. Phys. 13, 479 (2013). [38] K. Majhi, R. Vaish, G. Paramesh and K. B. R. Varma, Ionics 19, 99 (2013). [39] A. Tataroğlu, İ. Yücedağ and Ş. Altındal, Microelectro. Eng. 85, 1518 (2008). [40] M. S. Mattsson, G. A. Niklasson, K. Forsgren and A. Harsta, J. Appl. Phys. 85, 2185 (1999). [41] A. S. Md, S. Rahman, M. H. Islam and C. A. Hogarth, Int. J. Electron. 62, 167 (1987). [42] İ. B. Dökme and Ş. Altındal, IEEE Trans. Electron. Dev. 58, 4042 (2011).