120 Review Packet All photos and tables from Wikipedia unless

advertisement

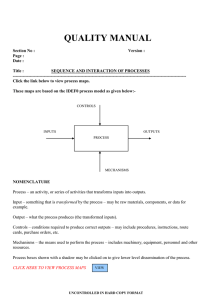

120 Review Packet All photos and tables from Wikipedia unless otherwise noted: https://en.wikipedia.org/wiki/Logic_gate 2 Input Gates, Truth Tables, and Boolean Expressions AND OR NOT NAND NOR XOR XNOR A 0 0 1 1 B 0 1 0 1 A AND B 0 0 0 1 A 0 0 1 1 B 0 1 0 1 A OR B 0 1 1 1 A 0 1 NOT A 1 0 A 0 0 1 1 B 0 1 0 1 A NAND B 1 1 1 0 A 0 0 1 1 B 0 1 0 1 A NOR B 1 0 0 0 A 0 0 1 1 B 0 1 0 1 A XOR B 0 1 1 0 A 0 0 1 1 B 0 1 0 1 A XNOR B 1 0 0 1 𝐴∙𝐵 𝐴+𝐵 𝐴̅ ̅̅̅̅̅̅̅̅̅ (𝐴 ∙ 𝐵) 𝐴̅ + 𝐵̅ ̅̅̅̅̅̅̅̅̅̅ (𝐴 + 𝐵) 𝐴 ∙ 𝐵̅ + 𝐴̅ ∙ 𝐵 (𝐴 + 𝐵) ∙ (𝐴̅ + 𝐵̅) 𝐴 ∙ 𝐵 + 𝐴̅ ∙ 𝐵̅ NAND/NOR Equivalencies GATE NAND EQUIVALENT NOR EQUIVALENT AND OR NOT NAND NOR XOR XNOR n/a n/a Boolean Algebra Identities 𝑎+0=𝑎 𝑎+1=1 𝑎 + 𝑎̅ = 1 𝑎+𝑎 =𝑎 𝑎∙1=𝑎 𝑎∙0=0 𝑎 ∙ 𝑎̅ = 0 𝑎∙𝑎 =𝑎 ̅̅̅̅ (𝑎̅) = 𝑎 𝑎(𝑏 + 𝑐) = 𝑎𝑏 + 𝑎𝑐 𝑎 + 𝑏𝑐 = (𝑎 + 𝑏)(𝑎 + 𝑐) 𝑎𝑏 + 𝑎𝑏̅ = 𝑎 (𝑎 + 𝑏)(𝑎 + 𝑏̅) = 𝑎 𝑎 + 𝑎̅𝑏 = 𝑎 + 𝑏 Absorption and Consensus 𝑎 + 𝑎𝑏 = 𝑎 𝑎(𝑎 + 𝑏) = 𝑎 𝑎𝑏 + 𝑎̅𝑐 = (𝑎 + 𝑐)(𝑎̅ + 𝑏) DeMorgan’s Law ̅̅̅̅̅̅̅̅̅̅ (𝑎 + 𝑏) = 𝑎̅ ∙ 𝑏̅ ̅̅̅ = 𝑎̅ + 𝑏̅ 𝑎𝑏 ̅̅̅̅̅̅̅̅̅̅̅̅ 𝑎 + 𝑏 + 𝑐 = 𝑎̅ ∙ 𝑏̅ ∙ 𝑐̅ Karnaugh Mapping 2-Bit K-Map A\B 0 1 0 0 1 1 2 3 3-Bit K-Map AB\C 00 01 11 10 0 0 2 6 4 1 1 3 7 5 4-Bit K-Map AB\CD 00 01 11 10 00 0 4 12 8 01 1 5 13 9 11 3 7 15 11 10 2 6 14 10 K-Map Rules 1) Circle only 1s (ones) and don’t cares for SOP. a. Circle only 0s (zeros) and don’t cares for POS. b. Don’t cares may be used or ignored. 2) No diagonals, only horizontal or vertical connections. 3) Only: 1, 2, or 4 numbers per grouping. 4) Groups as large as possible. 5) Must group all 1s (ones) for SOP. a. Must group all 0s (zeros) for POS. b. Any number of don’t cares may be used or ignored. 6) Overlapping allowed. 7) Wrapping around all edges allowed. 8) Fewest groups possible. SOP expression: Sum of Minterms (one values in truth table and K-map) w/ Don’t Cares ∑ 𝑚(𝐴, 𝐵, 𝐶, 𝐷) + ∑ 𝑑(𝐸, 𝐹, 𝐺) 𝐴𝐵̅𝐶̅ + 𝐴̅𝐵𝐶 + 𝐵𝐶 + 𝐴̅𝐶 POS expression: Product of Maxterms (zero values in truth table and K-map) w/ Don’t Cares ∏ 𝑀(𝐴, 𝐵, 𝐶, 𝐷) + ∑ 𝑑(𝐸, 𝐹, 𝐺) (𝐴 + 𝐵̅ + 𝐶̅ )(𝐴̅ + 𝐵)(𝐶̅ + 𝐴) Programmable Logic Arrays PAL (P”AND”L): selectable AND plane, fixed OR plane One OR gate outputs a single function with predetermined number of input terms SOP expressions limited to a fixed number of terms (connections available per OR gate) May select any number of literals per term in SOP expression ROM (R”OR”M): fixed AND plane, selectable OR plane All possible terms from truth table preselected in AND plane One OR gate outputs a single function in SOP format May select any number of terms to output in SOP expression PLA: selectable AND plane, selectable OR plane No limit on terms or literals in each function Latches SR Latch 𝑆 0 0 1 1 𝑅 0 1 0 1 𝑄 Store 0 1 Invalid 𝑄̅ Store 1 0 Invalid NOR Latch 𝑆 0 0 1 1 𝑅 0 1 0 1 𝑄∗ Store, Q Reset, 0 Set, 1 Invalid NAND Latch 𝑆̅ 0 0 1 1 𝑅̅ 0 1 0 1 𝑄∗ Invalid Set, 1 Reset, 0 Store NOR setup: look at inputs of 1 first to determine outputs (all 1 force output of 0) NAND setup: look at inputs of 0 first to determine outputs (all 0s force output of 1) D Latch with Enable 𝐸𝑛𝑎𝑏𝑙𝑒 0 0 1 1 𝐷 0 1 0 1 𝑄 Store Store 0 1 𝑄̅ Store Store 1 0 Characteristic Table 𝐸𝑁 0 1 1 𝐷 X 0 1 𝑄∗ Store, Q Reset, 0 Set, 1 All Latches are Level Triggered o Will change any time enable is active (asynchronous changes possible while active) Flip-Flops SR Flip Flop Can contain/store an invalid state Characteristic 𝑆 0 0 1 1 𝑅 0 1 0 1 𝑄∗ Q 0 1 Invalid Excitation 𝑄 0 0 1 1 𝑄∗ 0 1 0 1 𝑆 0 1 0 X R X 0 1 0 D Flip Flop Mirrors D input at the clock edge time Characteristic Leading Edge Clock Trigger _/¯ _/¯ Any Other Time Excitation Trailing Edge Clock Trigger ¯\_ ¯\_ Any Other Time 𝐷 𝑄∗ 𝑄 𝑄∗ 𝐷 0 1 X 0 1 Store 0 0 1 1 0 1 0 1 0 1 0 1 JK Flip Flop Often used in master/slave pairs to avoid timing problems and create level triggering Characteristic 𝐽 0 0 1 1 𝐾 0 1 0 1 𝑄∗ Store, Q Reset, 0 Set, 1 Toggle 𝑄̅ Excitation 𝑄 0 0 1 1 𝑄∗ 0 1 0 1 𝐽 0 1 X X 𝐾 X X 1 0 T Flip Flop Toggles: 𝑄 = 𝑄̅ whenever 𝑇 = 1 Characteristic 𝑇 0 0 1 1 𝑄 0 1 0 1 Excitation 𝑄∗ 0 1 1 0 𝑄 0 0 1 1 𝑄∗ 0 1 0 1 𝑇 0 1 1 0 Interpreting Timing Diagrams 1) Note type of register and triggering time a. Level or edge triggered (latch or flip/flop) b. Leading or trailing edge c. SR, D, T, or JK 2) Using proper excitation tables for flip/flop or latch, walk through circuit with given input a. Flip Flops will only change from an input signal on the proper clock edge b. Latches will change whenever the clock is active. 3) Clear will asynchronously set a value to 0 (low). a. CLR or CLR/~ denotes an active high clear, the output will be 0 while clear is 1. b. CLR’ or /~CLR or ̅̅̅̅̅̅ 𝐶𝐿𝑅 or a negate symbol at the CLR flip/flop connection denotes an active low clear, the output will be 0 while clear is 0. 4) Preset will asynchronously set a value to 1 (high). a. PRE or PRE/~ denotes an active high preset, the output will be 1 while preset is 1. ̅̅̅̅̅̅ or a negate symbol at the PRE flip/flop connection denotes an b. PRE’ or /~PRE or 𝑃𝑅𝐸 active low preset, the output will be 1 while preset is 0. Positive Edge Triggered, active low PRE and CLR D flip/flop Characteristic Table PRE’ 1 1 0 1 0 CLR’ 1 1 1 0 0 CLK ↑ ↑ X X X IN, D 0 1 X X X 𝑄 0 1 1 0 Invalid, 1 𝑄̅ 1 0 0 1 Invalid, 1 Moore Machine Output dependent on register outputs Simpler Boolean math, more complex hardware Outputs occur in states Mealy Machine Output dependent on register outputs and current inputs More complex Boolean math, simpler hardware setup Often less states than Moore Outputs occur in transitions between states State Diagram https://ece.uwaterloo.ca/~cgebotys/NEW/223-9notes.htm Transition Table 1) Understand the given requirements and conditions. 2) Decide on a Mealy or Moore implementation. 3) Create a state diagram using the minimal number of states. a. If single input, 2 arrows should leave each state. b. If two inputs, 4 arrows should leave each state. 4) Assign binary values to each state. a. If two states, need a single register and assign to 0 and 1. b. 2 registers can hold up to 4 states. 5) Create a state transition table listing the current state (individual bits), inputs, and next state (individual bits). 6) Decide on a register type (D, JK, T) 7) Use excitation tables for the chosen registers to finish transition table. Current State 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Inputs 0 0 0 1 Next State 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1 J0 0 1 0 1 X X X X K0 X X X X 0 1 0 0 J1 0 1 1 0 X X X X K1 X X X X 0 1 1 1 Output 0 1 Gate Implementation 1) For each individual register input and each output, create a separate K-map and find a minimum SOP. a. Moore outputs are only dependent on current state b. Mealy outputs are dependent on current inputs and current state. 2) Using proper gates, build a gate array for the minimum SOP of each input and output. 2’s Compliment Start: 1. Switch 1’s and 0’s. 2. Add 1 to the last digit Alternate method: Rules: - The first 1 becomes a 1. All 0’s before the first 1 become 0’s. After the first 1, replace all 1’s with 0’s and all 0’s with 1’s: 100101010 011010110 111000000 001000000 100101010 011010101 011010110 Binary, Decimal, and Hexadecimal Decimal represents numbers as powers of 10. Example: 510 = 5*102 + 1*101 + 0*100. Binary, similarly, represents numbers as powers of 2. Ex: 1011 = 1*23 + 0*22 + 1*21 + 1*20 = 8+2+1 = 11dec. 1 digit of hexadecimal corresponds to four bits: BINARY 0000 0001 0010 0011 0100 0101 0110 0111 HEXADECIMAL 0 1 2 3 4 5 6 7 BINARY 1000 1001 1010 1011 1100 1101 1110 1111 HEXADECIMAL 8 9 A B C D E F Half Adder Adds A and B A 0 0 1 1 B 0 1 0 1 Sum 0 1 1 0 Carry 0 0 0 1 Has no carry-in, can only sum to 01 or 10, not 11. Full Adder Adds A and B, with a Cin. This allows multiple full adders to be chained to create a multi-bit adder. A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 0 1 Cin 0 1 0 1 0 0 1 1 Sum 0 1 1 0 1 1 0 1 Cout 0 0 0 1 0 0 1 1 Multiplexer Takes multiple data inputs but selects which one goes to the output based on the selector inputs. AB F 00 01 C0 C1 10 11 C2 C3 Decoder A multiplexer, in reverse. (Also called demultiplexer) If enabled, whichever output is selected by the selector inputs, C1 and C0 gets a 1, all others get 0.