System in Package Design and Simulation Challenges

advertisement

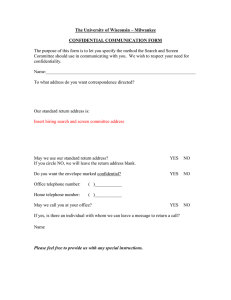

Design for Reliability for System-in-Package Stoyan Stoyanov*, Chris Bailey*, Nadia Strusevich* and Jean-Marc Yannou** *University of Greenwich, London, UK Copyright Confidential **NXP, Caen, France Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-forReliability • Conclusions Copyright Confidential Motivation + Objectives • Design for Reliability modelling for SiP – Thermal + Thermo-mechanical – Reliability Prediction aid for SiP structures – Reduced Order Models • Optimisation Techniques – Design parameters, materials, etc – Include data uncertainties Copyright Confidential Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-forReliability • Conclusions System-in-Package Copyright Confidential What is SiP • SiP (ITRS) “Any combination of semiconductors plus optionally other components such as passives, MEMS, and optical components assembled into a single package” • Wafer-Level Chip Scale Packaging Integrated Circuit Package with most process steps shifted at the wafer-level in the wafer foundry (as opposed to IC-level packaging) offering direct IC-to-PCB connections • WL-SiP (NXP) Copyright Confidential Why SiP Size Reduction Complexity Reduction Design Effort Reduction Power Reduction Lower System Cost More than Moore: Diversification Analog/RF Baseline CMOS: CPU, Memory, Logic Moore’s Law: Miniaturization • • • • • Passives 130nm 45nm 32nm 22nm Co mb ini Information Processing Digital content System-on-Chip (SoC) Copyright Biochips Interacting with people and environment Non-digital content (SiP) 90nm 65nm Sensors Actuators HV Power ng So C More than Moore an dS i P: Hi gh er Confidential Va lue Sy ste ms Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-forReliability • Conclusions Copyright Confidential System-in-Package WL-SiP Reliability Challenges • WLP modules are generally larger for SiP than for Single IC’s – Thermal miss-match – Board Level solder joint Reliability main concern – BLR of WLP worsens with larger dies • WLP modules to be assembled lead-free – Compliance to RoHS – No lead in the wafer-fab Copyright Confidential Need for Co-Design in SiP Copyright Confidential Integrated Analysis in Design • Integration taking place – Electronic Design Automation (EDA) tools now addressing Packaging – IC, RF, PCB Designs – Integrated Analysis Tools Thermo-Mechanical EMC Functional Source: Flomerics Limited Copyright Confidential 10 Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-for-Reliability • Conclusions Copyright Confidential System-in-Package 11 Fan-out (Embedded) Concept • A new SiP-friendly package platform processed at the wafer level with built-in substrate routing mold 12 Copyright Confidential Fan-out versus Fan-in WLCSP • Fan-out WLCSP • Fan-in WLCSP – Is miniature and low cost (Wafer-Scale Packaging) – Reliable up to 15mm² – Package cost impacted by wafer yield – Pad limitation – Poor acceptance (bare Si) by some customers – Is miniature and low cost (Wafer-Scale Packaging) – Expected high reliability even for large packages – Package cost only spent on known good dice – No pad limitation – Good customer acceptance (molded lid) – Excellent substrate isolation in between components – High Q low-cost inductors – Is highly SiP compatible (2D & 3D) IC Inductor in RDL 13 Copyright Confidential Analysis of an Fan-out SIP structure • • Thermo-Mechanical Modelling (Thermal Cycling) Simulation technology used to assess the effect of – Mold thickness – Fan-out ratio – Mold material Passive Die Mold Compound Underfill Active Die Computer Model: 1/8 section of an Embedded Die SiP (Fan-Out Package) IC2 IC1 Redistribution layer (RDL) PCB Redistribution layer (RDL) IC2 IC1 PCB 14 IC3 Copyright Confidential Effect of Mold Compound Thickness (1) Mold Compound Properties: CTE: α1=10ppm/ºC, α2=45ppm/ºC (Tg=130ºC) Young Modulus = 20.E+9Pa Poisson’s Ratio = 0.35 Embedded Die SiP without Underfill Mold Mold Thickness 20μm Chip Fixed Chip Thickness 80μm Mold Thickness 320μm Mold Thickness 120μm Copyright Confidential 15 Effect of Mold Compound Thickness (2) Solder Joint Reliability Metric: Accumulated creep energy in solder per thermal cycle Die Reliability Metric: Maximum effective stress during thermal cycling 120000 100 Effective Stress (MPa) Solder Damage (Pa) 100000 80000 60000 Solder Damage changes by 40% in the mold thickness range 40000 20000 0 0 100 200 300 400 Mold Thickness (um) 80 60 Die Stress changes by 70% in the mold thickness range 40 20 0 0 50 100 150 200 300 350 Mold Thickness (um) Lower Mold Compound Thickness improves reliability Copyright 250 Confidential 16 Effect of Fan-out Ratio (1) Embedded Die SiP without Underfill Mold Mold Compound Total Area is fixed: 5700x5700μm2 Chip Chip Fan-out Ratio =Total Area : Chip Area 1130μm 1400μm 2000μm Chip Chip Chip 1720μm 1450μm 850μm Mold Ratio 2 Mold Copyright Ratio 4 Confidential Mold Ratio 6 17 Effect of Fan-out Ratio (2) Chip Chip Chip Mold Mold Mold Ratio 2 Ratio 6 Ratio 4 800000 Solder Damage for FanOut Ratio 2 is 20 times higher than for the package with Ratio 6 600000 400000 200000 Effective Stress (MPa) Solder Damage (Pa) Stress in the Chip for FanOut Ratio 2 is higher by 90% than in the package with Ratio 6 100 1000000 80 60 40 20 0 Ratio 2 Ratio 4 0 Ratio 6 Ratio2 Higher Fan-out Ratio improves reliability Copyright Confidential Ratio4 Ratio6 18 Effect of Mold Material (1) Mold • Three options for mold selection considered Material CTE (ppm/oC) Mold Compound 1 ⎧α1 = 58 , Tg = 450 C ⎨ ⎩α 2 = 137 ⎧α1 = 10 , Tg = 1300 C ⎨ ⎩α 2 = 45 ⎧α1 = 7 , Tg = 1650 C ⎨ ⎩α 2 = 30 Mold Compound 2 Mold Compound 3 Young Modulus (Pa) Poisson’s Ratio 1.91E+9 0.35 20.0E+9 0.35 25.0E+9 0.3 Mold Compounds Material Properties Copyright Confidential 19 Effect of Mold Material (2) Die Reliability Metric: Maximum effective stress during thermal cycling Solder Joint Reliability Metric: Accumulated creep energy in solder per thermal cycle 60 1600000 Effective Stress (MPa) Solder Damage (Pa) 2000000 1200000 800000 50 40 30 20 400000 10 0 Mold 1 Mold 2 Mold 3 0 Mold 1 Best mold with respect solder joint reliability is Mold 2 Copyright Confidential Mold 2 Mold 3 20 Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-for-Reliability • Conclusions Copyright Confidential System-in-Package 21 Transmitter Receiver Module (TRM): an Avionics Application ASIC (Application Specific Integrated Circuit) MMIC (Millimetre Microwave Integrated Circuit) Low Melting Point Solder 63Sn37Pb Solder 90Pb10Sn Path of Crack Propagation Lifetime Prediction Model • • Uses data from FEA: Predicts damage in solder Lifetime model: Predicts crack growth rate (Ri) • • Cycles Prior to Crack Initiation Are Ignored Total Crack Length = ∑ Ni . Ri i Crack ( Ni - number of thermal cycles for cycle number i) • Failure Criteria: A joint fails if the crack extends beyond half the diameter of the joint at the interface 22 Copyright Confidential Thermal Cycles under Investigations Temp. Type Cycle Cycle No. # Equipment Operating Description Ambient Air Temperature (°C) Inlet Air Temperature (°C) Min Max Min Max No of Cycles Duration of Single Event (mins) Total No of Hours Life 1 1 Production PCA-ESS (passive) No Test 2 2 Production SRI-ESS (passive) No -40 90 -26 54 10 15 N/A 3 3 Production LRI-ESS Yes -40 70 -26 54 10 90 N/A 4 4 Production LRI-PAT Yes -19 60 -19 30 15 90 N/A 5 5 Production ATP (SRI) Yes 15 25 15 25 2 30 N/A 5 6 Production ATP ( LRI) Yes 15 25 15 25 3 60 N/A - 7 Storage 6 8 Flight 1x cold Yes -31 N/A 15 400 90 600 7 9a N/A 15 1400 90 2100 9b Yes 5 8 Flight 7x normal N/A 35 15 1400 90 2100 9 10 Flight 2 x hot Yes N/A 70 15 800 90 1200 10 11 Maintenance ATP (SRI) Yes 15 25 15 25 2 30 N/A 11 12 Maintenance ATP (LRI) Yes 15 25 15 25 3 60 N/A 12 13 Non-Flight Days cold No -33 -22 N/A N/A 875 1440 N/A 13 14 Non-Flight Days normal No 5 25 N/A N/A 6125 1440 N/A 14 15 Non-Flight Days hot No 33 71 N/A N/A 1750 1440 N/A 15 16 Ground Running 1x cold Yes -31 N/A -26 N/A 200 90 300 16 17a N/A 10 N/A 700 90 1050 17b Yes 5 17 Ground Running 7x normal N/A 35 N/A 45 700 90 1050 18 18 Ground Running 2 x hot Yes N/A 70 N/A 54 400 90 600 No Test 23 Copyright Confidential Simulation of Crack Growth Rate [μm] for Various Field Cycles (Life Time Spec) Path of Crack Propagation 2.0E-07 Modelling Predictions for the worst case of the module without underfill 1.5E-07 1.0E-07 5.0E-08 G ) or m al (b ro un d R un 7_ N D ay s H ot al N on D ay s Copyright -F l ig ht N or m ot ht 2x H -F li g ht Fl ig or m al (b ) N on Fl ig ht 7x N or m al (a ) ht 7x N Fl ig ht 1x C ol d 0.0E+00 Fl ig R, Crack Growth Rate (um/cycle) 2.5E-07 Confidential 24 Total Crack Length Calculation Cycle Crack Length after required cycles (μm) Flight 1 x Cold Radius = 230 μm 92 Flight 7 x Normal (a) 25.2 Flight 7 x Normal (b) 16.9 Flight 2 x Hot 128 Non-Flight days Normal 144 Non-Flight days Hot 77.9 Ground Running 7 x Normal 8.5 For Total Covered Cycles 494 Crack length Propagation Total Crack Length under the expected field cycles exceeds the critical failure limit, i.e. with no underfill the package will not survive the required life Copyright Confidential 25 Achieving Required Reliability • Underfill will enhance reliability • Different underfills simulated • With certain underfills the required reliability can be achieved Damage in solder decreases No Underfill Underfill A Underfill B Underfill C Underfill D 26 Copyright Confidential Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-forReliability • Conclusions Copyright Confidential System-in-Package Integrated Numerical Analysis Framework Reduced Order Modelling + Sensitivity Analysis High Fidelity Model Design of Experiment Process/Product parameters Reduced Order Model Generation Sensitivity Analysis Key process/product parameters Uncertainty Analysis Design Data Uncertainty Risk Analysis Optimisation Decision: alternatives Copyright Forecast Uncertainty, Process/Product Capability Decision: Optimal Design Confidential Fan-in stacked die SiP Structure Copyright Confidential Finite Element Model • Finite Element Model of SiP – One-eight section of the package due to symmetry – Underfill applied • Material Properties – Inelastic creep behaviour for solder ⎛ – Temperature dependent ε&ijcr = A (sinh (α σ eff )) n exp⎜⎜ − Q ⎝ RT Copyright Confidential ⎞ ⎟⎟ ⎠ Design Variables 1. PCB thickness (HPCB) 2. Board level solder joints stand-off-height (SOH) 3. Passive die thickness (HDIE) Copyright Confidential Damage Parameters • Two SiP responses under accelerated thermal cycling have been observed 1) Maximum warpage of the package Dw 2) Mean fatigue life of solder joints Nf Life-time model N f = (aWp ) b Warpage at 125C Solder Joints Damage Copyright Confidential Design Steps Flow 1. Identify experimental design points 2. Obtain responses (lifetime, warpage) at each design point • Undertake finite element analysis at each design point. 3. Construct Response Surface Approximation 4. Include formulations to account for – – – Parameter uncertainties Reliability requirements Robust design requirements Copyright Confidential Design of Experiments FEA at experimental points Response Surface Modelling (ROM) Sensitivity Analysis Reliability Robustness Uncertainties Design Task as Optimisation Problem / Design Solution Step 1: Design of Experiments • Central Composite Design (CCD) • 15 Design points • FEA Responses for • Cycles to failure (Nf) • Warpage of SiP (Dw) Factorial Point Axial Point Central Point Copyright Confidential Step 2: Response Surface Modelling • Response Surface Models represent response data: – Warpage of SiP – Lifetime of solder joints • Fast design evaluations for SiP • Accuracy using statistical tools – ANOVA – Efficiency measures – E.g. coefficient of multiple determination for both models is 99.9% Copyright Confidential Design Task • A SiP design is defined as reliable if it satisfies the constraints in the design task • Task formulated as Warpage optimisation problem Life-time SiP thickness Copyright Confidential (a) Deterministic Optimal Design • Design task solved using numerical optimisation techniques • Optimal design – Warpage reduced by 22 % – Lifetime Satisfied Deterministic Formulation Copyright Confidential (b) Effect of Uncertainties • Design variables have uncertainties Probabilistic Optimal design • Probability of Failure – the n-sigma design approach is needed Critical Response 2 Design Variable B – Will impact system responses – Reliability requirements may be violated due to uncertainty of the inputs Critical Response 1 Design Variable A • SiP design variables modelled Deterministic Optimal design with Gaussian distribution • Standard deviations: a) HPCB: σHPCB = 16 um; b) SOH: σSOH = 2 um; c) HDIE: σHDIE = 2.5 um; Copyright Confidential Effect of Uncertainties Design for Reliability • Constraints re-defined in terms of probability of failure • Monte Carlo simulations – Evaluation of the distribution of the response values 800 Frequency 600 95 % of designs have required life-time 400 200 0 2640 2660 2680 2700 2720 2740 2760 2780 2800 2820 Fatigue Life (cycles) Uncertanty at Reliable Optimum Copyright Confidential Probabilistic Formulation Effect of Uncertainties Design for Robustness • Design for Robustness – design that has minimum uncertainty (variation) of its responses • Focus is on life-time 800 Frequency 600 ± 1σ σ=14 cycles 400 200 0 2340 2360 2380 2400 2420 2440 2460 2480 2500 2520 Fatigue Life (cycles) Uncertanty at Robust Optimum Copyright Confidential Probabilistic Formulation Content • • • • • Motivation SiP and Wafer Level Packaging Technology Challenges Fan-Out Design Concept Lifetime Assessment for solder crack in a MMIC Device (Avionics Applications) • Virtual Prototyping and Design-forReliability • Conclusions Copyright Confidential System-in-Package Conclusions + Acknowledgments • • Lots of interest in SiP and Wafer Level SiP Design-for-Reliability for SiP is a key requirement – No clear integration between IC and Packaging – Design of Experiments to understand complex interactions – Optimisation is deterministic – No account of data uncertainties – Reduced Order Models required – Include data, design and process uncertainties Copyright Reduced Order Modelling High Fidelity Modelling Confidential Design of Experiments Response Surface Analysis OPTIMISATION ENGINE Uncertainty Analysis Sensitivity Analysis Design Optimisation