bjt_biasing_theory

advertisement

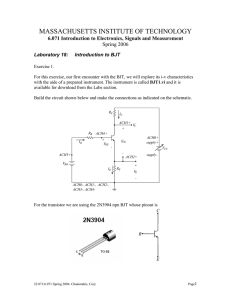

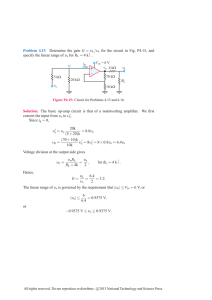

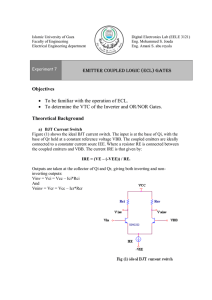

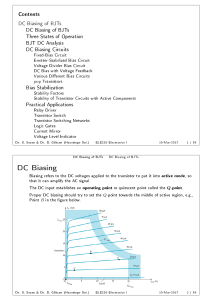

BJT Biasing Theory For a BJT to be used as an amplifier, DC bias is applied to fix IC and VCE at a constant IB (operating point) on the linear or active part of the characteristics. One of the configurations of biasing called Fixed Biasing is shown in 1. The operating point is also referred to as quiescent point Q shown in figure 2. Biasing refers to the application of DC voltages to setup the operating point in such a way that undistorted output signal is provided during the operation. The quiescent point has a direct impact on the maximum swing that can be obtained at the output. Once selected properly, the Q point should not shift because of change of IC due to * β variation due to replacement of the transistor of same type * Temperature variation The reverse saturation current changes with temperature. Specifically, ICO doubles for every 10◦ C rise in temperature. The collector current IC causes the collector junction temperature to rise, which in turn increases ICO . As a result of this increase in ICO , IC will increase as IC = βIB + (1 + β)ICO and will cause the operating point to shift. If the variation is small, it may at the most result in distortion which is not desired though. But if not stabilized, this may continue and the ratings of the transistors may get exceeded resulting in thermal runaway. The most popular biasing circuit is potential divider biasing shown in figure 3. A potential divider consisting of R1 and R2 (see figure 3) is used to establish the desired DC bias voltage VBB at the base. 1 Figure 1: Amplifier Circuit Figure 2: The DC load line and Q point 2 Figure 3: Potential Divider Biasing Figure 4: Thevenin Equivalent Circuit 3 DC Analysis 1. Thevenin equivalent of base circuit gives equation 1 VBB = R2 VCC R1 + R2 (1) 2. The Thevenin Resistance at the base (RB ) is given by equation 2 RB = R1 ||R2 (2) 3. Applying KVL to base circuit loop and collector circuit loop we get equations 3 and 4 VBB = IB RB + IE RE + VBE (3) VCC = IC RC + VCE + IE RE (4) Solving we get, IE = (VBB − VBE )(β + 1) RB + (β + 1)RE (5) where, VBE = 0.7 V * Since VBB >> VBE , small variations in VBE can be swamped by VBB . However, if VBB is made too large, the voltage VCE gets reduced and that limits the voltage swing. Hence as a rule of thumb while designing the biasing circuit; VBB , VCE and IC RC are chosen to be 31 VCC * RE >> RB β+1 If RE is sufficiently large compared to RB , any small variation in β does not affect IE and hence IC to a large extent. This is achieved by choosing small RB . However, if RB is made too small, the input resistance of the amplifier is reduced. Typically, current through the potential divider is chosen to be about 0.1IE to keep the current drain from power supply minimum. Role of RE: RE provides negative DC feedback and stabilizes IE and hence IC . Any increase in IE raises the emitter voltage VE reducing base emitter forward bias. This reduces further increase in base current IB and in turn IC and hence IE . 4 Design Steps If one wishes to design the bias network for an amplifier for given values of IE and VCC , following steps are to be followed. 1. Rule of thumb : VB = 13 VCC . 2. VE = VB − 0.7 3. RE = VE IE 4. Assuming negligible base current, current through R1 + R2, VCC = 0.1IE R1 + R2 I1 = R1 + R2 = 5. VB = VCC 0.1IE (6) (7) R2 V R1 +R2 CC +R2 R2 = VB RV1CC 6. IE to ensure the value of RE . Obtain the value of IE IE = (VBB − 0.7)(β + 1) RB + (β + 1)RE (8) There could be slight variation in this value of IE from the nominal value. Adjust RE to get close approximation to nominal value of IE . 7. IC = β I β+1 E VC = 23 VCC RC = VCC −Vc IC 5