A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration

advertisement

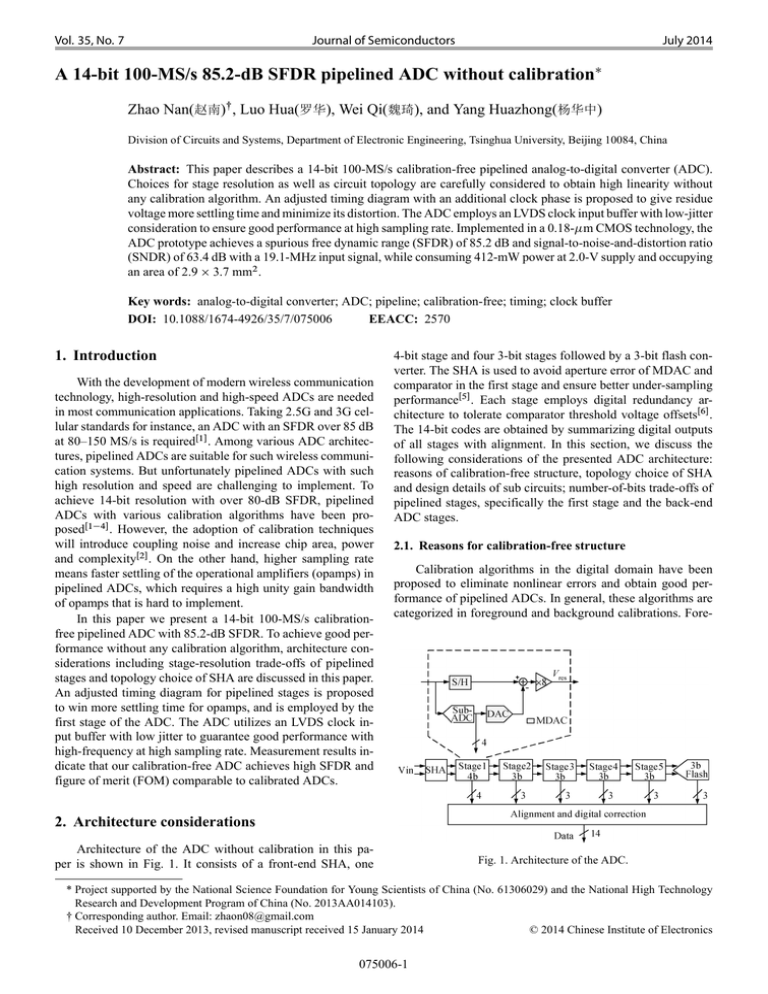

Vol. 35, No. 7 Journal of Semiconductors July 2014 A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration Zhao Nan(赵南) , Luo Hua(罗华), Wei Qi(魏琦), and Yang Huazhong(杨华中) Division of Circuits and Systems, Department of Electronic Engineering, Tsinghua University, Beijing 10084, China Abstract: This paper describes a 14-bit 100-MS/s calibration-free pipelined analog-to-digital converter (ADC). Choices for stage resolution as well as circuit topology are carefully considered to obtain high linearity without any calibration algorithm. An adjusted timing diagram with an additional clock phase is proposed to give residue voltage more settling time and minimize its distortion. The ADC employs an LVDS clock input buffer with low-jitter consideration to ensure good performance at high sampling rate. Implemented in a 0.18-m CMOS technology, the ADC prototype achieves a spurious free dynamic range (SFDR) of 85.2 dB and signal-to-noise-and-distortion ratio (SNDR) of 63.4 dB with a 19.1-MHz input signal, while consuming 412-mW power at 2.0-V supply and occupying an area of 2.9 3.7 mm2 . Key words: analog-to-digital converter; ADC; pipeline; calibration-free; timing; clock buffer DOI: 10.1088/1674-4926/35/7/075006 EEACC: 2570 1. Introduction With the development of modern wireless communication technology, high-resolution and high-speed ADCs are needed in most communication applications. Taking 2.5G and 3G cellular standards for instance, an ADC with an SFDR over 85 dB at 80–150 MS/s is requiredŒ1 . Among various ADC architectures, pipelined ADCs are suitable for such wireless communication systems. But unfortunately pipelined ADCs with such high resolution and speed are challenging to implement. To achieve 14-bit resolution with over 80-dB SFDR, pipelined ADCs with various calibration algorithms have been proposedŒ1 4 . However, the adoption of calibration techniques will introduce coupling noise and increase chip area, power and complexityŒ2 . On the other hand, higher sampling rate means faster settling of the operational amplifiers (opamps) in pipelined ADCs, which requires a high unity gain bandwidth of opamps that is hard to implement. In this paper we present a 14-bit 100-MS/s calibrationfree pipelined ADC with 85.2-dB SFDR. To achieve good performance without any calibration algorithm, architecture considerations including stage-resolution trade-offs of pipelined stages and topology choice of SHA are discussed in this paper. An adjusted timing diagram for pipelined stages is proposed to win more settling time for opamps, and is employed by the first stage of the ADC. The ADC utilizes an LVDS clock input buffer with low jitter to guarantee good performance with high-frequency at high sampling rate. Measurement results indicate that our calibration-free ADC achieves high SFDR and figure of merit (FOM) comparable to calibrated ADCs. 4-bit stage and four 3-bit stages followed by a 3-bit flash converter. The SHA is used to avoid aperture error of MDAC and comparator in the first stage and ensure better under-sampling performanceŒ5 . Each stage employs digital redundancy architecture to tolerate comparator threshold voltage offsetsŒ6 . The 14-bit codes are obtained by summarizing digital outputs of all stages with alignment. In this section, we discuss the following considerations of the presented ADC architecture: reasons of calibration-free structure, topology choice of SHA and design details of sub circuits; number-of-bits trade-offs of pipelined stages, specifically the first stage and the back-end ADC stages. 2.1. Reasons for calibration-free structure Calibration algorithms in the digital domain have been proposed to eliminate nonlinear errors and obtain good performance of pipelined ADCs. In general, these algorithms are categorized in foreground and background calibrations. Fore- 2. Architecture considerations Architecture of the ADC without calibration in this paper is shown in Fig. 1. It consists of a front-end SHA, one Fig. 1. Architecture of the ADC. * Project supported by the National Science Foundation for Young Scientists of China (No. 61306029) and the National High Technology Research and Development Program of China (No. 2013AA014103). † Corresponding author. Email: zhaon08@gmail.com Received 10 December 2013, revised manuscript received 15 January 2014 © 2014 Chinese Institute of Electronics 075006-1 J. Semicond. 2014, 35(7) Zhao Nan et al. Fig. 2. Schematics of SHA and the amplifier. ground calibration, which measures non-ideal transfer function of a pipelined ADC before its conversion, results in an interruption of normal operation and can’t track the variation of environment. Background calibration estimates the nonlinear errors during the conversion, and calculates accurate digital outputs continuously. However, main background calibrations have limitations of input signal. For example, correlationbased calibration cannot accept a randomized input signal, while statistics-based calibration requires an input signal with widely distributed magnitude. The limitations of input signal greatly narrow the application area of background calibration. Besides, convergence issues exist in background calibrations due to millisecond-level converging time, which is hard to tolerate in some applications. No matter which calibration algorithm is adopted, it will inevitably introduce coupling noise to analog circuits, and enlarge the power consumption, the chip area and circuit complexity. Therefore, calibration-free structure is utilized by the demonstrated ADC. Arbitrary input signal can be applied to this ADC, with no worries about interrupting conversion and converging problems. What’s more, it will take no extra power, area or circuit complexity. These advantages make the calibration-free structure widely used in industry productions, but lead to difficulties of opamp designing as a corresponding cost. To minimize the design challenge of opamps in a calibration-free structure, the proposed ADC carefully arranges the stage resolution and adopts an adjusted timing diagram, as discussed later in this paper. 2.2. Topologies of SHA and its opamp Since the accuracy and noise requirement of the frontend SHA is the strictest, the SHA should be carefully designed. Flip-around architecture is adopted for low noise and low power, in which a sampling capacitance of 4 pF is chosen for thermal noise consideration. To obtain enough signal swing with low power supply, a Miller compensated two-stage amplifier is applied. The first stage of the amplifier uses telescopic topology rather than folded-cascode to push the seconddominant pole to higher frequency and achieve sufficient unity gain bandwidth, while enhancing the open-loop gain of the am- plifier by adopting auxiliary gain boosters. Figure 2 gives the schematics of SHA and the amplifier. 2.3. Consideration of stage resolutions For pipelined ADCs with over 10-bit resolution, multi-bit stages are frequently used to decrease the accuracy requirement of MDACsŒ7 9 , which can further relax the requirements of capacitor mismatch as well as settling error of opamps. Different from the fixed stage resolution of 1.5-bit stages, the number of bits in multi-bit stages should be determined with various design concerns in different applications. For the first stage, it is desirable to maximize the number of bits so as to maximize the SNR and minimize the static error caused by capacitor mismatch, which in turn reduces the tolerance of comparator offsetŒ7 . A 4-bit structure is chosen in this design for the trade-off between capacitor mismatch and comparator offset. The design difficulty of the opamp which the calibration-free structure brings in is minimized due to 4bit stage resolution. A residue gain of eight is guaranteed by eight unit sampling capacitors, which also serve as the loading capacitor of front-end SHA, and one unit feedback capacitor of the MDAC, as shown in Fig. 3. To meet 11-bit matching accuracy, the value of the sampling capacitors is 625 fF each, with a total of 5 pF. In comparison, a 3-bit structure has a residue gain of four and the capacitor needs to meet 12-bit matching accuracy. So the unit capacitor is 1.5 pF and the total amount of the sampling capacitors is 6 pF, which is larger than that of the 4-bit condition. Hence the employment of a 4-bit stage results in a reduction of the SHA’s loading capacitor, making the amplifier of SHA more power-efficient. It also eases layout arrangement requirements due to the relaxed capacitor matching accuracy. Moreover, the following back-end stages can be scaled down to save power and area once the 4-bit structure is usedŒ8 . Although the comparator offset tolerance is decreased as a sacrifice, 4-bit structure brings in more benefits. Besides, small offset can be achieved by careful design and layout of comparators as well as the employment of front-end SHA, which can avoid aperture error. The back-end pipelined ADC chooses 3-bit stages rather than 2.5-bit ones to enhance linearityŒ10 . Ideal residue range of 075006-2 J. Semicond. 2014, 35(7) Zhao Nan et al. In the conventional timing diagram, the digital codes are generated during the delay time td of ˚1 and the nonoverlapping time tn between ˚1 and ˚2 , as demonstrated in Fig. 5. The decoder begins to process the digital codes at the rising edge of ˚2 , and outputs switch-control signals after a delay time of td; dec . During td; dec , the sampling capacitors are not connected to any voltage while CF is connected to the amplifier’s output. Charge redistribution does not take place until Csi are connected to reference voltages. Thus the residue voltage can be generated only after the delay time td; dec . The timing in Fig. 5 causes two problems. One is that the delay time of the decoder occupies settling time of the residue voltage, which leads to more dynamic settling error. The other is that large overshoot of residue voltage emerges due to floating Csi during td; dec . It takes much time to pull the overshoot back and thus causes insufficient settling of the residue. To overcome the above disadvantages, the rising edge of the decoder’s triggering clock should be earlier than the rising edge of ˚2 so that td; dec is moved out of the amplifying phase. Figure 6 presents the adjusted timing diagram. An additional clock phase ˚2a triggers the decoder as a substitution of ˚2 to offer an earlier rising edge, and it’s simply implemented by shifting ˚2 leftwards to minimize circuitry complexity. As a result, the falling edge of ˚2a is also earlier than that of ˚2 , but this does not reduce the settling time of the residue since the residue is sampled by the next stage at the falling edge of ˚2e , which is still earlier than ˚2a . By adopting ˚2a , the sampling capacitors are connected to reference voltages at the very beginning of ˚2 , maximizing the settling time of the residue. Besides, the overshoot due to capacitor floating are decreased, which also benefits settling. The adjusted timing with addition ˚2a is suitable for all pipelined stages, and it’s adopted by the first stage in this design because of its stricter settling accuracy. Fig. 3. 4-bit/stage MDAC of the first stage. 4. Low-voltage differential signaling (LVDS) clock buffer Fig. 4. Residue transfer curves of (a) 3-bit stages and (b) 2.5-bit stages. 3-bit stages is only half that of 2.5-bit stages as shown in Fig. 4. In practice a residue offset which shifts the transfer curve is inevitable. This shift results in out-of-range residue in 2.5-bit stages and thus contributes to nonlinearity. But 3-bit stages can maintain good linearity due to their small residue range. 3. Adjusted timing diagram for pipelined stages Conventional timing diagram as well as a simplified schematic of a pipelined stage is shown in Fig. 5. During the tracking phase ˚1 , the sampling capacitors Csi are connected to input voltage and the feedback capacitor CF is reset. At the sampling instant (the falling edge of ˚1e /, the short switch is closed and the comparators start to convert input voltage into digital codes. During the amplifying phase ˚2 , Csi are connected to reference voltages through switches controlled by the decoder’s outputs, and CF is connected to the amplifier’s output. Then residue voltage is generated due to charge redistribution, and the next stage samples it at the falling edge of ˚2e . Low-voltage differential signaling (LVDS) is widely used as an interface standard of high-speed data transmission for its low noise and good electromagnetic compatibility (EMC)Œ11 . To achieve better performance, clock input of the prototype ADC is transferred as LVDS with a frequency of 100 MHz. Thus an LVDS clock buffer is needed. Figure 7 shows the schematic of the clock input buffer, which comprises a differential-to-single amplifier and a short inverter chain. The differential-to-single amplifier transforms LVDS clock input to single-ended logical signals, which is then sent to the inverter chain to obtain sharp clock edges and sufficient driving capability. Both the amplifier and the inverter chain introduce clock jitter, which must be diminished in highspeed applications. The jitter, regarded as a random timing error, significantly deteriorates ADC performance by degrading signal-to-noise ratio (SNR), especially with high-frequency input signal. The relationship between SNR and clock jitter is given by Eq. (1), regardless of effective input noise of ADC and quantization noiseŒ12 : 075006-3 SNR D 20 lg 1 2fsig tjitter : (1) J. Semicond. 2014, 35(7) Zhao Nan et al. Fig. 5. Conventional timing diagram and simplified schematic for a pipelined stage. Fig. 6. Adjusted timing diagram for the first stage of the ADC. Fig. 7. Schematic of the clock input buffer in the ADC. Fig. 8. Simulation result of jitter in LVDS clock buffer. It indicates that SNR is inversely proportional to the signal frequency and clock jitter. For a 14-bit 100-MS/s ADC, if the effective number of bits (ENOB) is expected to maintain 13 bit in the first Nyquist zone (indicating a maximal input frequency of 50 MHz), the jitter should be less than 318 fs. In practice we reduce the jitter to below 200 fs with concern of the effective input noise of ADC and the quantization noise. One way to reduce jitter is to improve the slew rate of clock edges by raising the gain of clock amplifier. Cross-coupled MOS load and multi stages are common approachesŒ13; 14 . However, both of them introduce more thermal noise and hence contribute to extra jitter. In this design, a trade-off is made by using a single-stage amplifier with diode load, of which the gain is enlarged by expanding transistor length and the noise is reduced with fewer transistors. Besides, as shown in Eq. (2)Œ15 , each active component in the signal chain will increase the total amount of jitter, which indicates that minimizing the number of gates in the invertor chain helps keep the total jitter low. Thus 075006-4 J. Semicond. 2014, 35(7) Zhao Nan et al. Fig. 9. Die photograph. Fig. 11. Measured SNDR and SFDR versus input frequency. Table 1. Measured performance summary. Parameter Value Technology 0.18-m 1P6M CMOS Resolution 14 bit Sampling rate 100 MS/s Input range 2 Vpp Supply voltage 2V Area 2.9 3.7 mm2 Total power 412 mW SFDR 85.24 dB (fin D 19.1 MHz) 80.94 dB (fin D 79.1 MHz) SNDR 63.44 dB (fin D 19.1 MHz) 58.17 dB (fin D 79.1 MHz) ENOB 10.25 (fin D 19.1 MHz) 9.37 (fin D 79.1 MHz) Fig. 10. FFT spectrum with (a) 19.1-MHz input signal and (b) 79.1MHz at 100 MS/s. only necessary inverters are reserved in the chain to achieve low jitter. With such efforts, the jitter of the whole clock buffer is less than 182 fs according to the simulation result shown in Fig. 8. q 2 2 2 (2) jtotal D jsource; 1 C jsource; 2 C C jsource; n : 5. Measurement results The ADC prototype is fabricated in a 1P6M 0.18-m CMOS process with MIM capacitors. The die photograph is illustrated in Fig. 9. The chip area is 2.9 3.7 mm2 including the bonding pads. The ADC consumes a total power of 412 mW at 2-V supply. FFT spectrums with two different input frequencies are shown in Fig. 10. With 19.1-MHz input signal, the ADC achieves an SFDR of 85.2 dB and an SNDR of 63.4 dB. As the input frequency is raised to 79.1 MHz, the measured SFDR is 80.9 dB, which is only 4.3 dB worse. Figure 11 demonstrates dynamic performance versus input frequency. For an input frequency range of 19.1–79.1 MHz, SFDR varies from 85.2 to 78.9 dB, and SNDR ranges from 63.4 to 58.2 dB. The performance of the ADC is summarized in Table 1. It’s focused on in further work that decreasing noise so as to enhance the SNDR specification, and reducing power. Table 2 shows the performance comparison with prior works of similar resolution and sampling rate. SFDR of the ADC in this paper is comparable to the previous works, and even higher than some calibrated ADCs. FOM of this work is acceptable, and less than most calibrated ADCs, indicating the power advantage of calibration-free structure. 6. Conclusion This paper describes a 14-bit 100-MS/s pipelined ADC without any calibration algorithm. Choices of stage resolution and circuitry topology are discussed to obtain good performance with calibration-free architecture. An adjusted timing diagram with an additional clock phase is employed by the first 075006-5 J. Semicond. 2014, 35(7) Parameter Bits MS/s Power (mW) VDD (V) SFDR (dB) SNDR (dB) Technology (m) FOM1 (pJ/step) FOM2 (pJ/step) With calibration FOM1 D Power , 2ENOB fs Zhao Nan et al. This work 14 100 412 2 85.24 63.44 0.18 3.393 0.225 No FOM2 D Table 2. Performance comparison on several ADCs. Ref. [13] Ref. [14] Ref. [16] Ref. [18] 14 14 14 14 80 80 50 150 518 303 109.55 140 1.8 3.3 1.2 1.2 82.9 84.8 84.1 70 76.5 72 68.67 61 0.18 0.35 0.13 0.13 1.185 1.164 0.992 1.018 0.464 0.218 0.137 0.295 Yes No Yes No Ref. [19] 14 100 230 3.0 86 71 0.18 0.793 0.115 No Ref. [20] 14 100 543 1.8 87.5 70.02 0.18 2.101 0.229 Yes Power 10SFDR=20 fs stage to strive for more settling time, and a low-jitter LVDS clock buffer is utilized to maintain high performance with highfrequency input signal. The prototype ADC achieves 85.2-dB SFDR without calibration, which is comparable to previous works. References [1] Van de Vel H, Buter B A J, van Der Ploeg H, et al. A 1.2-V 250mW 14-b 100-MS/s digitally calibrated pipeline ADC in 90-nm CMOS. IEEE J Solid-State Circuits, 2009, 44(4): 1047 [2] Cho Y J, Lee K H, Choi H C, et al. A calibration-free 14b 70 MS/s 3.3 mm2 235 mW 0.13 m CMOS pipeline ADC with highmatching 3-D symmetric capacitors. IEEE Custom Integrated Circuits Conference, 2006: 485 [3] Daito M, Matsui H, Ueda M, et al. A 14-bit 20-MS/s pipelined ADC with digital distortion calibration. Asian Solid-State Circuits Conference, 2005: 61 [4] Luo L, Lin K, Cheng L, et al. A digitally calibrated 14-bit linear 100-MS/s pipelined ADC with wideband sampling frontend. Proc ESSCIRC, 2009: 472 [5] Yang W, Kelly D, Mehr I, et al. A 3-V 340-mW 14-b 75Msample/s CMOS ADC with 85-dB SFDR at Nyquist input. IEEE J Solid-State Circuits, 2001, 36(12): 1931 [6] Lewis S H, Gray P R. A pipelined 5-Msample/s 9-bit analog-todigital converter. IEEE J Solid-State Circuits, 1987, 22(6): 954 [7] Bardsley S, Dillon C, Kummaraguntla R, et al. A 100-dB SFDR 80-MSPS 14-bit 0.35-m BiCMOS pipeline ADC. IEEE J SolidState Circuits, 2006, 41(9): 2144 [8] Geelen G, Paulus E, Simanjuntak D, et al. A 90 nm CMOS 1.2 V 10 b power and speed programmable pipelined ADC with 0.5 pJ/conversion-step. IEEE International Solid-State Circuits Con- ference, Digest of Technical Papers, 2006: 782 [9] Brunsilius J, Siragusa E, Kosic S, et al. A 16b 80 MS/s 100 mW 77.6 dB SNR CMOS pipeline ADC. IEEE International SolidState Circuits Conference Digest of Technical Papers (ISSCC), 2011: 186 [10] Yin Xiumei, Wei Qi, Xu Lai, et al. A low power 12-b 40-MS/s pipeline ADC. Journal of Semiconductors, 2010, 31(3): 035006 [11] Conpration T I. LVDS application and data handbook. 2010 [12] Kester W. Analog-digital conversion, analog devices. Section 2.3. 2004: p. 2.72, Fig. 2.81 [13] Fan Ye, Cheng Long, Lin Kaihui, et al. An 80-MS/s 14-bit pipelined ADC featuring 83 dB SFDR. Analog Integrated Circuits and Signal Processing, 2010, 63(3): 503 [14] Cai Hua, Li Ping, Cen Yuanjun, et al. A 14-bit 80 MS/s CMOS ADC with 84.8 dB SFDR and 72 dB SNDR. Journal of Semiconductors, 2012, 33(2): 025012 [15] Reeder R, Green W, Shilito R. Analog-to-digital converter: clock optimization. Analog Dialogue 42-02, Feb. 2008 [16] Treichler J, Huang Q. A 11.1-bit ENOB 50-MS/s pipelined A/D converter in 130-nm CMOS without S/H front end. Proc ESSCIRC, 2010: 374 [17] Panigada A, Galton I. A 130 mW 100 MS/s pipelined ADC with 69 dB SNDR enabled by digital harmonic distortion correction. IEEE J Solid-State Circuits, 2009, 44(12): 3314 [18] Choi H C, Yoo P S, Ahn G C, et al. A 14b 150 MS/s 140 mW 2.0 mm2 0.13 m CMOS A/D converter for software-defined radio systems. Int J Circ Theor Appl, 2011, 39: 135 [19] Lee B, Min B, Manganaro G, et al. A 14 b 100 MS/s pipelined ADC with a merged active S/H and first MDAC. ISSCC Digest of Technical Papers, San Francisco, USA, 2008: 248 [20] Wang Ke, Fan Chaojie, Zhou Jianjun, et al. A 14-bit 100-MS/s CMOS pipelined ADC with 11.3 ENOB. Journal of Semiconductors, 2013, 34(8): 085015 075006-6