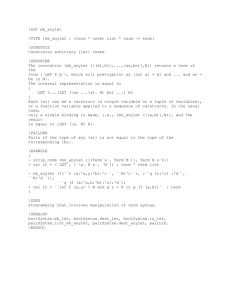

HSPICE behavioral modeling

advertisement