Digital Design

advertisement

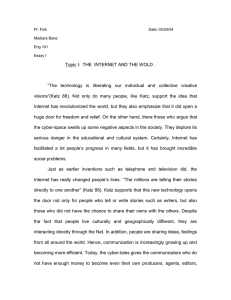

CSE140: Components and Design Techniques for Digital Systems Tajana Simunic Rosing 1 Sources: TSR, Katz, Boriello & Vahid Where we are now… • What we covered thus far: – – – – Number representations Logic gates Boolean algebra Introduction to CMOS • HW#2 due, HW#3 assigned • Where we are going: – – – – Logic representations SOP and POS K-maps Algorithm for simplification 2 Sources: TSR, Katz, Boriello & Vahid Combinational Circuit Introduction Digital circuit • We’ll start with a simple form of circuit: – Combinational circuit • A digital circuit whose outputs depend solely on the present combination of the circuit inputs’ values • Built out of simple components: switches and gates a b a b 1 Combinational 0 digital circuit 1 0 1 Sequential ? digital circuit F F 3 Sources: TSR, Katz, Boriello & Vahid Combinational Logic Design Process Step 2.7 Description Step 1 Capture the function Create a truth table or equations to describe the desired behavior of the combinational logic. Step 2 Convert to equations This step is only necessary if you captured the function using a truth table instead of equations. Simplify the equations if desired. Step 3 Implement as a gatebased circuit For each output, create a circuit corresponding to the output’s equation. 4 Sources: TSR, Katz, Boriello & Vahid Example: Three 1s Detector • Problem: Detect 3 consecutive 1s in 8-bit input: abcdefgh • 00011101 • 01111000 • 10101011 a – Step 1: Capture the function • Truth table or equation? a b c abc bcd d cde – Step 2: Convert to equation e y def f – Step 3: Implement with gates efg g fgh h 5 Sources: TSR, Katz, Boriello & Vahid Example: Seat Belt Warning Light System • • Design circuit for warning light Sensors – s=1: seat belt fastened – k=1: key inserted – p=1: person in seat • Capture logic equation – What are conditions for warning light to go on? • Convert equation to circuit 6 Sources: TSR, Katz, Boriello & Vahid Example: Number of 1s Count • Problem: Output in binary on two outputs yz the number of 1s on three inputs • 010 • 101 • 000 – Step 1: Capture the function • Truth table or equation? – Step 2: Convert to equation – Step 3: Implement as gates a b c a b c a b c a b y a b c z a b c a b c 7 Sources: TSR, Katz, Boriello & Vahid Design example: 1-bit binary adder Cout Cin • Inputs: A, B, Carry-in • Outputs: Sum, Carry-out A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Cin Cout S 0 1 0 1 0 1 0 1 A B Cin A B A B A B A B A B S S S S S S Cout 8 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Representation of logic functions Tajana Simunic Rosing 9 Sources: TSR, Katz, Boriello & Vahid Canonical Form -- Sum of Minterms • Truth tables are too big for numerous inputs • Use standard form of equation instead – Known as canonical form – Regular algebra: group terms of polynomial by power • ax2 + bx + c (3x2 + 4x + 2x2 + 3 + 1 --> 5x2 + 4x + 4) – Boolean algebra: create a sum of minterms • Minterm: product term with every literal (e.g. a or a’) appearing exactly once Determine if F(a,b)=ab+a’ is same function as F(a,b)=a’b’+a’b+ab, by converting the first equation to the canonical form 10 Sources: TSR, Katz, Boriello & Vahid Sum-of-products canonical forms • Also known as disjunctive normal form • Minterm expansion: F = 001 011 101 110 111 F = A’B’C + A’BC + AB’C + ABC’ + ABC A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F 0 1 0 1 0 1 1 1 F’ 1 0 1 0 1 0 0 0 F’ = A’B’C’ + A’BC’ + AB’C’ 11 Sources: TSR, Katz, Boriello & Vahid Sum-of-products canonical form (cont’d) • Product minterm – ANDed product of literals – input combination for which output is 1 – each variable appears exactly once, true or inverted (but not both) A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 minterms A’B’C’ m0 A’B’C m1 A’BC’ m2 A’BC m3 AB’C’ m4 AB’C m5 ABC’ m6 ABC m7 short-hand notation for minterms of 3 variables F in canonical form: F(A, B, C) = m(1,3,5,6,7) = m1 + m3 + m5 + m6 + m7 = A’B’C + A’BC + AB’C + ABC’ + ABC canonical form minimal form F(A, B, C) = A’B’C + A’BC + AB’C + ABC + ABC’ = (A’B’ + A’B + AB’ + AB)C + ABC’ = ((A’ + A)(B’ + B))C + ABC’ = C + ABC’ = ABC’ + C = AB + C 12 Sources: TSR, Katz, Boriello & Vahid Product-of-sums canonical form • Also known as conjunctive normal form • Also known as maxterm expansion • Implements “zeros” of a function F= 000 010 100 F = (A + B + C) (A + B’ + C) (A’ + B + C) A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F 0 1 0 1 0 1 1 1 F’ 1 0 1 0 1 0 0 0 F’ = (A + B + C’) (A + B’ + C’) (A’ + B + C’) (A’ + B’ + C) (A’ + B’ + C’) 13 Sources: TSR, Katz, Boriello & Vahid Product-of-sums canonical form (cont’d) • Sum term (or maxterm) – ORed sum of literals – input combination for which output is false – each variable appears exactly once, true or inverted (but not both) A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 maxterms A+B+C A+B+C’ A+B’+C A+B’+C’ A’+B+C A’+B+C’ A’+B’+C A’+B’+C’ short-hand notation for maxterms of 3 variables M0 M1 M2 M3 M4 M5 M6 M7 F in canonical form: F(A, B, C) = M(0,2,4) = M0 • M2 • M4 = (A + B + C) (A + B’ + C) (A’ + B + C) canonical form minimal form F(A, B, C) = (A + B + C) (A + B’ + C) (A’ + B + C) = (A + B + C) (A + B’ + C) (A + B + C) (A’ + B + C) = (A + C) (B + C) 14 Sources: TSR, Katz, Boriello & Vahid Mapping between canonical forms • Minterm to maxterm conversion – use maxterms whose indices do not appear in minterm expansion – e.g., F(A,B,C) = m(1,3,5,6,7) = M(0,2,4) • Maxterm to minterm conversion – use minterms whose indices do not appear in maxterm expansion – e.g., F(A,B,C) = M(0,2,4) = m(1,3,5,6,7) • Minterm expansion of F to minterm expansion of F’ – use minterms whose indices do not appear – e.g., F(A,B,C) = m(1,3,5,6,7) F’(A,B,C) = m(0,2,4) • Maxterm expansion of F to maxterm expansion of F’ – use maxterms whose indices do not appear – e.g., F(A,B,C) = M(0,2,4) F’(A,B,C) = M(1,3,5,6,7) 15 Sources: TSR, Katz, Boriello & Vahid Incompletely specified functions • Example: binary coded decimal increment by 1 – BCD digits encode the decimal digits 0 – 9 • A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 W 0 0 0 0 0 0 0 1 1 0 X X X X X X X 0 0 0 1 1 1 1 0 0 0 X X X X X X Y 0 1 1 0 0 1 1 0 0 0 X X X X X X Z 1 0 1 0 1 0 1 0 1 0 X X X X X X Don’t cares and canonical forms – – – so far, only represented on-set also represent don’t-care-set need two of the three sets (on-set, off-set, dc-set) off-set of W on-set of W don’t care (DC) set of W these inputs patterns should never be encountered in practice – "don’t care" about associated output values, can be exploited in minimization 16 Sources: TSR, Katz, Boriello & Vahid Alternative two-level implementations of F = AB + C A B F1 canonical sum-of-products C minimized sum-of-products F2 canonical product-of-sums F3 minimized product-of-sums F4 17 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Logic simplification Tajana Simunic Rosing 18 Sources: Sources: TSR, Katz, Katz, Boriello Boriello & & Vahid Vahid Key to simplification: the uniting theorem • Uniting theorem: A (B’ + B) = A • Essence of simplification of two-level logic – find two element subsets of the ON-set where only one variable changes its value – this single varying variable can be eliminated and a single product term used to represent both elements F = A’B’+AB’ = (A’+A)B’ = B’ A B F 0 0 1 0 1 0 1 0 1 1 1 0 B has the same value in both on-set rows – B remains A has a different value in the two rows – A is eliminated 19 Sources: TSR, Katz, Boriello & Vahid Boolean cubes • Visual technique for applying the uniting theorem • n input variables = n-dimensional "cube" 11 01 0 1-cube 1 Y X 00 X 111 3-cube Y Z 000 101 2-cube 10 0111 1111 4-cube Y X 0000 Z W X 1000 20 Sources: TSR, Katz, Boriello & Vahid Mapping truth tables onto Boolean cubes • Uniting theorem combines two “faces" of a cube into a larger “face" • Example: A B F 0 0 1 0 1 0 1 0 1 1 1 0 F 11 01 two faces of size 0 (nodes) combine into a face of size 1(line) B 00 A 10 A varies within face, B does not this face represents the literal B' ON-set = solid nodes OFF-set = empty nodes DC-set = 'd nodes 21 Sources: TSR, Katz, Boriello & Vahid Three variable example • Binary full-adder carry-out logic (A'+A)BCin A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Cin 0 1 0 1 0 1 0 1 Cout 0 0 0 1 0 1 1 1 111 B C 000 AB(Cin'+Cin) 101 A A(B+B')Cin the on-set is completely covered by the combination (OR) of the subcubes of lower dimensionality - note that “111” is covered three times Cout = BCin+AB+ACin 22 Sources: TSR, Katz, Boriello & Vahid Higher dimensional cubes • Sub-cubes of higher dimension than 2 011 111 110 010 000 on-set forms a square - a cube of dimension 2 001 B C A F(A,B,C) = m(4,5,6,7) 101 100 This subcube represents the literal A • In a 3-cube (three variables): – – – – • a 0-cube, i.e., a single node, yields a term in 3 literals a 1-cube, i.e., a line of two nodes, yields a term in 2 literals a 2-cube, i.e., a plane of four nodes, yields a term in 1 literal a 3-cube, i.e., a cube of eight nodes, yields a constant term "1" In general, – an m-subcube within an n-cube (m < n) yields a term with n – m literals 23 Sources: TSR, Katz, Boriello & Vahid Karnaugh maps • Flat map of Boolean cube – wrap–around at edges – hard to draw and visualize for more than 4 dimensions – virtually impossible for more than 6 dimensions • Alternative to truth-tables to help visualize adjacencies – guide to applying the uniting theorem – on-set elements with only one variable changing value are adjacent unlike the situation in a linear truth-table B A 0 1 0 0 1 1 0 2 3 A B F 1 0 0 1 1 0 1 0 0 1 0 1 1 1 0 24 Sources: TSR, Katz, Boriello & Vahid Karnaugh maps (cont’d) • Numbering scheme based on Gray–code – e.g., 00, 01, 11, 10 – only a single bit changes in code for adjacent map cells C AB 0 C 1 0 1 00 11 01 2 3 6 7 A 5 011 111 110 010 001 B C A 0 2 6 4 1 3 7 5 B A 4 B C 10 000 A 101 100 C 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 B D 25 Sources: TSR, Katz, Boriello & Vahid Karnaugh map examples A • F= B 1 1 0 0 • Cout = A 0 0 1 0 Cin 0 1 1 1 B • f(A,B,C) = m(0,4,5,7) C AB 0 C 1 00 11 01 A 0 2 6 4 1 3 7 5 B A 10 C 1 0 0 1 0 0 1 1 B 26 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Logic simplification cont. Tajana Simunic Rosing 27 Sources: Sources: TSR, Katz, Katz, Boriello Boriello & & Vahid Vahid CSE140a HW2 Stats Students (%) 30.0% HW2 Grade Distribution 20.0% 10.0% 0~5 5 ~ 10 10 ~ 15 15 ~ 20 20 ~ 25 25 ~ 30 30 ~ 35 35 ~ 40 40 ~ 45 45 ~ 50 50 ~ 55 55 ~ 60 60 ~ 65 65 ~ 70 70 ~ 75 75 ~ 80 80 ~ 85 85 ~ 90 90 ~ 95 95 ~ 100 0.0% Bucket of Points • • • • • • buckets # students 0~5 14 5 ~ 10 0 10 ~ 15 0 15 ~ 20 0 20 ~ 25 0 25 ~ 30 1 30 ~ 35 0 35 ~ 40 0 40 ~ 45 0 45 ~ 50 1 50 ~ 55 3 55 ~ 60 0 60 ~ 65 4 65 ~ 70 6 70 ~ 75 11 75 ~ 80 18 80 ~ 85 11 85 ~ 90 29 90 ~ 95 11 95 ~ 100 42 students (%) 9.27% 0.00% 0.00% 0.00% 0.00% 0.66% 0.00% 0.00% 0.00% 0.66% 1.99% 0.00% 2.65% 3.97% 7.28% 11.92% 7.28% 19.21% 7.28% 27.81% Total students enrolled : 151 # Solutions received : 137 Max score : 100.00 Min score (w/o 0s) : 30.00 Mean score : 86.03 Median score : 89.00 Sources: TSR, Katz, Boriello & Vahid Where we are now… • What we covered thus far: – – – – Chap 1 Logic representations SOP and POS K-maps • HW#3 due, HW#4 assigned • Midterm #1 next week on Th • Where we are going: – K-maps – more examples – Mux and Demux 29 Sources: TSR, Katz, Boriello & Vahid Karnaugh map: 4-variable example • F(A,B,C,D) = m(0,2,3,5,6,7,8,10,11,14,15) F= A C 1 0 0 1 0 1 0 0 1 1 1 1 1 1 1 1 0111 D C 0000 D A B 1111 1000 B find the smallest number of the largest possible subcubes to cover the ON-set (fewer terms with fewer inputs per term) 30 Sources: TSR, Katz, Boriello & Vahid Karnaugh maps: don’t cares • f(A,B,C,D) = m(1,3,5,7,9) + d(6,12,13) without don't cares with don’t cares f= f= A C A 0 0 X 0 1 1 X 1 1 1 0 0 0 X 0 0 B D 0 0 X 0 1 1 X 1 1 1 0 0 0 X 0 0 D C B don't cares can be treated as 1s or 0s depending on which is more advantageous 31 Sources: TSR, Katz, Boriello & Vahid Another Example • F = m(0, 2, 7, 8, 14, 15) + d(3, 6, 9, 12, 13) A C 1 0 X 1 0 0 X X X 1 1 0 1 X 1 0 D B 32 Sources: TSR, Katz, Boriello & Vahid Design example: two-bit comparator N1 N2 A B C D LT EQ GT AB<CD AB=CD AB>CD block diagram and truth table A 0 B 0 0 1 1 0 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 LT 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 EQ 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 GT 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 we'll need a 4-variable Karnaugh map for each of the 3 output functions 33 Sources: TSR, Katz, Boriello & Vahid Design example: two-bit comparator (cont’d) A C A 0 0 0 0 1 0 0 0 1 1 0 1 1 1 0 0 D C A 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 D C 0 1 1 1 0 0 1 1 0 0 0 0 0 0 1 0 B B B K-map for LT K-map for EQ K-map for GT D LT = A' B' D + A' C + B' C D EQ = A' B' C' D' + A' B C' D + A B C D + A B' C D’ = (A xnor C) • (B xnor D) GT = B C' D' + A C' + A B D' LT and GT are similar (flip A/C and B/D) 34 Sources: TSR, Katz, Boriello & Vahid Design example: 2x2-bit multiplier A1 A2 B1 B2 P1 P2 P4 P8 block diagram and truth table A2 A1 B2 0 0 0 0 1 1 0 1 0 0 1 1 1 0 0 0 1 1 1 1 0 0 1 1 B1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 P8 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 P4 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 0 P2 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 P1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 4-variable K-map for each of the 4 output functions 35 Sources: TSR, Katz, Boriello & Vahid Design example: 2x2-bit multiplier (cont’d) A2 B2 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 K-map for P8 K-map for P4 B1 B2 A2 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 A1 A1 A2 B2 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 A1 B1 K-map for P2 K-map for P1 B1 B2 A2 0 0 0 0 0 1 1 0 0 1 1 0 0 0 0 0 B1 A1 36 Sources: TSR, Katz, Boriello & Vahid Design example: BCD + 1 I1 I2 I4 I8 O1 O2 O4 O8 block diagram and truth table I8 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 I4 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 I2 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 I1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 O8 0 0 0 0 0 0 0 1 1 0 X X X X X X O4 0 0 0 1 1 1 1 0 0 0 X X X X X X O2 0 1 1 0 0 1 1 0 0 0 X X X X X X O1 1 0 1 0 1 0 1 0 1 0 X X X X X X 4-variable K-map for each of the 4 output functions 37 Sources: TSR, Katz, Boriello & Vahid Design example: BCD + 1 (cont’d) I8 I2 0 0 X 1 0 0 X 0 0 1 X X 0 0 X X O8 O4 I1 I2 I8 0 1 X 0 0 1 X 0 1 0 X X 0 1 X X I4 I4 I8 I2 0 0 X 0 1 1 X 0 0 0 X X 1 1 X X I4 I1 O2 O1 I1 I2 I8 1 1 X 1 0 0 X 0 0 0 X X 1 1 X X I1 I4 38 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Muxes and demuxes Tajana Simunic Rosing 39 Sources: TSR, Katz, Boriello & Vahid Contention: X • Contention: circuit tries to drive output to 1 and 0 – – – – Actual value somewhere in between Could be 0, 1, or in forbidden zone Might change with voltage, temperature, time, noise Often causes excessive power dissipation A=1 Y=X B=0 • Warnings: – Contention usually indicates a bug. – X is used for “don’t care” and contention - look at the context to tell them apart Sources: TSR, Katz, Boriello & Vahid Transmission Gate: Mux/Tristate building block • nMOS pass 1’s poorly • pMOS pass 0’s poorly • Transmission gate is a better switch – passes both 0 and 1 well EN A B • When EN = 1, the switch is ON: – EN = 0 and A is connected to B • When EN = 0, the switch is OFF: EN – A is not connected to B Sources: TSR, Katz, Boriello & Vahid Floating: Z • Floating, high impedance, open, high Z • Floating output might be 0, 1, or somewhere in between – A voltmeter won’t indicate whether a node is floating Tristate Buffer E Y A E 0 0 1 1 A 0 1 0 1 Y Z Z 0 1 Sources: TSR, Katz, Boriello & Vahid Tristate Busses • Floating nodes are used in tristate busses – many different drivers, but only one is active at once processor en1 to bus from bus video en2 to bus Ethernet en3 sharedbus from bus to bus from bus memory en4 to bus from bus Sources: TSR, Katz, Boriello & Vahid 2:1 Multiplexer or Mux • Selects between one of N inputs to connect to output • log2N-bit select input – control input • Example: 2:1 Mux Y S S 0 0 0 0 1 1 1 1 D1 0 0 1 1 0 0 1 1 D0 0 D1 1 D0 0 1 0 1 0 1 0 1 S Y Logic gates D0 D1 00 01 11 10 0 0 1 1 S 0 1 Pass gates S D0 1 Y 0 1 0 1 0 0 1 1 0 Tristates Y D0 D1 0 1 1 0 Y = D 0S + D1S Y D1 D0 S D1 Y Sources: TSR, Katz, Boriello & Vahid Multiplexers • 2:1 mux: • 4:1 mux: • 8:1 mux: Z = A'I0 + AI1 Z = A'B'I0 + A'BI1 + AB'I2 + ABI3 Z = A'B'C'I0 + A'B'CI1 + A'BC'I2 + A'BCI3 + AB'C'I4 + AB'CI5 + ABC'I6 + ABCI7 • In general: Z = 2 n -1(m k=0 kIk) – in minterm shorthand form for a 2n:1 Mux I0 I1 2:1 mux A Z I0 I1 I2 I3 4:1 mux A B Z I0 I1 I2 I3 I4 I5 I6 I7 8:1 mux Z A B C 45 Sources: TSR, Katz, Boriello & Vahid Logic using Multiplexers • Using the mux as a lookup table A 0 0 1 1 B 0 1 0 1 Y 0 0 0 1 Y = AB AB 00 01 10 Y 11 Sources: TSR, Katz, Boriello & Vahid Logic using Multiplexers • Reducing the size of the mux Y = AB A 0 0 1 1 B 0 1 0 1 Y 0 0 0 1 A Y 0 0 1 B A 0 B 1 Y Sources: TSR, Katz, Boriello & Vahid Mux example: Logical function unit C0 0 0 0 0 1 1 1 1 C1 0 0 1 1 0 0 1 1 C2 0 1 0 1 0 1 0 1 Function 1 A+B (A • B)' A xor B A xnor B A•B (A + B)' 0 Comments always 1 logical OR logical NAND logical xor logical xnor logical AND logical NOR always 0 0 1 2 3 8:1 MUX 4 5 6 7 S2 S1 S0 C0 C1 F C2 48 Sources: TSR, Katz, Boriello & Vahid Mux as general-purpose logic • A 2n-1:1 multiplexer can implement any function of n variables – with n-1 variables used as control inputs and – the data inputs tied to the last variable or its complement • Example: F(A,B,C) = AC + BC' + A'B‘C 49 Sources: TSR, Katz, Boriello & Vahid Demux or Decoder • N inputs, 2N outputs • One-hot outputs: only one output HIGH at once 2:4 Decoder A1 A0 A1 0 0 1 1 A0 0 1 0 1 Y3 0 0 0 1 11 10 01 00 Y3 Y2 Y1 Y0 Y2 0 0 1 0 Y1 0 1 0 0 Y0 1 0 0 0 Sources: TSR, Katz, Boriello & Vahid Decoder: logic equations • Decoders/demultiplexers – control inputs (called “selects” (S)) represent binary index of output to which the input is connected – data input usually called “enable” (G) 1:2 Decoder: O0 = G S’ O1 = G S 2:4 Decoder: O0 = G S1’ O1 = G S1’ O2 = G S1 O3 = G S1 S0’ S0 S0’ S0 O0 O1 O2 O3 O4 O5 O6 O7 3:8 Decoder: = G S2’ S1’ S0’ = G S2’ S1’ S0 = G S2’ S1 S0’ = G S2’ S1 S0 = G S2 S1’ S0’ = G S2 S1’ S0 = G S2 S1 S0’ = G S2 S1 S0 51 Sources: TSR, Katz, Boriello & Vahid Decoder Implementation A1 A0 Y3 Y2 Y1 Y0 Sources: TSR, Katz, Boriello & Vahid Logic Using Decoders • OR minterms A B 2:4 Decoder 11 10 01 00 Y = AB + AB = A B Minterm AB AB AB AB “1” 0 1 2 3 3:8 DEC 4 5 6 7 S2 S1 S0 A B A'B'C' A'B'C A'BC' A'BC AB'C' AB'C ABC' ABC C Y Sources: TSR, Katz, Boriello & Vahid Example of demux as general-purpose logic F1 = A'BC'D + A'B'CD + ABCD F2 = ABC'D' + ABC F3 = (A' + B' + C' + D') Enable 0 1 2 3 4 5 6 4:16 7 DEC 8 9 10 11 12 13 14 15 A'B'C'D' A'B'C'D A'B'CD' A'B'CD A'BC'D' A'BC'D A'BCD' A'BCD AB'C'D' AB'C'D AB'CD' AB'CD ABC'D' ABC'D ABCD' ABCD A B C D Sources: TSR, Katz, Boriello & Vahid Another example • F(A,B,C) = M(0,2,4) 55 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Timing and hazards Tajana Simunic Rosing 56 Sources: TSR, Katz, Boriello & Vahid Timing • Delay between input change and output changing • How to build fast circuits? A Y delay A Y Time Sources: TSR, Katz, Boriello & Vahid Propagation & Contamination Delay • Propagation delay: tpd = max delay from input to output • Contamination delay: tcd = min delay from input to output A Y tpd A Y tcd Time Sources: TSR, Katz, Boriello & Vahid Propagation & Contamination Delay • Delay is caused by – Capacitance and resistance in a circuit – Speed of light limitation • Reasons why tpd and tcd may be different: – Different rising and falling delays – Multiple inputs and outputs, some of which are faster than others – Circuits slow down when hot and speed up when cold Sources: TSR, Katz, Boriello & Vahid Critical (Long) & Short Paths Critical (Long) Path: tpd = 2tpd_AND + tpd_OR Short Path: tcd = tcd_AND Critical Path A B n1 n2 C Y D Short Path Sources: TSR, Katz, Boriello & Vahid Glitches or Hazards • Glitch occurs when an input change causes multiple output changes; circuit with a potential for a glitch has a hazard • There are 3 types of hazards: • • • Static-0 : output should be 0 but has a 1 glitch Static-1 : output should be 1 but has a 0 glitch Dynamic: transition 0->1 or 1->0 with a glitch • Example: B = A1 = 00 0 Critical Path 1 n1 Y=1 0 1 What happens if A = 0, C = 1, & Y B falls? A B n2 C=1 1 0 C Short Path Y B AB 00 01 11 10 0 1 0 0 0 1 1 1 1 0 C n2 n1 Y = AB + BC Y Time glitch Sources: TSR, Katz, Boriello & Vahid Fixing a hazard Y AB 00 01 11 10 0 1 0 0 0 1 1 1 1 0 C AC Y = AB + BC + AC A=0 B=1 0 Y=1 C=1 Sources: TSR, Katz, Boriello & Vahid Another example A • F(A,B,C,D)=m(1,3,5,7,8,9,12,13) • Test two single bit input transitions: – 1100 -> 1101 – 1100 -> 0101 A C C’ 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 D B Z D 63 Sources: TSR, Katz, Boriello & Vahid CSE140: Components and Design Techniques for Digital Systems Two and Multilevel logic implementation Tajana Simunic Rosing 64 Sources: TSR, Katz, Boriello & Vahid Multiple-Output Circuits: Priority Circuit • Output asserted corresponds to the most significant TRUE input A3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 A1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Y3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Y2 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 Y1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 Y0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 A3 0 0 0 0 1 A2 0 0 0 1 X A1 0 0 1 X X A0 0 1 X X X Y3 0 0 0 0 1 Y2 0 0 0 1 0 A3 A 2 A1 A0 A3 Y3 A2 Y2 A1 Y1 A0 Y0 PRIORITY CiIRCUIT Y1 0 0 1 0 0 Y0 0 1 0 0 0 Y3 Y2 Y1 Y0 Sources: TSR, Katz, Boriello & Vahid Multiple-Output Circuits • Many circuits have more than one output • Can give each a separate circuit, or can share gates • Ex: F = ab + c’, G = ab + bc Option 1: Separate circuits Option 2: Shared gates 66 Sources: TSR, Katz, Boriello & Vahid Multi-level logic • x=ADF + AEF + BDF + BEF + CDF + CEF + G – reduced sum-of-products form – already simplified – 6 x 3-input AND gates + 1 x 7-input OR gate (that may not even exist!) – 25 wires (19 literals plus 6 internal wires) • x = (A + B + C) (D + E) F + G – factored form – not written as two-level S-o-P – 1 x 3-input OR gate, 2 x 2-input OR gates, 1 x 3-input AND gate – 10 wires (7 literals plus 3 internal wires) A B C X D E F G Sources: TSR, Katz, Boriello & Vahid Multiple-Output Example: BCD to 7-Segment Converter a f b g e c d abcdefg = (a) 1111110 0110000 1101101 (b) a = w’x’y’z’ + w’x’yz’ + w’x’yz + w’xy’z + w’xyz’ + w’xyz + wx’y’z’ + wx’y’z b = w’x’y’z’ + w’x’y’z + w’x’yz’ + w’x’yz + w’xy’z’ + w’xyz + wx’y’z’ + wx’y’z 68 Sources: TSR, Katz, Boriello & Vahid