Lecture3 MOS Transistor

advertisement

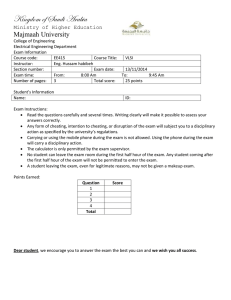

The MOS Transistor Polysilicon Aluminum The Devices: MOS Transistor [Adapted from Rabaey’s Digital Integrated Circuits , ©2002, J. Rabaey et al.] EE415 VLSI Design EE415 VLSI Design The MOS Transistor Switch Model of NMOS Transistor Gate Oxyde Source Gate | V GS| Gate Polysilicon n+ Drain Field-Oxyde Source (of carriers) (SiO2) n+ Drain (of carriers) p+ stopper p-substrate Open (off) (Gate = ‘0’ ) Closed (on) ( Gate = ‘1’) Ron Bulk Contact | V GS| < | V T| CROSS-SECTION of NMOS Transistor EE415 VLSI Design | V GS| > | V T| EE415 VLSI Design Switch Model of PMOS Transistor | V GS| Source (of carriers) CMOS Inverter Gate V DD Drain (of carriers) M2 In Open (off) (Gate = ‘1’ ) Out Closed (on) ( Gate = ‘0’) Out Ron M1 | V GS| > | VDD – | VT | | VDD | V GS| < | VDD – | VT| | Prefered layout with minimal diffusion routing In GND EE415 VLSI Design EE415 VLSI Design 1 MOS transistors Symbols D MOSFET Static Behavior D G VGS =0 G S S NMOS Enhancement NMOS Depletion D Channel D G G B S Mobile electrons S NMOS with Bulk Contact PMOS Enhancement EE415 VLSI Design Depletion Region With drain and source grounded, and VGS = 0, both back-to-back (subsource, sub-drain) junctions have 0V bias and are OFF EE415 VLSI Design Inversion MOSFET Static Behavior Positive voltage applied to the gate (VGS > 0) •The gate and substrate form the plates of a capacitor. •Negative charges accumulate on the substrate side (repels mobile holes) As the VGS increases, the surface under the gate undergoes inversion to ntype material. This is the beginning of a phenomenon called strong inversion. •A depletion region is formed under the gate (like pn junction diode) + VGS S - D G n+ n+ n-channel Depletion Region p-substrate EE415 VLSI Design B The Threshold Voltage Further increases in V GS do not change the width of the depletion layer, but result in more electrons in the thin inversion layer, produc ing a continuous channel from source to drain EE415 VLSI Design The Threshold Voltage The value of V GS where strong inversion occurs is called the Threshold Voltage, VT , and has several components: Where: φ F is the Fermi potential ( ~ -0.3V for ptype substrates •The flat -band voltage, VFB , is the built-in voltage offset across the MOS structure and depends on fixed charge and implanted impurities charge on the oxide-silicon interface Cox is the gate oxide capacitance VSB is the substrate bias voltage •VB represents the voltage drop across the depletion layer at inversion and equals to minus twice the Fermi potential ~(0.6V) VT0 is VT at VSB = 0 •Vox represents the potential drop Note: across the gate oxide VT is positive for NMOS transistors and negative for PMOS VT = V FB + VB + Vox EE415 VLSI Design EE415 VLSI Design 2 Current-Voltage Relations The Body Effect Assume VGS > V T 0.9 •A voltage difference VD S will cause I D to flow from drain to source 0.85 •At a point x along the channel, the voltage is V(x), and the gate-tochannel voltage is VGS - V(x) 0.8 0.75 •For channel to be present from drain to source, VG S - V(x) > VT , i.e. V GS - VD S > VT for channel to exist from drain to source T V (V) 0.7 0.65 0.6 V S V GS DS 0.5 n+ – 0.45 0.4 -2.5 I G 0.55 V (x) n+ L -2 -1.5 -1 -0.5 0 x p-substrate VB S (V) EE415 VLSI Design D D + B EE415 VLSI Design MOS transistor and its bias conditions Linear (triode) Region •When V G S - V D S > V T , the channel exists from drain to source •Transistor behaves like voltage controlled resistor EE415 VLSI Design Current-Voltage Relations Long-Channel Device Saturation Region •When V G S - V D S ≤ V T , the channel is pinched off •Electrons are injected into depletion region and accelerated towards drain by electric field •Transistor behaves like voltage-controlled current source Pinch- off EE415 VLSI Design Current-Voltage Relations Long Channel transistor -4 6 x 10 VGS= 2.5 V 5 VD S = VGS - VT Resistive I D(A) 4 Saturation VGS= 2.0 V 3 Quadratic Relationship VDS = VGS - VT 2 VGS= 1.5 V cut-off 1 0 0 VGS= 1.0 V 0.5 1 1.5 2 2.5 VDS (V) NMOS transistor, 0.25um, Ld = 10um, W/L = 1.5, VDD = 2.5V, VT = 0.4V EE415 VLSI Design EE415 VLSI Design 3 A model for manual analysis EE415 VLSI Design 4