CVT Transients Revisited

advertisement

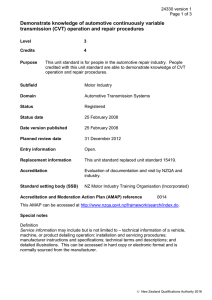

CVT Transients Revisited – Distance, Directional Overcurrent, and Communications-Assisted Tripping Concerns David Costello and Karl Zimmerman Schweitzer Engineering Laboratories, Inc. Copyright © SEL 2012 Basic CVT Structure Line Voltage (EL) C1 C2 Compensating Reactor (LC) ZB Step-Down Transformer (XFMR) 1 Relay Voltage Cross Section of a CVT Primary Terminal Oil Expansion Diaphragm Diaphragm Housing Spring Assembly HV Lead of Capacitor Capacitor Stack Porcelain Insulator Intermediate Voltage Lead LV Lead of Capacitor Bushing Assembly Coverplate Reactance Protective Gap Sight Glass Oil Level Indicator Secondary Terminal Box Transformer Seal Block Assembly Oil Sampling/Drain Valve Reactance Figure Courtesy of Alstom Grid Inc. Physical Construction of CVTs Photo Courtesy of Alstom Grid Inc. 2 CVT Transient Causes Classic Zone 1 Distance Element Overreach CVT Transient Response at Zero Crossing CVT Transient and CT Saturation Cause Directional Element to Misoperate 3 CVT Transient Response When Fault Clears CVT Transient Occurs on Fault Clearing When Unfaulted Voltages Rise CVT Transient During Ringdown After Fault Clears 4 Factors That Affect Transient Response of CVT • Fault point-on-wave • CVT stack capacitance • Ferroresonance suppression • Magnitude and composition burden • Step-down transformer turns ratio and excitation current Voltage (V) CVT Response at Voltage Zero 100 80 60 40 20 0 –20 –40 –60 –80 –100 –2 CVT Transient Ratio Voltage –1 0 1 2 Time (Cycle) 5 3 4 CVT Response at Voltage Peak CVT Transient Voltage (V) 100 80 60 40 20 0 –20 –40 –60 –80 –100 –2 Ratio Voltage –1 0 1 2 Time (Cycle) 3 4 Fundamental Voltage Magnitude (V) High-Capacitance CVT Response Is Better 10 9 8 7 6 5 4 3 2 1 0 Ratio Voltage High-Capacitance CVT Normal-Capacitance CVT 1 1.5 2 2.5 3 Time (Cycle) 6 3.5 4 Ferroresonance Suppression Circuit Relay Voltage L C R AFSC Step-Down XMFR Relay Voltage GAP Lf Rf PFSC R Step-Down XMFR PFSC Is Less Distorted Than AFSC Active Passive Voltage (V) 100 80 60 40 20 0 –20 –40 –60 –80 –100 –2 Ratio –1 0 1 2 Time (Cycle) 7 3 4 Fundamental Voltage Magnitude (V) PFSC Follows Ratio Voltage Better Than AFSC 10 9 8 7 6 5 4 3 2 1 0 Passive CVT Ratio Voltage Active CVT 1 1.5 2 2.5 3 Time (Cycle) 3.5 4 Impact of CVT Burden • ANSI C93.1 defines burden as R&X • Resistive burden does not store energy, provides better transient response • Inductive burden worsens transient response, oscillates at low frequency 8 Impact of CVT Burden • Microprocessor-based relays are lower burden, mostly resistive • Rare case exists where higher burden improves directional element response (i.e., transient is worse, but damped more quickly) Classic Case: Zone 1 2.5 X-ohm 2 Without CVT Transient 1.5 1 With CVT Transient 0.5 0 –0.5 0 0.5 1 R-ohm 9 1.5 2 CG Fault Produces CVT Transient and Zone 1 Overtrip Zone 1 Overreach • Conditions ♦ High SIR ♦ Low-capacitance, AFSC CVT design • Solutions ♦ Change CVT or composition of burden ♦ Reduce reach or delay Zone 1 ♦ Use CVT detection logic 10 Calculate SIR SIR V1FAULT V1PREFAULT I1FAULT I1PREFAULT • Z1LINE Maximum Zone 1 Reach Maximum Zone 1 Reach Setting (pu) PFSC Versus AFSC 1 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 Passive CVT Burden = 100 ohms Active CVT 0 5 10 11 15 SIR 20 25 30 Reduce Overreach Using Resistive Burden Maximum Zone 1 Reach Setting (pu) 1 Resistive Burden 0.95 ANSI Burden 0.9 0.85 0.8 0.75 SIR = 10 Maximum Rated Burden = 200 VA 0 20 40 60 80 % Maximum Rated Burden 100 Improved Zone 1 Setting Strategy: Apply Two “Zone 1s” Zone 1 (ZR1) ZR1_NEW Instantaneous Delayed Relay 12 Apply CVT Detection Logic Distance Calculation Stable CVT Transient Detected 0 Logic Enabled by User Setting Switch-Onto-Fault 1.5 Delay Zone 1 Distance Element Breaker Open Zone 1 Trips Due to CVT Transient Without CVT Detection Logic 13 Zone 1 Impedance Calculation Ohms (sec) 4 MABi 2 Z1P 0 –2 –4 0 1 2 3 4 5 6 Cycles 7 8 9 CVT Detection Blocks Zone 1 Until Transient Subsides 14 10 11 Impact on Directional Elements 3IR2 90° ZR2 ZL2 Z L 2 Angle 3V2 0° Z2R Z2F ZS2 3IS2 Reverse Fault Momentarily Picks Up Forward During CVT Transient 15 Erratic Response of Z2 Directional Element Negative Sequence Dirn Element Calc 1010 Z2Rthrei Ohms (sec) 55 Z2i Z2Fthre i Z2Rthre i 00 Z2i –55 Z2Fthrei 1 2 3 4 5 6 7 8 9 10 11 1 9. 98 8 10 .0 05 10 .0 21 10 .0 38 10 .0 55 10 .0 71 10 .0 88 10 .1 05 10 .1 21 10 .1 38 10 .1 55 –1010 0 9. 97 i RS Time (sec) Result: Permissive Trip Signal Incorrectly Transmitted to Remote Terminal Independent Relay at Substation Captures CVT and Conventional VT CVT CVT CVT Unfaulted A-Phase Voltages Unfaulted B-Phase Voltages Faulted C-Phase Voltages CVT Transient Observed on Faulted and Unfaulted Phase Voltages 16 12 13 14 15 Follow CVT Manufacturer Recommendations “When high speed directional relays are energized from this device it is recommended that the basic burden be power factor corrected to 100% or slightly leading, and that the device be loaded to its full rating of 150 watts, by the addition of parallel resistance if necessary.” – Coupling Capacitor Potential Devices DCB Scheme Overtrips Due to Delayed Transmit of Block Signal 17 CVT Transient Extends Ringdown Conventional VTs CVTs Impact of CVT Transients on Reclosing VA VB VC V1Mag V1Ang VA VB VC 100 0 -100 100 V1Mag 75 50 25 0 V1Ang 100 0 -100 1 2 3 4 5 6 Cy cles 18 7 8 9 10 11 Zone 1 Trips on Reclose Due to V1 Memory 2500 IA IB IC IAMag ICMag VA VB VC IBMag IA IB IC 0 -2500 IAMag IBMag ICMag 2000 1000 0 100 VA VB VC 0 Digitals -100 3 ZAB 0 1 2 3 4 5 1111 6 Cycles 7 8 111 9 10 11 12 COMTRADE Replay With V1 Memory Reset Produces No Trip IA IB IC VA VB VC 2000 IA IB IC 1000 0 -1000 -2000 100 VA VB VC 50 0 -50 Digitals -100 ZAB 0 1 2 3 4 5 6 Cycles 19 7 8 9 10 11 12 Monitor Aging CVTs Debris Scattered Following a Catastrophic CVT Failure Conclusions 20 Larger CVT Transients • Zero-voltage point-on-wave faults • Low CVT capacitance • AFSC • High SIR • Low transformer ratios • High transformer excitation current • Inductive and larger burdens Zone 1 Overreach Solutions • For older relays ♦ Disable Zone 1 ♦ Time-delay Zone 1 ♦ Restrict Zone 1 reach per guidelines based on burden, SIR, and ferroresonance suppression design • For newer relays, enable CVT transient detection logic 21 CVT Transients Affect High-Speed Reclosing • Polarizing memory voltage of distance elements can be corrupted • Simple solutions ♦ Extend open intervals ♦ Set fault detectors above load • Advanced solutions ♦ Adjust the time constant of the memory filter ♦ Substitute zeros into the memory filter when ringdown or terminal-open condition is detected CVT Transients Affect Directional Comparison Schemes • Directional elements are generally secure • For AFSC CVT designs ♦ Adhere to specific burden requirements from CVT manufacturer ♦ Consider using extended carrier coordination delays for DCB schemes ♦ Consider delaying the transmission of permissive signals for POTT schemes 22 CVTs Should Be Monitored • Older and aging CVTs can fail and explode violently • Synchrophasors and automated metering checks ♦ Extend maintenance intervals ♦ More importantly, alarm for discrepancies and improve personnel safety Questions? 23