A Performance Analysis for Interconnections of 3D ICs with

advertisement

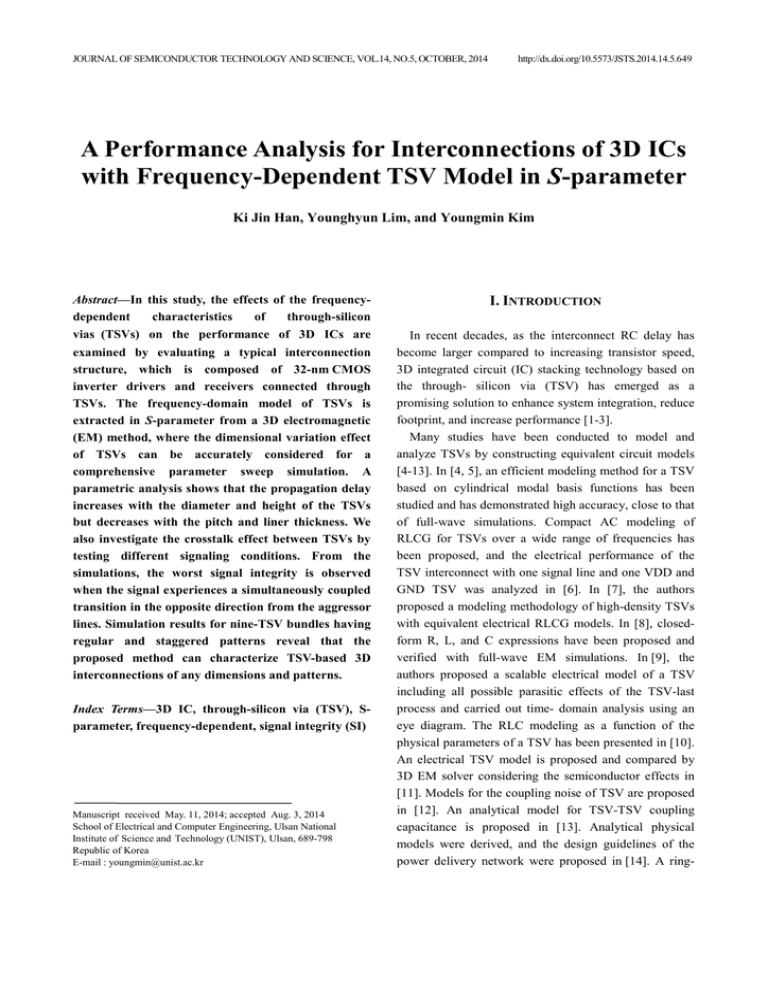

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.5, OCTOBER, 2014 http://dx.doi.org/10.5573/JSTS.2014.14.5.649 A Performance Analysis for Interconnections of 3D ICs with Frequency-Dependent TSV Model in S-parameter Ki Jin Han, Younghyun Lim, and Youngmin Kim Abstract—In this study, the effects of the frequencydependent characteristics of through-silicon I. INTRODUCTION vias (TSVs) on the performance of 3D ICs are In recent decades, as the interconnect RC delay has become larger compared to increasing transistor speed, 3D integrated circuit (IC) stacking technology based on the through- silicon via (TSV) has emerged as a promising solution to enhance system integration, reduce footprint, and increase performance [1-3]. Many studies have been conducted to model and analyze TSVs by constructing equivalent circuit models [4-13]. In [4, 5], an efficient modeling method for a TSV based on cylindrical modal basis functions has been studied and has demonstrated high accuracy, close to that of full-wave simulations. Compact AC modeling of RLCG for TSVs over a wide range of frequencies has been proposed, and the electrical performance of the TSV interconnect with one signal line and one VDD and GND TSV was analyzed in [6]. In [7], the authors proposed a modeling methodology of high-density TSVs with equivalent electrical RLCG models. In [8], closedform R, L, and C expressions have been proposed and verified with full-wave EM simulations. In [9], the authors proposed a scalable electrical model of a TSV including all possible parasitic effects of the TSV-last process and carried out time- domain analysis using an eye diagram. The RLC modeling as a function of the physical parameters of a TSV has been presented in [10]. An electrical TSV model is proposed and compared by 3D EM solver considering the semiconductor effects in [11]. Models for the coupling noise of TSV are proposed in [12]. An analytical model for TSV-TSV coupling capacitance is proposed in [13]. Analytical physical models were derived, and the design guidelines of the power delivery network were proposed in [14]. A ring- examined by evaluating a typical interconnection structure, which is composed of 32-nm CMOS inverter drivers and receivers connected through TSVs. The frequency-domain model of TSVs is extracted in S-parameter from a 3D electromagnetic (EM) method, where the dimensional variation effect of TSVs can be accurately considered for a comprehensive parameter sweep simulation. A parametric analysis shows that the propagation delay increases with the diameter and height of the TSVs but decreases with the pitch and liner thickness. We also investigate the crosstalk effect between TSVs by testing different signaling conditions. From the simulations, the worst signal integrity is observed when the signal experiences a simultaneously coupled transition in the opposite direction from the aggressor lines. Simulation results for nine-TSV bundles having regular and staggered patterns reveal that the proposed method can characterize TSV-based 3D interconnections of any dimensions and patterns. Index Terms—3D IC, through-silicon via (TSV), Sparameter, frequency-dependent, signal integrity (SI) Manuscript received May. 11, 2014; accepted Aug. 3, 2014 School of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology (UNIST), Ulsan, 689-798 Republic of Korea E-mail : youngmin@unist.ac.kr 650 KI JIN HAN et al : A PERFORMANCE ANALYSIS FOR INTERCONNECTIONS OF 3D ICS WITH FREQUENCY-DEPENDENT TSV … oscillator (RO)-based digital signal transmission scheme was exploited to verify the feasibility of the 3D IC and to assess the impact of the TSV on the performance in [15, 16]. All previous works have focused on TSV parasitic modeling and analysis with varying frequency. However, a significant amount of research has not been conducted for the signal integrity between the multi-lines of TSV signals and the related timing analysis under different neighboring TSV conditions with an understanding of the various TSV placements and structural variations. In this study, the frequency-dependent impact of the TSVs on the performance of 3D ICs is evaluated. To obtain a frequency-dependent model of TSV structures, a 3D electro- magnetic (EM) method [4] is used. At first, three lines of the transmission structure with 32-nm inverter drivers and receivers connected by TSVs are evaluated to analyze the comprehensive TSV structural impact on the signal line. The interconnection consists of one signal line (or victim) at the center and two neighbor lines (or aggressors) at both sides. To investigate the crosstalk or capacitance coupling effect between TSVs on the performance, the aggressor can make a transition opposite to the signal line, in the same direction as the signal line, or be quiet at VDD or GND. Then, we expand the analysis for the 3D nature of the interconnection with a nine-TSV bundle, where a victim line is at the center and the other eight TSVs surround the victim line. The effects are estimated through a transient analysis with SPICE [17]. We sweep the TSV parameters, such as the diameter, height, oxide liner thickness, size of landing pads, and pitch of TSVs, to evaluate the impact of the TSV dimensions on the signal performance and signal integrity. We also analyze the performance impact on the signal line for a wide range of frequencies by changing the rise time of the signal. Statistical eye analysis with a pseudo-random source is conducted to evaluate the impact on the high-speed signal integrity. In addition, SPICE AC simulations with compact TSV model [6] and S-parameter model are compared and investigated to validate the efficiency of the proposed S- parameterbased approach. Section II explains the EM modeling methodology used for S-parameter extraction of the TSVs of a 3D IC. Section III shows the simulation setups and results, followed by the conclusion in Section IV. II. EM MODELING AND S-PARAMETER EXTRACTION Frequency-dependent S-parameters of the TSV structures are extracted from a 3D EM modeling method based on the mixed-potential integral equation [4]. The procedure of the modeling method is illustrated Fig. 1 where the electrical characteristics of the original TSV structure is divided into current in conductors, charge on surfaces, and polarization current in oxide liner regions. To capture the charge and current density distributions in TSVs, the EM method employs cylindrical modal basis functions, which are used when converting electric-field integral equation (EFIE) and scalar potential integral equation (SPIE) into equivalent circuit equations. Because spatial discretization is avoided with the modal basis functions, the method produces a reduced impedance and admittance matrices shown in Fig. 1 and a simplified equivalent circuit [5], compared to the conventional partial element equivalent circuit (PEEC) method [18]. The reduction of modeling time and memory of the proposed EM method enables the efficient generation of a large number of parametric models. The Fig. 1. Procedure of the EM-based TSV modeling method. JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.5, OCTOBER, 2014 Port 2 Port 4 Port 6 Port 3 Port 5 aggressor 651 victim aggressor pitch D H Liner thickness Port 1 Fig. 2. Three-TSV structure with six ports for frequencydependent S-parameter generation. Fig. 4. Three lines of interconnections with drivers and receivers; note that vertical cylinders are TSVs. Table 1. Nominal structural and material parameters of TSV [1] Fig. 3. Frequency-dependent transmission coefficients of the three TSVs in Fig. 2; the left plot is for D = 5µm, and the right plot is for D = 10 µm. circuit model obtained from the EM method can be converted to a multi-port network parameter. In this paper, we apply the EM modeling method to a three-TSV structure shown in Fig. 2 and generate sixport S-parameter data (and nine TSVs with 18-port data as shown in Fig. 8 as well) with varying parameters, as explained in Table 1. For all cases, the considered TSVs are signal lines, whose return paths are assumed to be at the ideal ground at infinity. By assuming the ideal ground in this paper, we can focus on the performance of the signal TSVs only. The frequency-dependent transmission coefficients (|S12|, |S34|) of the three TSVs for eight cases sampled from Table 1 are plotted in Fig. 3. All responses in Fig. 3 follow a typical characteristic of TSV interconnects, where low-frequency and high-frequency behaviors exhibit slow-wave and quasi-TEM modes, respectively. III. SIMULATION RESULTS 1. Three Lines of Interconnection Three lines of interconnection with 32-nm CMOS [19, Parameters Nominal Values Parameter sweep TSV diameter (D) 5 [µm] 5, 10, 20, 50, 100 TSV height (H) 50 [µm] 5, 10, 20, 30, 100 TSV pitch (P) 15 [µm] 10, 20, 30, 50, 100 Liner thickness (Tox) 0.1 [µm] 0.05, 0.1, 0.2, 0.5, 1 Pad diameter 7.8 [µm] D + (2.8) * (D/5) Pad thickness 0.1 [µm] - Silicon conductivity 10 [S/m] - Resistivity of TSV 1.68e-8 [Ω·m] - 20] drivers and receivers, as shown in the Fig. 4, are exploited to analyze the impact of TSV parameters on the propagation delay. We use high-performance predictive technology models (HP PTM) for drivers and receivers. NMOS width of 5 um and 1.5x larger PMOS width are used to match both rising and falling transitions for generating the drivers and receivers. In Fig. 4, the center TSV is the victim and the two neighboring TSVs are aggressors. In this paper, we simulate the transient response of the center TSV line with respect to the following four aggressor conditions: (a) The aggressors are quiet and steadily connected to VDD (‘VDD’). (b) The aggressors are steadily connected to GND (‘GND’). (c) The aggressors make a simultaneous transition in the opposite direction to the center line signal (‘opposite’). (d) The aggressors make a simultaneous transition in the same direction to the center line signal (‘same’). Fig. 5 represents the normalized delay change for each TSV parameter variation, such as diameter (D), height (H), pitch (P), and liner thickness, respectively. The delay data are normalized to the propagation delay of the nominal parameter value (i.e., Table 1) when neighboring TSVs are quiet at GND. As expected, the signal line experiences the greatest impact when neighboring aggressors are simultaneously driving in the opposite direction and the smallest impact (or better) 652 KI JIN HAN et al : A PERFORMANCE ANALYSIS FOR INTERCONNECTIONS OF 3D ICS WITH FREQUENCY-DEPENDENT TSV … (a) (b) (c) (d) Fig. 5. Normalized delay vs. TSV parameter sweep (a) diameter, (b) height, (c) pitch, (d) liner thickness. when they are in the same direction. For example, with the nominal TSV parameters (i.e., D = 5 µm) shown in Fig. 5(a), there is up to a 24% delay increase in the case of opposite aggressors and a 21% delay decrease (speed up) in the case when the transition is in the same direction as the center signal lines, compared to the quiet neighboring lines (i.e., GND or VDD). As shown in Fig. 5, the propagation delay increases as the diameter and the height of the TSV increase because of the growth of oxide capacitance and inductance of the TSV. On the other hand, the signal propagation becomes faster as the pitch of the TSVs becomes larger because of the reduced coupling effects in opposite and quite conditions as shown in Fig. 5(c). Note that, as expected, the delay becomes lager as the pitch increases at ‘same’ aggressor condition due to the reduction of the crosstalk effect [21]. The delay also becomes smaller as the liner thickness increases because of the lower capacitive coupling with neighboring TSVs and the reduction of the oxide capacitance, as shown in Fig. 5(d). It is worth mentioning that the TSV height and liner thickness variation have the largest impact, and the changes in the landing pad size have the smallest impact. The normalized delay variation as the frequency of input signal increases (or rise time decreases) is shown in Fig. 6. The delay data are normalized to the result of the 1.5-ns rise time (or 212 MHz) at a GND neighboring condition. It is quite interesting that the delay sensitivity Fig. 6. Normalized delay vs. input frequency of three TSV lines (frequency = 1/π·Trise). to the frequency becomes lower as the frequency increases. For example, there is a 15% increase in speed from 100 MHz to 200 MHz, but only a 5% improvement from 1 GHz to 2 GHz at the worst crosstalk condition (i.e., ‘opposite’ in Fig. 6). The normalized delay by the analytical TSV model [6] is represented by the dashed line for comparison. Over the entire frequency range, there exists up to 10% difference between data at ‘opposite’ case from two methods. The discrepancy is attributed to the absence of the signal-to-ground capacitance in the analytical model. Since the Sparameter model is applicable to more general cases, the proposed S-parameter -based SPICE AC simulation is efficient for understanding the frequency-dependent JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.5, OCTOBER, 2014 Fig. 7. Statistical eye diagram of the center TSV line with 5Gb/s pseudo-random data when (left) two neighboring TSVs are quite and (right) two neighboring TSVs are agitated. (Vertical eye-opening for (left) is 456 mV and (right) is 440 mV). characteristics of 3D ICs with TSVs. Statistical eye analysis with a 5-Gb/s pseudo-random source and a 100-ps rise time without any random jitter is conducted to evaluate the impact on the high-speed signal integrity, as shown in Fig. 7. As shown in the figure, the vertical and horizontal eye-openings are reduced by 4% and 3.6%, respectively, when both the neighboring TSV lines affect the center signal line. 2. Signals in the TSV Bundle TSVs are vertical interconnects used to transmit signals between the bottom tier and top tier by penetrating the substrate. Thus, the conventional three lines of interconnect structure with a center victim line and two neighboring aggressors near the victim used for a traditional 2D planar circuit as shown in Fig. 4 is not suitable for the vertical TSV interconnection because it is 3D structure. Therefore, in this section, we exploit a nine-TSV bundle, as shown in Fig. 8(a), to analyze the impact of TSV parameter variation on the signal propagation for various frequencies. In Fig. 8, there are nine vertical TSV lines placed in a Manhattan-like grid of the same pitch (i.e., square pattern). The frequencydependent S-parameter elements are shown in Fig. 8(b) for various TSV diameters from 2 µm to 30 µm. As shown in the figure, the maximum degradation (i.e., insertion loss) occurs at the center TSV line (in black) because of the higher coupling interaction between neighboring TSV lines, and TSVs at the four corners (in red) exhibit the minimum degradation as the frequency increases. We apply a victim driver and a receiver at the center TSV and aggressors at eight surrounding TSV lines to measure the worst impact of the signal propagation in four different aggressor conditions (i.e., (a) 653 (b) Fig. 8. (a) Structure of the square pattern of nine-TSV bundle used in this section showing the GND aggressor condition, (b) Frequency-dependent transmission coefficients of the nine TSVs with decreasing TSV diameter (D); the black lines represent the center TSV, the blue lines represent the left, right, bottom, and top center TSVs, and the red lines represent the four edge TSVs. opposite, GND, VDD, and same). Delay impacts are measured by sweeping three TSV structural parameters, such as the diameter, height, and center-to-center pitch, as shown in Table 1. The simulation results shown in Fig. 9 are normalized to the delay of the nominal parameter values (D = 5 µm, H = 50 µm, P = 15 µm, and Tox = 0.1 µm). In the opposite aggressor condition, as expected, delay degradation is worst, and the impact is greater than those of the three-line case shown in Fig. 5. For example, at the worst crosstalk condition, the signal slows down by a factor of 1.2 with a three-line structure but by a factor of up to 1.5 slower with a nine-TSV bundle when compared to the quiet neighboring case when D = 5 µm. The height makes the most significant impact on the signal propagation because the coupling effects become larger as the height of the TSV increases. For example, when we decrease the height to half of the nominal value (H = 25 µm), we can achieve an increase of speed by 30% in the signal propagation. To analyze the impact by the center-to-center TSV pitch, we sweep the pitch from 10 µm to 500 µm. As shown in Fig. 9(c), we can observe a significant impact as the pitch changes. At the nominal value of the pitch, the same neighboring condition shows up to a 40% positive coupling effect (i.e., faster), and opposite aggressors result in more than 40% negative (i.e., slower) crosstalk. The impact reduces dramatically as the pitch increases. For example, when the pitch becomes twice the nominal value (P = 30 µm), the coupling effect is reduced up to 6%, and there are very small neighboring effects when the pitch is wider than 654 KI JIN HAN et al : A PERFORMANCE ANALYSIS FOR INTERCONNECTIONS OF 3D ICS WITH FREQUENCY-DEPENDENT TSV … (a) (b) (c) Fig. 9. Normalized delay vs. TSV parameter sweep of nine TSV lines (a) diameter, (b) height, (c) pitch. (a) (b) Fig. 10. Two different TSV bundle patterns (a) square, (b) staggered; the arrows indicate identical pitch between TSVs. (a) (b) Fig. 11. Delay comparison between the square and staggered patterns of TSV lines (a) in frequency (the black line and dots are for the opposite aggressor condition, and the reds are for the same aggressor condition. They are normalized to the quiet aggressor case at 212 MHz), (b) with increasing pitch to opposite aggressors (normalized to nominal values with GND neighbors. The discrepancy numbers are shown). 100 µm. There are several choices for TSV placement for 3D IC interconnections [22-24]. One method is to place TSVs along an array-like grid (i.e., square pattern), as shown in Fig. 10(a), and the other method is to place TSVs in a staggered pattern by shifting each row a half pitch to maintain equal distances between all surrounding TSVs, as shown in the Fig. 10(b). To assess the performance impact on the center TSV between these two placements, we generate frequency-dependent Sparameters for the two TSV bundles. The transient simulation results are shown in Fig. 11(a). For the entire range of frequencies, though the staggered pattern TSV has a slightly smaller impact on the signal, the two structures show very similar results on the center TSV line. Comparison of the delay impact on the center TSV between these two patterns as pitch increases is shown in Fig. 11(b). The maximum discrepancy exists when the pitch is at a minimum (i.e., 10 µm), and the difference decreases as the pitch becomes wider. At ‘same’ crosstalk condition, the discrepancy between two patterns increases up to 5% at the minimum pitch. This result clearly indicates that the proposed S-parameter-based approach is versatile and applicable to any number of TSVs and any placement. The statistical eye analysis results of the nine TSVs are shown in Fig. 12. The vertical eye-opening is reduced up to 6.5%, which is 20 mV smaller than that of the threeline case when all eight surrounding TSVs affect the signal transmission of the center TSV. JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.5, OCTOBER, 2014 Fig. 12. Statistical eye diagram of the center TSV line in the nine-TSV bundle with 5-Gb/s pseudo-random data when (left) eight neighboring TSVs are quiet and (right) eight neighboring TSVs are agitated. (Vertical eye-opening for (left) is 449 mV and (right) is 420 mV). Fig. 13. Normalized delay of the center line vs. input frequency in the nine TSV bundle (frequency = 1/π·Trise). Table 2. Normalized delay by ±10% parameter variations for different aggressor conditions with nine TSVs diameter (D) height (H) liner (Tox) aggressor condition nominal opposite 1.39 1.33 1.45 1.32 1.46 1.44 1.35 GND 1 0.95 1.04 0.95 1.04 1.03 0.97 VDD 0.99 0.95 1.04 0.95 1.04 1.03 0.96 same 0.65 0.64 0.67 0.63 0.67 0.66 -10% +10% -10% +10% -10% +10% 0.64 The comparison between our proposed approach and the analytical model [6] is shown in Fig. 13. Common characteristics observed from all cases are (1) the capacitive effect is dominant at low frequencies and (2) the inductive effect becomes severe at high frequencies. On the other hand, a significant discrepancy between the two approaches in the lower frequency range (e.g., ≤ 200 MHz) is worth mentioning. The discrepancy originates from a simplification in which the analytical model neglects the self-admittances of TSVs. Without the self-admittances, the analytical model overestimates or underestimates the delay, depending on the excitation 655 conditions. The S-parameters used in our approach include the self-admittances that contribute to the delay. Since the self-admittances are defined with respect to the ideal ground, the estimated delay in our analysis can be considered as a baseline when predicting a selfadmittance oriented delay in real structures. In the opposite excitation case in Fig. 13, for example, the analytical model overestimates the delay that is dominated by the oxide capacitance (Cox) only, but the delay from our S-parameter model is reduced due to the additional charge relaxation through the self-admittances. The comparison shows the strength of the proposed approach that easily captures realistic delay effects, whereas the analytical model needs to be modified for every different excitation condition. To quantify the impact on the signal propagation at the center TSV line with parameter variations, transient analyses with varying ±10% parameter values are conducted. The results normalized to the delay of the nominal case are summarized in Table 2. The +10% height variation results in the maximum delay change from that of the nominal value. A 10% smaller diameter and height provide approximately a 5% increase in speed in the worst crosstalk condition. A 10% thicker oxide liner results in approximately a 3% delay improvement. IV. CONCLUSION In this study, we analyze the frequency-dependent impact of the TSVs on the performance of 3D ICs. Supported by a recently developed EM modeling method, numerous transient analyses combined with S-parameter TSV models are conducted to quantify the impact of TSV parameters on the performance of a signaling structure. Simulation results show that the signal propagation is influenced by the TSV parameter variation, the crosstalk (coupling) condition, and the signal frequency (or rise time). Because the TSV model used in this study is more versatile than simple circuit models, the presented data can provide more realistic design guidelines. Analysis of the nine-TSV bundle provides close-to-real 3D effects of the TSV in the transmission of the signal. The proposed S-parameter-based approach can be applied to any TSV patterns (e.g., regular or custom) and structural parameters (e.g., diameter, height, and pitch). 656 KI JIN HAN et al : A PERFORMANCE ANALYSIS FOR INTERCONNECTIONS OF 3D ICS WITH FREQUENCY-DEPENDENT TSV … REFERENCES [1] ITRS 2012, [online], http://public.itrs.net. [2] S.Q. Gu, P. Marchal, M. Facchini, F. Wang, M. Suh, D. Lisk, and M. Nowak, “Stackable memory of 3D chip integration for mobile applications”, IEEE IEDM, pp. 1-4, 2008. [3] D. H. Kim, S. Mukhopadhyay, and S. K. Lim, “TSV-aware interconnect length and power prediction for 3D stacked ICs”, IEEE Interconnect Technology Conference, IITC, pp. 26-28, 2009. [4] K. J. Han, M. Swaminathan, and T. Bandyopadhyay, “Electromagnetic Modeling of Through-Silicon Via (TSV) Interconnections Using Cylindri- cal Modal Basis Functions”, IEEE Transactions on Advanced Packaging, vol. 33, no. 4, pp. 804-817, 2010. [5] K. J. Han and M. Swaminathan, “Inductance and resistance calculations in three-dimensional packaging using cylindrical conduction-mode basis functions”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 28, no. 6, pp. 846-859, 2009. [6] X. Chuan, L. Hong, R. Suaya, and K. Banerjee, “Compact AC Modeling and Performance Analysis of Through-Silicon Vias in 3-D ICs”, IEEE Transactions on Electron Devices, vol. 57, no. 12, pp. 3405-3417, 2010. [7] C. Bermond, L. Cadix, A. Farcy, T. Lacrevaz, P. Leduc, and B. Flechet, “High Frequency Characterization and Modeling of High Density TSV in 3D Integrated Circuits”, IEEE Workshop on Signal Propagation on Interconnects, pp. 1-4, 2009. [8] I. Savidis and E. G. Friedman, “Closed-form expressions of 3-D via resistance, inductance, and capacitance”, IEEE Transactions on Electron Devices, vol. 56, no. 9, pp. 1873-1881, 2009. [9] J. Kim et al., “High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV)”, IEEE Transactions on Components, packaging, and manufacturing technology, vol. 1, no. 2, pp. 181-195, 2011. [10] G. Katti, et al., “Electrical modeling and characterization of through silicon via for threedimensional ICs”, IEEE Transactions on Electron Devices, vol. 57, no. 1, pp. 256-262, 2010. [11] T. Bandyopadhyay, R. Chatterjee, D. Chung, M. Swaminathan, and R. Tummala, “Electrical modeling of through silicon and package vias”, IEEE International Conference on 3D System Integration, pp. 1-8, 2009. [12] J. Cho, et al. “Modeling and analysis of throughsilicon via (TSV) noise coupling and suppression using a guard ring”, IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 1, no. 2, pp. 220-233, 2011. [13] D. H. Kim, S. Mukhopadhyay, and S. K. Lim, “Fast and accurate analytical modeling of throughsilicon-via capacitive coupling”, IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 1, no. 2, pp. 168-180, 2011. [14] G. Huang, M. Bakir, A. Naeemi, H. CHen, and J. D. Meindl, “Power Delivery for 3D Chip Stacks: Physical Modeling and Design Implica- tion”, IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 2, no. 5, pp. 852859, May 2012. [15] V. D. Plas et al., “Design Issues and Considerations for Low-Cost 3-D TSV IC Technology”, IEEE JSSC, vol. 46, no. 1, pp. 293-307, 2011. [16] H. V. Nguyen, M. Ryu, and Y. Kim, “TSV Geometrical Variations and Optimization Metric with Repeaters for 3D IC”, IEICE Trans. on Electronics, vol. E95-C, no. 12, pp. 1864-1871, 2012. [17] HSPICE, ver. H-2013-03, [online], http://www. synopsys.com/ [18] A. E. Ruehli, “Equivalent circuit models for three dimensional multi-conductor systems”, IEEE TMTT, vol. MTT-22, pp. 216–221, 1974. [19] W. Zhao and Y. Cao, “New generation of Predictive Technology Model for sub-45nm early design exploration” IEEE Transactions on Electron Devices, vol. 53, no. 11, pp. 2816-2823, 2006. [20] 32 nm HP PTM models, [online], http://ptm.asu.edu/ [21] T. Sakurai, “Closed-form expressions for interconnection delay, coupling, and crosstalk in VLSIs”, IEEE Transactions on Electron Devices, vol. 40, no.1, pp. 118-124, 1993. [22] S.W. Yoon et al., “3D TSV Micro Cu Column Chip-to-Substrate/ChipAssembly/Packaging Technology”, In proceedings of the International JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.5, OCTOBER, 2014 Wafer Level Packaging Conference, Nov. 2012. [23] D. H. Kim, Y.-K. Wu, R. O. Topaloglu, and S. K. Lim, “Enabling 3D Integration Through Optimal Topography”, IEEE International Workshop on Design for Manufacturability and Yield, 2010. [24] M. Jung, X. Liu, S. K. Sitaraman, D. Z Pan, and S. K. Lim, “Full-Chip Through-Silicon-Via Interfacial Crack Analysis and Optimization for 3D IC”, IEEE ICCAD, pp. 563-570, Nov. 2011. Ki Jin Han received the B.S. (summa cum laude) and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1998 and 2000, respectively, and the Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2009. He was with the System Research and Development Laboratory, LG Precision, Yongin, Korea, from 2000 to 2005. From 2009 to 2011, he was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, as a Post-Doctoral Researcher. Currently, he is with the School of ECE, Ulsan National Institute of Science and Technology, Ulsan, Korea, as an Assistant Professor. His current research interests include computational electromagnetics, signal/power integrity for high-speed digital design, microwave circuits, antennas, and electromagnetic modeling of electronic packaging and interconnections. Dr. Han is a recipient of the Samsung Scholarship for graduate study in 2005. 657 Younghyun Lim is currently an undergraduate student in electrical engineering at Ulsan National Institute of Science of Technology (UNIST). He is expecting to receive the B.S. in 2015. His current research interests include analog and mixedsignal integrated circuit designs and modeling. Youngmin Kim received the B.S. degree in electrical engineering from the Yonsei University, Seoul, Korea, in 1999, and the M.S. and Ph.D. degrees in electrical engineering from the university of Michigan, Ann Arbor, in 2003 and 2007, respectively. He has held a senior engineer position in the Qualcomm, San Diego, CA. He is currently an Assistant Professor in the school of electrical engineering and computer engineering at the Ulsan National Institute of Science and Technology (UNIST), Ulsan, South Korea. His research interests include variability-aware design methodologies, design for manufacturability, and design and technology co-optimization methodologies, and lowpower and 3D IC designs.