Chapter7. FET Biasing

advertisement

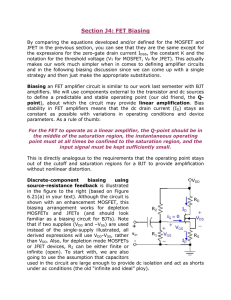

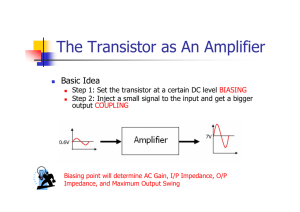

Chapter7. FET Biasing JFET Biasing configurations Fixed biasing Self biasing & Common Gate Voltage divider MOSFET Biasing configurations Depletion-type Enhancement-type FET Biasing JFET: Fixed Biasing Example 7.1: As shown in the figure, it is the fixed biasing configuration of n-channel JFET. Determine: VGSQ , IDQ , VDS , VD , VG and VS . Solution: Mathematical approach VGSQ = - VGG = - 2V. FET Biasing 2 I DQ VGS 2V 10mA1 I DSS 1 VP 8V 2 = 5.625mA VDS = VDD – ID RD = 16V - (5.625mA) (2k) = 4.75V VD = VDS = 4.75V VG = VGS = - 2V VS = 0V FET Biasing Graphical approach First, according to Shockley’s equation, we can sketch out the transfer curve. It is known that IDSS= 10mA and VP= -8V. Three points are sufficient to plot the curve. (0 , IDSS) (0, 10mA) (VP, 0) (-8V, 0) (VP /2, IDSS/4) (-4V, 2.5mA) FET Biasing The fixed level of VGS has been superimposed as a vertical line at VGS= -VGG = -2V. The intersection of the two curves is the solution to the configuration, referred to as the quiescent or operating point. By drawing a horizontal line from the Q-point to the vertical ID axis, we get IDQ = 5.6mA FET Biasing The remaining work is almost the same as previous approach: VDS = VDD – ID RD = 16V - (5.6mA) (2k) = 4.8V VD = VDS = 4.8V VG = VGS = - 2V VS = 0V FET Biasing Figure: Example 7.1, FET fixed biasing FET Biasing Figure: Example 7.1, Graphical approach FET Biasing JFET: Self-Bias Example 7.2: As shown in the figure, it is the self biasing configuration of n-channel JFET. This network needs only one dc supply. Determine: VGSQ , IDQ , VDS , VD , VG and VS . Solution: This time, we only use graphical approach. FET Biasing For dc analysis, all the capacitors are replaced with open circuit. Note that IG = 0mA . From the dc circuit, we get VGS = – ID RS It is a straight line through the origin. The other point is (-4V, 4mA). So the load line is plotted through the two points. FET Biasing Then, according to Shockley’s equation, we can sketch out the transfer curve. It is known that IDSS= 8mA and VP= -6V. Three points are sufficient to plot the curve. (0 , IDSS) (0, 8mA) (VP, 0) (-6V, 0) (VP /2, IDSS/4) (-3V, 2mA) FET Biasing The intersection of the two curves is the Qpoint. So we get IDQ = 2.6mA VGSQ = -2.6V VDS = VDD – ID (RD+RS) = 20V - (2.6mA) (1k+ 3.3k) = 8.82V FET Biasing VS = ID RS = (2.6mA) (1k) = 2.6V VG = 0V VD = VDS +VS = 8.82V+ 2.6V = 11.42V or VD = VDD – ID RD = 20V- (2.6mA) (3.3k) = 11.42V FET Biasing Figure: Example 7.2, FET self-bias FET Biasing Figure: Example 7.2, Q-point of self-bias FET Biasing JFET: Common Gate Example 7.4: As shown in the figure, it is the common gate configuration of n-channel JFET. Determine: VGSQ , IDQ , VDS , VD , VG and VS . Solution: This network is corresponding to commonbase network of BJT. FET Biasing According to Shockley’s equation, we can sketch out the transfer curve. It is known that IDSS= 12mA and VP= -6V. Three points are sufficient to plot the curve. (0 , IDSS) (0, 12mA) (VP, 0) (-6V, 0) (VP /2, IDSS/4) (-3V, 3mA) FET Biasing From the dc circuit, we get VGS = – ID RS = – ID (680 ) It is a straight line through the origin. The other point is (-4.08V, 6mA). So the load line is plotted through the two points. So from the Q-point, we get IDQ 3.8mA VGSQ -2.6V FET Biasing VG = 0V VD = VDD – ID RD = 12V- 3.8mA 1.5k = 6.3V VS = ID RS = 3.8mA 680 = 2.58V VDS = VD – VS = 6.3V-2.58V = 3.72V FET Biasing Figure: Example 7.4, Common gate configuration FET Biasing Figure: Example 7.4, Transfer curve & load line FET Biasing JFET: Voltage Divider Example 7.5: As shown in the figure, it is the voltage divider configuration of n-channel JFET. Determine: VGSQ , IDQ , VD , VS , VDS , and VDG . Solution: This network is the same as voltage divider network of BJT. FET Biasing According to Shockley’s equation, we can sketch out the transfer curve. It is known that IDSS= 8mA and VP= -4V. Three points are sufficient to plot the curve. (0 , IDSS) (0, 8mA) (VP, 0) (-4V, 0) (VP /2, IDSS/4) (-2V, 2mA) FET Biasing For dc analysis, all the capacitors are replaced with open circuit. Note that IG = 0mA . So we get R2 270k VG VDD 16V R1 R2 2.1M 270k = 1.82V Also it’s obvious that VGS = VG – ID RS = 1.82V- ID (1.5k) FET Biasing So the load line is plotted through the two points. (1.82V, 0mA) & (0V, 1.21mA) Then from the Q-point, we get IDQ 2.4mA VGSQ -1.8V VD = VDD – ID RD = 16V- 2.4mA 2.4k = 10.24V FET Biasing VS = ID RS = 2.4mA 1.5k = 3.6V VDS = VDD – ID (RD+RS) = 16V- 2.4mA ( 2.4k + 1.5k ) = 6.64V Or VDS = VD – VS = 10.24V-3.6V = 6.64V VDG = VD – VG = 10.24V-1.82V = 8.42V FET Biasing Figure: Example 7.5, Voltage divider configuration FET Biasing Figure: Example 7.5, Transfer curve & load line FET Biasing Depletion-Type MOSFET Example 7.7: As shown in the figure, it is the n-channel depletion-type MOSFET configuration. Determine: VGSQ , IDQ , and VDS . Solution: For the n-channel depletion-type MOSFET, VGS can be positive and ID can exceed IDSS. FET Biasing According to Shockley’s equation, we can sketch out the transfer curve. It is known that IDSS= 6mA and VP= -3V. Three points are sufficient to plot the curve while VGS<0. (0 , IDSS) (0, 6mA) (VP, 0) (-3V, 0) (VP /2, IDSS/4) (-1.5V, 1.5mA) FET Biasing when VGS > 0, letting VGS =1V, and according to Shockley’s equation, we get 2 VGS I D I DSS 1 VP 2 1V 6mA1 3V = 10.67mA So the transfer curve has been sketched out. FET Biasing For dc analysis, all the capacitors are replaced with open circuit. Note that IG = 0mA . So we get R2 11M VG VDD 18V R1 R2 110 M 11M = 1.5V Also it’s obvious that VGS = VG – ID RS = 1.5V- ID (750) FET Biasing So the load line is plotted through the two points. (1.5V, 0mA) & (0V, 2mA) Then from the Q-point, we get IDQ 3.1mA VGSQ -0.8V VDS = VDD – ID (RD + RS) = 18V- (2.4mA) (2.4k+750) 10.1V FET Biasing Figure: Example 7.7, depletion-type MOSFET configuration FET Biasing Figure: Example 7.7, Transfer curve & load line FET Biasing Enhancement-Type MOSFET Example 7.11 : As shown in the figure, it is the n-channel enhancement-type MOSFET feedback biasing configuration. Determine: VGSQ and IDQ. Solution: Due to the existence of VGS(Th), we need four points to obtain the transfer curve. FET Biasing The ID is defined by ID = k (VGS – VT)2 Solving for k, we obtain I D ( on ) 6mA k 2 (VGS ( on ) VGS (Th ) ) (8V 3V ) 2 = 0.2410-3 A/V2 Then, Letting VGS = 6V, we get ID = 0.2410-3 (VGS – VT)2 = 0.2410-3 (6V – 3V)2 = 2.16mA FET Biasing Also, Letting VGS = 10V, we get ID = 0.2410-3 (VGS – VT)2 = 0.2410-3 (10V – 3V)2 = 11.76mA So four points are sufficient to plot the curve. VGS(Th) (3V, 0mA) (VGS(on) , ID(on) ) (8V, 6mA) (6V, 2.16mA) (10V, 11.76mA) FET Biasing From the dc circuit, we get VGS = VDD – ID RD = 12V– ID (2k) So the load line is plotted through the two points. (0V, 6mA) and (12V, 0mA) So from the Q-point, we get IDQ 2.75mA VGSQ 6.4V FET Biasing Figure: Example 7.11, enhancement-type MOSFET configuration FET Biasing Figure: Example 7.11, Transfer curve & load line FET Biasing Summary of Chapter 7 JFET Biasing configurations Fixed biasing Self biasing & Common Gate Voltage divider MOSFET Biasing configurations Depletion-type: voltage divider Enhancement-type: feedback biasing FET Biasing