FET Biasing

advertisement

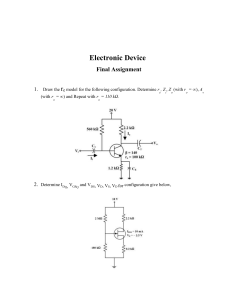

Section J4: FET Biasing By comparing the equations developed and/or defined for the MOSFET and JFET in the previous section, you can see that they are the same except for the expressions for the zero-gate drain current IDSS, the constant K and the notation for the threshold voltage (VT for MOSFET, VP for JFET). This actually makes our work much simpler when in comes to defining amplifier circuits and in the following biasing discussion since we can come up with a single strategy and then just make the appropriate substitutions. Biasing an FET amplifier circuit is similar to our work last semester with BJT amplifiers. We will use components external to the transistor and dc sources to define a predictable and stable operating point (our old friend, the Qpoint), about which the circuit may provide linear amplification. Bias stability in FET amplifiers means that the dc drain current (ID) stays as constant as possible with variations in operating conditions and device parameters. As a rule of thumb: For the FET to operate as a linear amplifier, the Q-point should be in the middle of the saturation region, the instantaneous operating point must at all times be confined to the saturation region, and the input signal must be kept sufficiently small. This is directly analogous to the requirements that the operating point stays out of the cutoff and saturation regions for a BJT to provide amplification without nonlinear distortion. Discrete-component biasing using source-resistance feedback is illustrated in the figure to the right (based on Figure 6.21(a) in your text). Although the circuit is shown with an enhancement MOSFET, this biasing arrangement works for depletion MOSFETs and JFETs (and should look familiar as a biasing circuit for BJTs). Note that if two supplies (VDD and –VSS) are used instead of the single-supply illustrated, all derived expressions will use VDD-VSS, rather than VDD. Also, for depletion mode MOSFETs or JFET devices, R2 can be either finite or infinite (open). To start with, we are also going to use the assumption that capacitors used in the circuit are large enough to provide dc isolation and act as shorts under ac conditions (the old “infinite and ideal” ploy). Using the same procedure as the BJT derivations, we can define single bias circuit for all FET amplifier configurations. This is presented as a Thevenin equivalent circuit (Figure 6.22 in your text) for the single-source circuit above, with components: RG = R1 || R2 = VGG R1 R2 R1 + R2 V R = DD 1 R1 + R2 . (Equation 6.24) Looking at the figure above, we have three unknown variables to define for biasing (IDQ, VGSQ and VDSQ), so we need three dc equations. The first is found from the definition of the drain current in the saturation region, while the other two are the KVL equations obtained from the Thevenin equivalent circuit. I DQ = K (VGSQ − VT ) (1 + λV DSQ ) ≅ K (VGSQ 2 I DQ ⎛ VGSQ = I DSS ⎜⎜1 − VP ⎝ 2 ⎛ VGSQ − VT ) = KVT ⎜⎜1 − VT ⎝ 2 2 ⎞ ⎛ V ⎟ (1 + λV DSQ ) ≅ I DSS ⎜1 − GSQ ⎟ ⎜ VP ⎠ ⎝ ⎞ ⎟ ⎟ ⎠ 2 ⎞ ⎛ V ⎟ = I DSS ⎜1 − GSQ ⎟ ⎜ VT ⎠ ⎝ ⎞ ⎟ ⎟ ⎠ 2 ( MOSFET ) 2 ( JFET ) The final expressions for IDQ given above (a modified version of Equation 6.27) are obtained by making the assumption |λVDSQ|<<1 and are of the same form for the MOSFET and JFET devices. The only difference is the notation used for the threshold voltage and the expression for IDSS. The second equation may be obtained by writing the KVL equation around the gate-source loop in the figure above: VGG = VGSQ + I DQ R S , (Equation 6.25) and the third equation is the KVL equation of the drain-source loop (with IG=0, so that IS=ID as shown in the figure): V DD = I DQ R D + V DSQ + I DQ R S = V DSQ + I DQ ( R D + R S ) . (Equation 6.26) Finally, it is often useful in design to use the transconductance parameter. Using the approximation, |λVDSQ|<<1, gm may be expressed for the MOSFET by: gm = − 2 I DSS VT ⎛ VGSQ ⎜1 − ⎜ VT ⎝ ⎞ ⎟. ⎟ ⎠ (Equation 6.28) Equation 6.28 also holds for the JFET if VT is replaced by VP. Recall the criteria mentioned earlier for FET amplifier biasing – to obtain linear amplification, we want the transistor to operate in the active (also called saturation or pinch-off) region. Many times, however, we are going to have to begin the design process with this assumption. This is fine, this is good, but always go back and check this assumption at the end of the design process!! Your author also notes that it is often not necessary to put the Q-point in the center of the ac load line as we did for BJTs. If the FET amplifier is used as a preamplifier to take advantage of its high input impedance, the input signal is so small that we do not have to design for maximum swing. As usual, this is pretty much just for information, the problem or circumstances will determine Q-point placement.