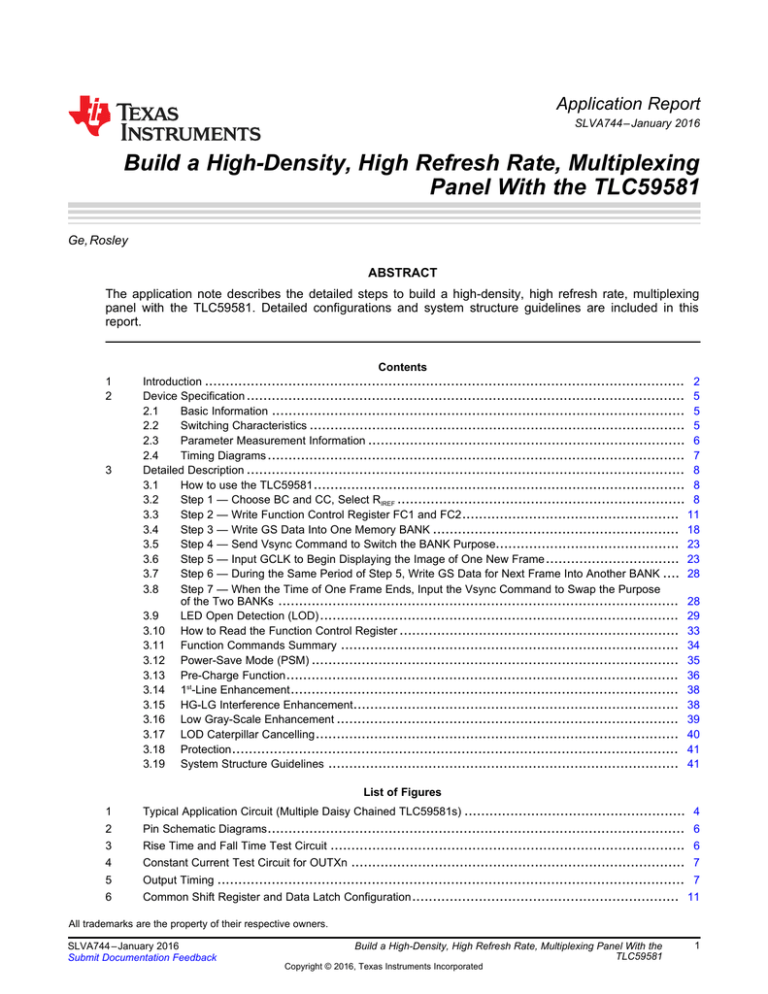

Build a High-Density, High Refresh Rate

advertisement