Characteristics of a 1200V PT IGBT With Trench Gate and

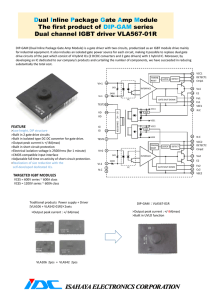

advertisement

Characteristics of a 1200V PT IGBT With Trench Gate and Local Life Time Control Eric R. Motto*, John F. Donlon*, H. Takahashi**, M. Tabata**, H. Iwamoto* * Powerex Inc., Youngwood, Pennsylvania, USA ** Mitsubishi Electric, Power Device Division, Fukuoka, Japan Abstract - A new 1200V IGBT with a VCE(sat) 2 of 1.9V at 125C and 140A/cm has been developed using a trench gate PT (punch-through) structure and local life time control. Compared to state-ofthe-art third generation planar devices, this device represents a 30% improvement of on-state losses at almost twice the current density. This paper will describe the structure and characteristics of this new IGBT. I. INTRODUCTION The IGBT (Insulated Gate Bipolar Transistor) has become the power semiconductor device of choice for a wide range of industrial power conversion applications. Its popularity is the direct result of technology advances that have produced devices with rugged switching characteristics, low losses, and simple gate drive. Devices with VCES ratings of 1200V are of particular interest due to their widespread use with AC mains voltages of 360VAC to 480VAC. This paper will present a new 1200V IGBT device that has been optimized using the latest processing technologies to substantially reduce losses in these applications. II. 1200V TRENCH GATE IGBT - KEY TECHNOLOGIES Historically, improvements in the performance of IGBTs have been attained primarily through finer surface patterns and shallow diffusion processing technologies. Unfortunately, this approach has reached the point of severely diminishing returns due in part to the so-called "parasitic JFET" resistance between adjacent cells in the MOSFET portion of the device and in part to the VF of the diode structure in the bipolar portion of the device. The key to producing the significantly improved 1200V IGBT described in this paper was the simultaneous optimization of these critical areas. The following subsections will present the FIGURE 1: STRUCTURE OF THE TRENCH GATE IGBT CHIP structure and process technologies employed to reduce the losses of this new IGBT. A. Trench gate structure In order to reduce the RDS(on) of the MOSFET portion of the IGBT, a trench gate structure has been adopted. This structure, illustrated in Figure 1, has already been adopted to reduce the on-state voltage drop of low voltage MOSFETS and IGBT devices rated at up to 600V [6] [7] [10]. This paper reports the result of adopting this technology to 1200V IGBT devices. A schematic cross section comparison of a conventional IGBT cell to the trench gate cell is shown in Figure 2. The trench structure differs from the conventional planar structure in that the gate oxide and conductive polysilicon gate electrode are formed in a deep narrow trench below the chip surface. When voltage is applied to the gate, a channel forms along the vertical wall of the trench perpendicular to the surface of the chip. This is very different from the conventional planar structure where the channel forms under the gate parallel to the surface of the chip. The vertical channel of the trench structure provides two key advantages. First, the vertical channel requires less chip area permitting a substantial increase in cell density. The increased cell Emitter Gate n+ RChannel RJFET p Rn- n- trench structure. In particular, the non-uniform current density in the "JFET" region of the planar structure can result in SOA aberrations at high current densities. In the case of the new 1200V PT IGBT the more uniform current flow of the trench structure, combined with the greater cell density, has resulted in an increase in the controllable current density from about 800A/cm2 in third generation planar devices to more than 1400A/cm2. B. PT chip structure n+ p+ Collector Conventional Planar Gate IGBT Cell Emitter Gate n+ p RChannel To optimize the VF of the diode structure within the bipolar portion of the IGBT, a PT (Punch Through) rather than NPT (Non Punch Through), chip structure was selected. The n+ buffer layer of the PT structure essentially makes the diode a PIN type. The advantages of this structure for optimizing the VF and recovery characteristics of power diodes are well known. In particular, the resistivity and thickness of the n- drift layer can be optimized for low VF without the severe problems of high off-state leakage current and the need to process extremely thin silicon wafers that plague the NPT IGBT structure. n- C. Local Lifetime Control Rnn+ p+ Region of local lifetime control Collector New 1200V Trench Gate IGBT Cell FIGURE 2: UNIT CELL COMPARISON TABLE I: REDUCTION OF VCE(SAT) Components of VCE(sat) Reduction Technique RChannel Adopt trench gate surface structure to increase cell density and channel width per unit area Eliminate by adopting trench gate structure Utilize local lifetime control to increase on-state carrier concentration RJFET Rn- density produces a greater channel width per unit chip area resulting in a reduction in the Rchannel portion of the IGBT’s on-state voltage drop. The second advantage of the trench structure is complete elimination of the "JFET" resistance (RJFET) which results from the constriction of current flow in the region between adjacent cells in the planar structure. Additionally, there are some less obvious secondary advantages of the In order to reduce the VF of the pin diode structure within the bipolar portion of the IGBT, it is necessary to optimize the doping profile, geometry and carrier lifetime of the n- drift region and n+ buffer layer. The carrier lifetime in the n+ buffer layer must be reduced to increase the rate of recombination and speed up turn-off switching. In the third generation planar IGBT, the lifetime was reduced using a uniform lifetime killing process employing electron irradiation. Unfortunately, the uniform lifetime control also reduces the carrier lifetime in the n- drift region causing an increase in VCE(sat). To avoid this problem, a local lifetime control process utilizing heavy ion irradiation was developed. This process allows the lifetime killing to be applied to the n+ buffer layer, as shown in Figure 2, without reducing the lifetime of the n- drift layer. The longer lifetime in the drift layer produces a greater carrier concentration during conduction which in turn reduces the Rn- component of VCE(sat). D. The RTC (Real Time Control) Circuit Industrial power electronic equipment is often required to survive catastrophic events such as miswiring and shorted loads. In these applications, the IGBT is required to survive low impedance short circuits long enough for protection circuits to respond. III. ELECTRICAL CHARACTERISTICS The most outstanding characteristic of the new 1200V IGBT is its extremely low VCE(sat). This characteristic is obtained as a collective result of the new processing technologies described in Section II and outlined in Table I. A saturation voltage characteristic curve comparing a third generation planar IGBT with the new trench gate device is shown in Figure 4. The third generation planar device in this comparison is a 100A 1200V device with a nominal current density at rated current of 95A/cm2. The trench gate device is also rated 100A, 1200V and has a nominal current density of 140A/cm2. This curve shows that the trench gate device has a VCE(sat) 0.9V lower than the third generation planar device at 1.4 times greater current density. Figure 5 shows the inductive load turn-on and turn-off switching waveforms for the new trench gate IGBT at Tj=125C. The local lifetime Main Emitter Area Current Mirror Emitter Gate C Trench Gate IGBT 1200V Trench Gate 1200V Third Generation Planar G RTC Circuit E FIGURE 3: TRENCH GATE IGBT CHIP AND RTC The trench gate IGBT, by itself, has very limited short circuit withstanding capability due to its extremely high short circuit saturation current. To reduce this current, the trench IGBT chip is fabricated with a current mirror emitter. The current mirror is connected to an RTC (Real Time Control) circuit to provide active clamping of short circuit current. The RTC and trench gate IGBT chip are shown in Figure 3. The RTC circuit is activated by the current from the current mirror emitter on the trench IGBT chip. During a short circuit, the high current from the current mirror activates the RTC which reduces the gate driving voltage on the IGBT, thereby clamping the short circuit current to a safe level. The RTC circuit restores the short withstanding capability to more than 10µs, comparable to the third generation planar devices. FIGURE 4: (VCE(SAT)) CHARACTERISTIC FOR 100A IGBT CHIP control gives low turn-off losses with a desirable reduction in dv/dt compared to the third generation planar device. With equivalent series gate resistance, the turn on of the trench gate device is faster than the third generation planar device due to a reduction in reverse transfer capacitance. A substantial reduction in turn-on losses was made possible by a new free wheel diode which will be described in section V. Table II compares the basic electrical characteristics of a 100A, 1200V trench gate and a third generation planar device. TABLE II: CHARACTERISTICS OF 100A, 1200V TRENCH GATE VERSUS THIRD GENERATION Characteristic Symbol Conditions U-Series Trench Gate Collector cutoff current Gate-emitter threshold voltage Gate leakage current Collector to emitter saturation voltage Input Capacitance Output Capacitance Reverse Transfer Capacitance Thermal Resistance IC ICES VGE(th) VCE=1200V, VGE=0V IC=10mA, VCE=10V 1.0mA Max 6V 1.0mA Max 6V IGES VCE(sat) VGE=20V, VCE=0V VGE=15V Tj=25C IC=100A Tj=125C 0.5µA Max 2.9V 2.85V 15nF 5nF 3nF 20µA Max 1.8V 1.9V 36nF 0.99nF 0.93nF 0.19C/W 0.25C/W Cies Coes Cres VCE=10V, VGE=0V RTH(j-c) IGBT Turn-Off Switching Inductive Load, TJ=125C IC:20A/div, VCE:200V/div t:200ns/div described in Section II permits less silicon area to be used for a given current rating. The resulting smaller chip is less expensive to manufacture and can be adapted to smaller, lower cost packages. Figure 6 shows the trade-off relationship between various technologies considering a 100A 1200V IGBT. From Figure 6 it is obvious that the trench gate PT IGBT with local lifetime control has the best EOFF versus VCE(sat) trade-off characteristic. Table III gives a performance 4.0 VCE A 3.5 C 3.0 Turn-On Switching Inductive Load, TJ=125C IC:20A/div, VCE:200V/div t:200ns/div VCE VCE(sat) (V) Tj=125C IC=100A B D Powerex/Mitsubishi U-Series 2.5 E Powerex/Mitsubishi H-Series 2.0 New Powerex/Mitsubishi Trench gate IGBT 1.5 1.0 0 5 10 15 20 25 30 ESW(off) (mJ/pulse) Tj=125C, IC=100A, VCC=600V 2 IC A: Conventional NPT, tN-=250µm, JC=100A/cm 2 B: PT planar gate uniform lifetime control, JC=100A/cm 2 C: Thin Drift Region NPT, tN-=150µm, JC=100A/cm 2 D: PT planar gate, uniform lifetime control, JC=75A/cm 2 E: PT trench gate, local lifetime control, JC=140A/cm FIGURE 6: EOFF VERSUS VCE(SAT) TRADE-OFF FIGURE 5: 1200V TRENCH GATE IGBT SWITCHING WAVEFORMS IV. PERFORMANCE ANALYSIS The low VCE(sat) of the trench gate IGBT combined with the improved turn-off current density comparison for the different device technologies shown in Figure 6. The low losses of the trench gate chip result in a reduced junction to case temperature rise compared to other technologies even though its smaller chip has a higher thermal impedance. The lower losses also allow use of smaller heat sinks which helps to reduce the cost and size of finished equipment. The combination of reduced chip size and reduced losses Parameter TABLE III: IGBT PERFORMANCE COMPARISON Third Third Thin drift Generation Generation region H-Series U-Series NPT VCE(sat) (V) Tj=125C 2 @ Current Density (A/cm ) Switching Loss - Eon+EOFF Total Sinusoidal Output Inverter Loss fPWM=5KHz Total Sinusoidal Output Inverter Loss fPWM=15KHz Thermal Impedance RTH(j-c) Temperature Rise - TJ-C fPWM=5KHz Temperature Rise - TJ-C fPWM=15KHz IGBT Chip size Trench Gate 2.3 75 1.0 1.0 2.85 95 0.95 0.94 3.4 95 0.89 1.0 1.9 140 0.84 0.62 1.0 0.89 0.89 0.59 1.0 1.0 1.0 1.0 1.25 1.08 1.03 0.8 1.25 1.15 1.03 0.8 1.5 0.93 0.88 0.6 make the 1200V, PT, trench gate IGBT an effective technology for high power applications. V. MODULE DEVELOPMENT To obtain maximum performance from the new trench gate chips an optimized module package and a new free wheel diode with improved fast but soft recovery characteristics were developed. The new IGBT module package is based on the "U-Series" package developed by Powerex/Mitsubishi in 1996 [11]. Figure 7 shows a cross section drawing of the new package. The key innovation is its insert molded case in which the power electrodes are molded into the sides as opposed to inserted after the case is molded. The main electrodes are then connected directly to the power chips using large diameter aluminum bonding wires rather than solder. A photograph of a dual (half bridge) module is shown in figure 8. One of the main objectives in the design of the new package was a reduction in internal inductance. The most significant improvement was made possible by molding wide electrodes into the sides of the case to form parallel plate structures having considerably less Main Terminal Electrode Silicone Gel Cover Insert Molded Case Al Bond Wires Cu Base Plate Power Chips AlN Substrate FIGURE 7: U-PACKAGE CROSS SECTION FIGURE 8: TRENCH GATE IGBT MODULE inductance than conventional electrodes. In addition, the strain relieving "S" bends that were needed in the electrodes of conventional modules are not needed in the U-Series package because the aluminum bond wires perform the strain relieving function. Elimination of these "S" bends helped to further reduce the electrode inductance. Overall, as a result of these inductance reducing features, the new package has about one third the inductance of conventional modules. Another advantage of the new package is a significant improvement in manufacturability. The number of soldering steps required is reduced from two to one. With the conventional module, the chip to substrate and substrate to base plate soldering is done first with high temperature solder. Then, the case is attached to the base plate and a second low temperature soldering step is used to connect the power electrodes. In the new module, the second step is eliminated because the connections to the power electrodes are made using the aluminum bond wires. The soldering temperature of the chip and substrate attachment can be reduced helping to minimize the effects of the mismatched coefficients of expansion between the base plate and the AlN DBC substrate. The result is a reduction in thermal stress during manufacturing, improved baseplate flatness, and increased reliability. Another advantage of the new package is a substantially smaller ceramic substrate. The ceramic area needed for soldering the power electrodes in the conventional module is not required. As a result, higher performance AlN ceramic can be cost effectively utilized to minimize the thermal impedance of the new package. VI. CONCLUSION A new 1200V Trench gate IGBT with local lifetime control has been presented. The electrical characteristics include low VCE(sat), low switching losses, and robust switching SOA. 10µs short circuit withstanding capability was achieved by implementing an active current clamping circuit. A performance analysis was presented to show the advantages of this device for industrial power conversion applications. VII. REFERENCES [1] G. Majumdar, et al. "A New Generation High Speed Low Loss IGBT Module", ISPSD, May 1992 [2] J Yamashita, et al. "A Study on the Short Circuit Destruction of IGBTs" , ISPSD, May 1993 [3] Powerex "IGBTMOD and IntellimodTM Application and Technical Data Book" PUB# 9DB-100, March 1998 [4] Majumdar, et. al., "Enhancing SOAs of IGBT Modules for Hard Switching Applications", PCIM 1990 [5] Yamada, et. al., "Next Generation Power Module", ISPSD 1994 [6] M. Harada, et. al., "600v Trench IGBT in Comparison with Planar IGBT", ISPSD May 31, 1994 [7] T. Iida, et. al., "Low VCE(sat) IGBT Module by New Structure - Trench", PCIM Europe June 28, 1994 [8] E. Motto, et. al., "Evaluating the Dynamic Performance of High Current IGBT Modules" PCIM/PQ 1994 [9] E. Motto "Protecting High Current IGBT Modules From Over Current and Short Circuits" HFPC Conference May ,1995 [10] Eric R. Motto, et. al. “New Process Technologies Improve IGBT Module Efficiency” IEEE IAS Conference October 1995 [11] Eric R. Motto, “A New Low Inductance IGBT Module Package” PCIM Conference September 1996