Laboratory 3 NAND, NOR and XOR functions properties

advertisement

DSAS Laboratory

no 3

Laboratory 3

NAND, NOR and XOR

functions properties

3.1 Laboratory work goals

•

•

•

Enumeration of NAND, NOR and XOR functions properties

Presentation of NAND, NOR and XOR modules

Realisation of circuits with gates in order to practically test

some of the properties of NAND, NOR and XOR functions.

3.2 Theoretical considerations

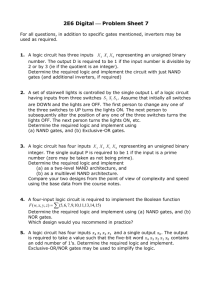

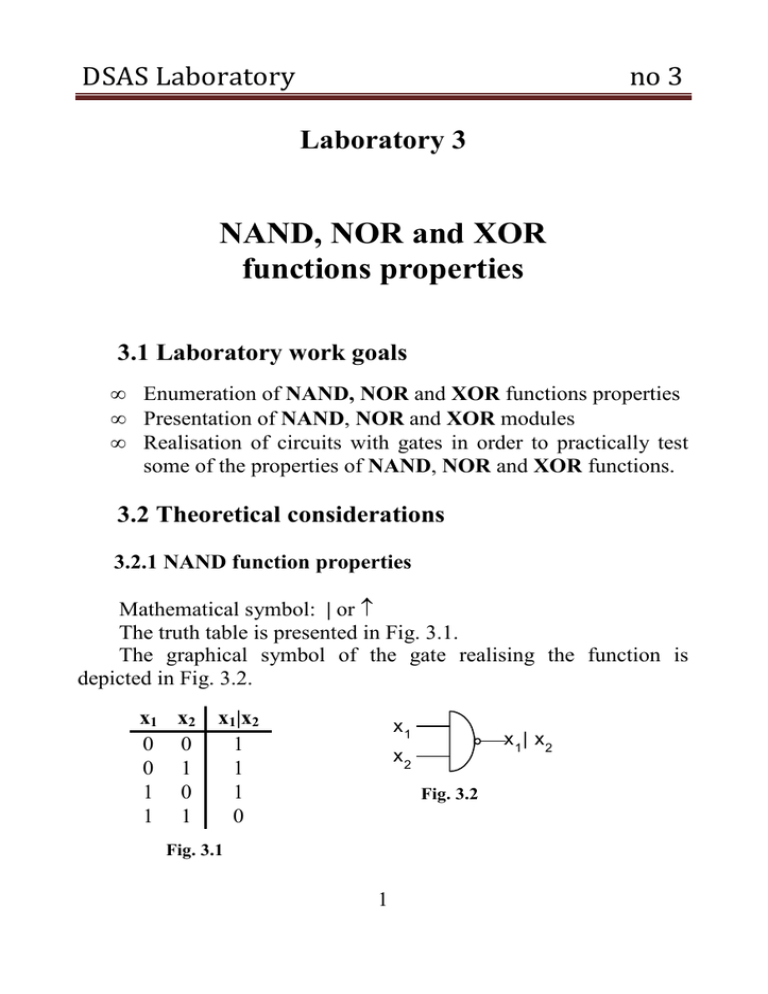

3.2.1 NAND function properties

Mathematical symbol: | or ↑

The truth table is presented in Fig. 3.1.

The graphical symbol of the gate realising the function is

depicted in Fig. 3.2.

x1 x2

0 0

0 1

1 0

1 1

x1|x2

1

1

1

0

x1

x 1| x2

x2

Fig. 3.2

Fig. 3.1

1

DSAS Laboratory

no 3

P1) x1|x2|…|xn= x1 ⋅ x 2 ⋅ ... ⋅ x n = x1 + x 2 + ... + x n

P2) Commutativity of NAND:

x1|x2=x2|x1

P3) NAND function is not associative, that is

(x1|x2)|x3 ≠ x1|(x2|x3)

P4) NAND function is pseudo-associative, that is

x1|x2|x3= ( x1 | x 2 ) |x3 = x1| ( x 2 | x 3 )

P5) 0 is aggressive with respect to NAND meaning

0|x1|x2|…|xn=1

P6) The pseudo-neutrality of 1 with respect to NAND

a) 1|x1|x2|…|xn=x1|x2|…|xn

b) 1|x1 = x1

P7) The pseudo-idempotency of NAND

a)

b)

x|x|…|x|y1|y2|…|ym= x|y1|y2|…|ym

x|x|…|x= x

P8) The pseudo-distributivity of NAND with respect to NOR:

x|(y↓z)=( x ↓y)|( x ↓z)

P9) The first absorption law for NAND:

x|(x|y)=x| y

P10) The second absorption law for NAND:

(x|y)|( x |y)=y

P11) Any switching function can be represented using only

NAND operators (The NAND operator forms a base for

switching functions representation).

2

DSAS Laboratory

no 3

3.2.2 NOR function properties

Mathematical symbol: ↓

The truth table is presented in Fig. 3.3.

The graphical symbol of the gate realising the function is

depicted in Fig. 3.4.

x1 x2 x1↓↓x2

0 0

1

0 1

0

1 0

0

1 1

0

x1

x1 x 2

x2

Fig. 3.4

Fig. 3.3

P1) x1↓x2↓…↓xn= x1 + x 2 + ... + x n = x1 ⋅ x 2 ⋅ ... ⋅ x n

P2) NOR is commutative:

x1↓x2=x2↓x1

P3) NOR function is not associative, meaning

(x1↓x2)↓x3 ≠ x1↓(x2↓x3)

P4) NOR function is pseudo-associative, meaning

x1↓x2↓x3= (x1 ↓ x 2 ) ↓ x 3 = x1 ↓ (x 2 ↓ x 3 )

P5) 1 is aggressive with respect to NOR meaning

1↓x1↓x2↓…↓xn=0

P6) The pseudo-neutrality of 0 with respect to NOR

a) 0↓x1↓x2↓…↓xn=x1↓x2↓…↓xn

b) 0↓x1 = x1

P7) The pseudo-idempotency of NOR

a) x↓x↓…↓x↓y1↓y2↓…↓ym= x↓y1↓y2↓…↓ym

b) x↓x↓…↓x= x

3

DSAS Laboratory

no 3

P8) The pseudo-distributivity of NOR with respect to NAND:

x↓(y|z)=( x |y)↓( x |z)

P9) The first absorption law for NOR:

x↓(x↓y)=x↓ y

P10) The second absorption law for NOR:

(x↓y)↓( x ↓y)=y

P11) Any switching function can be represented using only

NOR operators (the NOR operator forms a base for switching

functions representation).

3.2.3 XOR function properties

Mathematical symbol: ⊕

The truth table is presented in Fig. 3.5.

The graphical symbol of the gate realising the function is

depicted in Fig. 3.6.

x1 x2 x1⊕x2

0 0

0

0 1

1

1 0

1

1 1

0

x1

x1 + x2

x2

Fig. 3.6

Fig. 3.5

P1) x1 ⊕ x 2 = x1 x 2 + x1x 2 (see paragraph 3.5.7)

P2) XOR operator is commutative:

x1⊕x2=x2⊕x1

P3) XOR operator is associative:

x1⊕(x2⊕x3)= (x1⊕x2)⊕

⊕x3

P4) 0 is neutral with respect to XOR:

4

DSAS Laboratory

no 3

0⊕

⊕x=x⊕

⊕0=x

P5) 1 is pseudo-neutral with respect to XOR:

1⊕

⊕x=x⊕

⊕1= x

Remark! The P4 and P5 properties justify the name of

commanded inverter, sometimes used to designate the XOR

operator, as it can be seen in Fig. 3.7.

Fig. 3.7

P6) The symmetrical of x with respect to XOR is x itself,

meaning x⊕

⊕x=0.

0

x ⊕ x ⊕ ... ⊕ x =

x

n times

P7)

if

n = 2k

if n = 2k + 1

P8) x ⊕ y = x ⊕ y = x ⊕ y

P9) Distributivity of AND with respect to XOR:

x•(y⊕z)=(x•y)⊕(x•z)

P10) Any switching function can be implemented using only

XOR, AND operators and the constant 1 (XOR, AND, 1 form a

base for switching functions representation).

5

DSAS Laboratory

no 3

3.3 Presentation of modules comprising NAND,

NOR and XOR logic gates

The modules used during the lab activities comprise XOR

(7486), NOR (7402) and NAND (74LS00) logic circuits.

Details about each module and pin assignment are presented in

Appendix 4 and [20], [21].

The 74LS00 module (Fig. 3.8) is an integrated circuit that

contains 4 NAND 2 gates, implementing the NAND function with 2

inputs.

Y=A|B= A ⋅ B = A + B

The 74LS10 module (Fig. 3.9) is an integrated circuit that

contains 3 NAND 3 gates, implementing the NAND function with 3

inputs.

Y=A|B|C = A ⋅ B ⋅ C = A + B + C

The 74LS20 module (Fig. 3.10) is an integrated circuit that

contains 2 NAND 4 gates, and implements the NAND function with

4 inputs.

Y=A|B|C|D = A ⋅ B ⋅ C ⋅ D = A + B + C + D

The 74LS02 module (Fig. 3.11) is an integrated circuit

containing 4 independent NOR 2 gates, and implements the NOR

function with 2 inputs.

Y=A ↓ B= A + B = A ⋅ B

The 7486 module (Fig. 3.12) is an integrated circuit containing 4

independent XOR 2 gates, implementing the XOR function with 2

inputs.

6

DSAS Laboratory

no 3

Y=A ⊕ B= AB + AB

GND

7

5

14

13

12

2A

11

4Y

2B

10

3A

2Y

9

3B

GND

8

7

4B

3Y

7

8

6

1Y

6

9

3B

4A

5

10

3A

1B

4

11

5

3Y

Vcc

3

4

4B

1A

2

12

2Y

3Y

Fig. 3.10 -7420

1

3

4A

3B

8

6

8

3Y

3A

9

2Y

4Y

10

9

3C

4B

11

3B

2B

NC

4A

12

2A

Vcc

13

3

3C

NC

14

2

1Y

4

1

1Y

10

13

1B

1A

GND

1B

11

14

2

4Y

1

Vcc

2B

1C

Fig. 3.9 -7410

1Y

2A

1A

12

7

GND

Vcc

13

8

6

Fig. 3.8 -7400

14

9

3Y

GND

2Y

7

10

3B

2Y

2C

6

11

5

3A

2B

2B

5

4

4Y

4

12

2A

2A

3

3

4B

1B

2

13

1Y

1B

1A

1

14

2

4A

1

Vcc

1A

Fig. 3.11-7402

Fig. 3.12-7486

3.4 Lab activity progress

There will be implemented circuits comprising gates in order to

verify some of the XOR, NOR and NAND functions properties.

Example:

Distributivity of conjunction with respect to XOR:

∀ x,y,z∈

∈{0,1} x•(y⊕z)=(x•y)⊕(x•z)

E1= x•(y⊕z)

7

DSAS Laboratory

no 3

E2=(x•y)⊕(x•z)

In order to verify these properties a XOR SN7486 module and an

AND SN74LS08 module will be used. The test diagram is depicted

in Fig. 3.13. Both expressions must be implemented and then for

each possible combination of x, y and z the output voltage must be

measured for each expression circuit.

x

U2A

U1A

y

1

1

3

3

z

E1

2

2

74LS08

74LS86A

U2B

4

6

U1B

5

4

74LS08

6 E2

5

U2C

9

74LS86A

8

10

74LS08

Fig. 3.13

3.5 Proposed problems

1. Implement a circuit containing logic gates that verifies

property P3 of NAND function.

2. Implement a circuit containing logic gates that verifies

property P4 of NAND function. The NAND 3 function will

be implemented using the 7410 module.

3. Implement a circuit containing logic gates that verifies

property P8 of NAND function.

4. Implement a circuit containing logic gates that verifies

properties P2, P5, P6 and P7 of NAND function.

8

DSAS Laboratory

no 3

5. Implement a circuit containing logic gates that verifies

properties P9 and P10 of NAND function.

6. Implement a circuit containing logic gates that verifies

property P4 of NOR function. The NOR 3 function will be

implemented using 7432 and 7404 modules.

7. Implement a circuit containing logic gates that verifies

properties P2, P5, P6 and P7 of NOR function.

8. Implement a circuit containing logic gates that verifies

property P8 of NOR function.

9. Implement a circuit containing logic gates that verifies

properties P9 and P10 of NOR function.

10. Implement a circuit containing logic gates that verifies

properties P4, P5, P6 and P9 of XOR function.

11. Implement a circuit containing logic gates that verifies

properties P2, P3 and P8 of XOR function.

Note! The test results will be recorded for each problem in a

table.

9