EEE 524: Communication Transceiver System and Circuits Design

advertisement

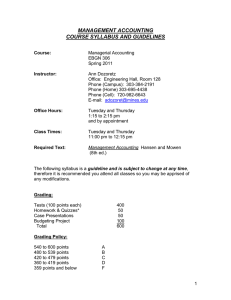

**Disclaimer** This syllabus is to be used as a guideline only. The information provided is a summary of topics to be covered in the class. Information contained in this document such as assignments, grading scales, due dates, office hours, required books and materials may be from a previous semester and are subject to change. Please refer to your instructor for the most recent version of the syllabus. EEE 524: Communication Transceiver System and Circuits Design Spring, 2013 Jennifer Kitchen Meeting Time & Place: TTH 1:30 - 2:45pm, ECG – G 347 Instructor: Prof. Jennifer Kitchen Office: Goldwater Center (GWC) 314 Phone: 480-965-1857 Office hours: TTH 3:15-4:30pm and by appointment Email: kitchen.jennifer@asu.edu TA: Jianxiong Sun; Email: Sun.Jianxiong@asu.edu Lab Hours: T: 10am-1pm & 3pm-7pm, TH: 10am-1pm, F: 12noon-6pm Required Textbook: None – Detailed handouts will be posted prior to class. Reference Book 1 provides significantly more detailed information than that covered within this course. Ref Book 1: Kevin McClaning, “Wireless Receiver Design for Digital Communications, 2nd Edition” SciTech Publishing, 2012, ISBN13-978-1891121807. Ref. Book 2: Razavi, “RF Microelectronics, ISBN 9780137134731 Co/Pre-requisites: EEE433, EEE523, EEE445 (recommended) + basic knowledge in linear systems, analog/digital circuits and basic communication theory Grading Policy: Homework: 20% Laboratory Projects: 30% Two Exams: 50% (25% each) Homework: Homework needs to be submitted in the first 10 minutes of the class. No late homework is accepted. Homework solutions will be posted on Blackboard. Exams: There will be two exams: Exam 1: ~ the middle of the semester and will cover the first half of the material. Exam 2: Final exam and covers the second half of the material. 2nd Edition” Prentice Hall, Final exam will be held on Thursday, May 2 (12:10pm-2:00pm) 1 of 3 2011, Lecture Notes: Lecture slides will be posted on Blackboard at least one day before class You are encouraged to review lectures notes before the class. Homework and Laboratory assignments will be posted on Blackboard and announced in-class. Course Description: This course is intended for graduate students interested in learning about the design of wireless transceivers (mainly at the system level). The course will provide the students with the tools and techniques needed to: Learn and apply RF terminology such as dB, dBm, VSWR, return loss, mismatch loss Understand propagation losses and link budgets. Understand, calculate, and assess performance impacts of system parameters such as: noise figure, sensitivity, P1dB, IP2, IP3, EVM, and phase noise. Design (at a circuit level) a few of the most critical blocks in today’s RF transceivers (e.g. low noise amplifier, mixer, and power amplifier). Analyze the trade-offs between radio architectures, circuit performance, and overall system performance. Examples of radio architectures from commercial systems (e.g. GSM, WCDMA) will be discussed. Academic Student Code of Conduct While discussions between students are encouraged; cheating in this course will not be tolerated. Any student found cheating on an exam or assignment may be given a failing grade for the course and flagrant violations can result in additional consequences. You are cheating if you represent someone else's work as your own or if someone else represents your work as theirs. All graded work (exams, homework assignments, as well as any written exercises or quizzes) in this class must represent your individual work only. Students may discuss the conceptual aspects of an assignment, but in solving problems, students must turn in their own, independently developed solutions. Grading may include executing software on your solutions that compares the structure and content of your solution files with that of other students. Any cases of suspected cheating will be referred directly to the College of Technology and Applied Sciences according to established policy. By your registration in this class, you are assumed to have read, understand and agreed to this policy, as well as to the procedures conveyed at the web site below. http://azregents.asu.edu/rrc/Policy%20Manual/5‐303‐Prohibited%20Conduct.pdf 2 of 3 APPROXIMATE Course Schedule The schedule below is approximate and may vary based upon lecture questions, timing, and students’ progress. Lecture Topics Homework Laboratory Projects WEEK 1 ‐ System Overview ‐ Obtain Cadence ‐ System Noise Account/Access 1/8/2013 WEEK 2 ‐ Circuit Noise ‐ Intro to LNAs 1/15/2013 WEEK 3 ‐ LNA CS Architecuture ‐ LNA Cascode Architecture 1/22/2013 WEEK 4 ‐ System Nonlinearity ‐ Gain Compression, HD 1/29/2013 Lab 1 HW 1 WEEK 5 ‐ Nonlinearity Link Budget ‐ Introduction to Mixers 2/05/2013 WEEK 6 ‐ Mixer Details ‐ Rx Architectures 2/12/2013 WEEK 7 ‐ Rx Architectures ‐ Modulation (AM, FM, PM) 2/19/2013 Lab 2 HW 2 ‐ Digital Modulation, Spectral WEEK 8 Efficiency, Constellations 2/26/2013 ‐ Lab 2 Presentations WEEK 9 ‐ Lab 2 Presentations ‐ Midterm Exam 3/05/2013 WEEK 10 ‐ Spring Break 3/12/2013 ‐ Pulse Shaping WEEK 11 ‐ Intersymbol Interference 3/19/2013 ‐ Intro to Tx Architectures HW 3 Lab 3 HW 4 Lab 4 WEEK 12 ‐ ACPR/ACLR ‐ EVM 3/26/2013 ‐ Tx Building Blocks WEEK 13 ‐ Power Amplifiers 4/2/2013 WEEK 14 ‐ PLL Architectures ‐ PLL Noise 4/9/2013 WEEK 15 ‐ Phase Noise/Jitter ‐ VCOs 4/16/2013 WEEK 16 ‐ VCOs 4/23/2013 4/30/2013 5/2/2013 ‐ Review for Final Exam ‐ Final Exam 3 of 3