- Kamaljeeth Instrument

advertisement

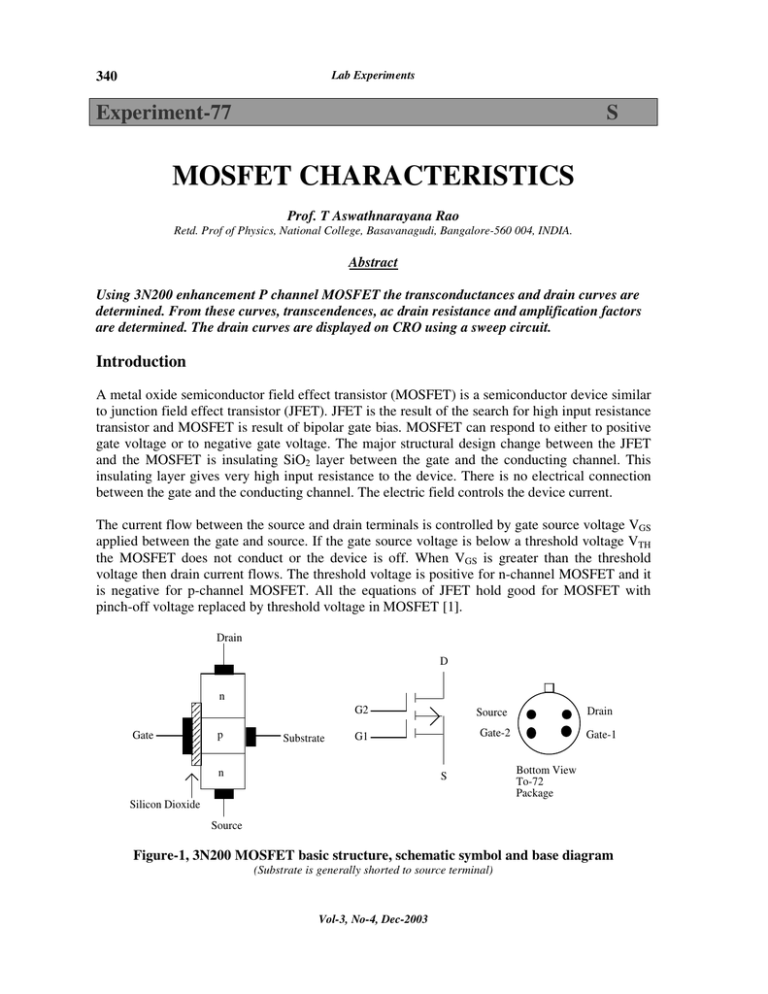

Lab Experiments 340 Experiment-77 S MOSFET CHARACTERISTICS Prof. T Aswathnarayana Rao Retd. Prof of Physics, National College, Basavanagudi, Bangalore-560 004, INDIA. Abstract Using 3N200 enhancement P channel MOSFET the transconductances and drain curves are determined. From these curves, transcendences, ac drain resistance and amplification factors are determined. The drain curves are displayed on CRO using a sweep circuit. Introduction A metal oxide semiconductor field effect transistor (MOSFET) is a semiconductor device similar to junction field effect transistor (JFET). JFET is the result of the search for high input resistance transistor and MOSFET is result of bipolar gate bias. MOSFET can respond to either to positive gate voltage or to negative gate voltage. The major structural design change between the JFET and the MOSFET is insulating SiO2 layer between the gate and the conducting channel. This insulating layer gives very high input resistance to the device. There is no electrical connection between the gate and the conducting channel. The electric field controls the device current. The current flow between the source and drain terminals is controlled by gate source voltage VGS applied between the gate and source. If the gate source voltage is below a threshold voltage VTH the MOSFET does not conduct or the device is off. When VGS is greater than the threshold voltage then drain current flows. The threshold voltage is positive for n-channel MOSFET and it is negative for p-channel MOSFET. All the equations of JFET hold good for MOSFET with pinch-off voltage replaced by threshold voltage in MOSFET [1]. Drain D n Gate p Substrate G2 Source Drain G1 Gate-2 Gate-1 n S Bottom View To-72 Package Silicon Dioxide Source Figure-1, 3N200 MOSFET basic structure, schematic symbol and base diagram (Substrate is generally shorted to source terminal) Vol-3, No-4, Dec-2003 Lab Experiments 341 A negative gate potential results in depletion mode of operation and positive gate potential results in enhancement mode of operation. By design, change it is possible make MOSFET operate any one of these modes [2]. Few MOSFETS are also available with dual gate useful for cascading purpose. MOSFET 3N200 is one such device 3N200 is a dual gate p channel enhancement MOSFET for small signal application. It can be also operated in the depletion mode with very low gate voltage less than one volt. However, it is generally meant for enhancement mode of operation. Figure-1 shows the basic structure, schematic symbol and base diagram of 3N200. Transconductance Curve A graph of drain current versus gate-source voltage at constant drain-source voltage is known as transconductance curve. Threshold voltage of MOSFET is the gate-source that makes the drain current zero. Below threshold voltage, the MOSFET is off and above threshold voltage the MOSFET is on. This is the switching characteristic of the MOSFET. The drain current is given by V I D = I DSS 1 − GS VTH Where 2 …1 IDSS is the drain current for VGS=0V VTH is the threshold voltage All the equations that control the conduction in JFET also control MOSFET. Equation –1 represents the transconductance curve of a MOSFET. The transconductance at zero gate-source voltage is given by g mo = − 2I DSS VTH …2 Transconductance vary with gate-source voltage as V g m = g mo 1 − GS VTH …3 Drain Curves The drain curves or the output curves are the set of curves obtained by experiment, which relate the drain current with drain-source voltage for different gate-source voltages. Drain curves are also known as output curves. Testing MOSFET Vol-3, No-4, Dec-2003 Lab Experiments 342 MOSFET is a delicate semiconductor device because of its insulating layer SiO2. For lab experiments, it is better you test before using it. After identification of its terminals, a DMM is used to measure resistance across drain and source terminals. In either polarity of the DMM the drain, source resistance for MOSFET is of the order of 100-150 ohms. The resistance between gate- source and gate- drain must be infinity in either polarity. In case of SiO2 layer breakage, the gate-drain and gate-source resistance is not infinity. Instruments Used Dual power supply with 0 to ±5V variable, 0-15V/0.2A variable power supplies, digital dc milliammeter 0-200mA/0-20 mA dual range, digital dc voltmeter 0-2V/0-20V dual range. Components Used MOSFET 3N200, resistor 100Ω/2W, heat sink for mosfet in the form of aluminum plate (1”x1”) Optional Components for displaying output curve on CRO DAC0808, 74LS193,LF356, resistors 100K, 5.6K, trim pots 1K, 10K, capcitors 0.1µF. Experimental Procedure The experiment consists of three parts Part A, Transconductance curve Part B, Drain curves Part C, display of drain curve on CRO. Part A, Transconductance curve 1. The heat sink is fitted to the body of the MOSFET. The circuit is rigged as shown in Figure2. VDD power supply is 0-15V variable and VGG power supply is 0 to ±5V variable. Positive and negative voltages are selected by a toggle switch of the power supply unit. (DCP201 model of KamalJeeth Make). ID VGG G1 G2 100 Ohms D V VDS VDD S Figure-2, Circuit connections for MOSFET characteristics (Note: A crocodile clip also can be used as heat sink in place of aluminum plate. For trials below +2volts VGS, there is no need of heat sink. With heat sink the decrease in the drain current in the saturation region can be reduced.) Vol-3, No-4, Dec-2003 Lab Experiments 343 2. The resistance in Figure-2 is a protective resistance. For transconductance curve it is not required. VDD is directly connected to the digital milliameter voltmeter junction. 3. The drain- source voltage VDS is set to 4 volts by adjusting VDD power supply. 4. The gate-source voltage VGS is set to zero. The milliammeter reads drain current. This drain current is IDSS = 3.8mA 5. The VGG supply is set to 0 to –5V position. VGS is varied closely watching the decrease in the drain current. The drain current becomes zero at certain voltage. This VGS is measured and it is the threshold voltage. Table-1 VGS(V) ID(mA) gm (mS) Expt Thet -1.00 0 0 0 -0.75 0.41 0.24 -0.54 -0.50 1.24 0.95 -2.48 -0.25 2.21 2.13 -8.84 0 3.80 3.80 7.60 0.25 5.65 5.93 22.60 0.50 7.91 8.55 15.82 0.75 10.05 11.63 13.40 1.00 12.00 15.20 12.00 2.00 24.10 34.20 12.05 3.00 36.49 60.80 12.16 4.00 50.15 95.00 12.53 Drain current variations with Gate-source voltage Expt Thet Drain Current (mA) 100 75 50 25 0 -2 -1 0 1 2 3 4 Gate-Source Voltage (V) Figure-3, Transconductance curve VTH = -1V. g mo = − 2I DSS − 2 x 3.8mA = = 7.6m S VTH −1 Vol-3, No-4, Dec-2003 5 Lab Experiments 344 6. Further VGS is increased in the forward direction in steps of 0.25volts and the corresponding drain current is noted in Table-1. 7. Trial is repeated by varying VGS in suitable steps up to a maximum of +4 volts. Corresponding drain current is noted in Table-1. 8. A transconductance curve is drawn taking gate-source voltage on X-axis and drain current on Y-axis as shown in Figure-3. It is observed that the experimental and theoretical value differ very much. May be because the equation is a lending from JFET. Drain Curves 9. The resistance in the circuit is now included. Both the voltage sources are set to zero. The VGG supply is set 0 to –5Vrange and VGS is set to - 0.5V. 10. VDS is slowly increased in steps of 0.25Volts up to a maximum of 2 volts. In each case, the drain current is noted in Table-2. Further VDS is increased in steps of 1 volt up to a maximum of 10 volts and the corresponding drain current is noted. 11. Trial is repeated by varying VGS to 0, +2, +3,and +4volts. In each case VDS is varied from 0 to 10 volts and the drain, current is noted in Table-2. Table-2 ID (mA) VDS(V) VGS = -0.5V VGS = 0V VGS = +2V VGS = +3V VGS = +4V 0 0 0 0 0 5.12 0.25 1.21 1.65 2.20 4.05 11.50 0.50 1.70 2.61 3.40 10.12 17.15 0.75 1.98 3.05 4.05 14.08 22.0 1.00 2.01 3.22 4.10 19.50 26.1 1.25 2.01 3.30 4.20 23.1 31.0 1.50 2.01 3.31 4.30 26.1 34.1 1.75 2.01 3.42 4.35 29.4 38.0 2.00 2.01 3.42 4.41 31.5 44.1 3.00 2.01 3.42 4.43 38.0 52.0 4.00 2.01 3.50 4.45 39.5 53.0 5.00 2.01 3.51 4.60 40.1 54.5 6.00 2.04 3.60 4.62 41.5 55.6 7.00 2.04 3.60 4.75 42.3 56.7 8.00 2.05 3.65 4.80 43.3 57.9 9.00 2.18 3.80 5.00 44.5 60.3 10.00 2.20 4.10 5.30 45.6 62.0 Drain current variations with drain-source voltage for different VGS 12. A graph is drawn talking drain-source voltage along X-axis and drain current along Y-axis. The graph is shown in Figure-4. The slope of the graph is determined and ac drain resistance is calculated and presented in Table-3. AC drain resistance for VGS= -0.5V is Vol-3, No-4, Dec-2003 Lab Experiments rd = 345 1 1 = = 42KΩ Slope 23.75x10 − 6 Drain Current (mA) Similarly ac resistance for VGS= 0V and VGS = 2.0V is calculated and presented in Table-3 along with corresponding gm values from Table-1. VGS=-0.5V VGS=0V VGS=+3V VGS=+4V VGS=+2V 70 60 50 40 30 20 10 0 0 2 4 6 8 10 12 Source Drain Voltage (V) Figure-4, MOSFET output characteristics curve VGS(V) -0.5 0 +2.0 Table-3 rd (KΩ) gm (mS) 42.0 2.48 12.1 7.60 8.8 12.00 µ= gmrd 104 92 105 Amplification factor of 3N200 MOSFET 13. The amplification factor µ=gmrd is also calculated and presented in Table-3. Part C, Display of drain curves on CRO. (a) (b) (c) Figure-6, (a) The gate and drain drive waveforms, (b) Eight drain curves (c) Sixteen drain curves Vol-3, No-4, Dec-2003 Lab Experiments 346 Figure-5 shows circuit arrangement to displaying drain curves on CRO. The gate of the MOSFET is fed with staircase wave, which remains in one voltage state for one millisecond. During this one millisecond the drain voltage, vary from 0 to 10 volts in either way. This sweep of drain voltage results in one curve. When step input attains its next step voltage again the drain voltage sweep and second curve is obtained. The 16-step input staircase waveform resulted in 16 drain curves. Figure-6 shows the drain curves. By disconnecting pin 9 of the DAC from counter resulted in eight drain curves. TP2 in Figure-5, is the offset adjustment for the triangular wave. The triangular waveform has lower 0 volt level and upper 20V level . CLOCK 1KHz 8 14 RF=100K 1 6 2 3 11 12 -15V 4 Io RI=10K 4 74LS193 5.6K 2 9 DAC0808 10 7 5 15 2 3 + 560 Ohms 14 7 8 16 10K TP1 - 11 10.00V Vref 13 5 6 +5V REF=100K IREF +15V +5V 6 LF356 1 15 16 0.1 7 3 10 9 +15V +15V -15V 10K TP2 22K 10K 4 2 - 3 + 10K -15V 6 T0 CRO channel-B LF356 3N200 7 20V pp Triangular wave from function generator +15V To CRO channel-A 10K Figure-5, Sweep generator circuit used to display drain curve on CRO. (For circuit detail refer experiment-76) Results The results obtained are tabulated in Table-4 Table-4 Parameters Expt IDSS (mA) 3.8 VTH(V) -1.0 gmo(mS) 7.6 µ 100 Various parameters of 3N200 MOSFET Vol-3, No-4, Dec-2003 Vo Lab Experiments 347 Discussions MOSFET has similar characteristics compared to JFET with –ve gate voltage replaced by positive gate voltage. Further, the current carrying capacity of the MOSFET is high compared to JFET because there is no junction formation in MOSFET at the gate terminal. The threshold voltage is negative which is indicates that for very low negative voltage 3N200 can be operated either in enhancement or in the depletion mode. The transconductance curve appeared to be quadratic rather than linear as per theory. The equation governing the transconductance may not be accurate for MOSFET. The amplification factor for low signal (for VGS < 2V) is large (100) compared to JFET. References [1] Jeethendra Kumar P K, JFET Characteristics, LE Vol-1, No-1, November-2001, Page 32. [2] A P Malvino, Electronic principles, 3rd Edn, Page-368. Vol-3, No-4, Dec-2003