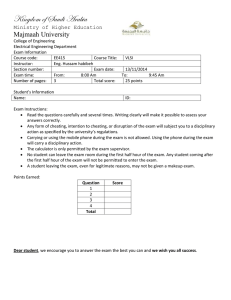

Lecture10 Inverter Dynamics

advertisement

Dynamic Behavior THE INVERTER DYNAMICS Propagation Delay, Tp •Defines how quickly output is affected by input •Measured between 50% transition from input to output •tpLH defines delay for output going from low to high •tpHL defines delay for output going from high to low •Overall delay, tp , defined as the of tpLH and tpHL [Adapted from Rabaey’s Digital Integrated Circuits , ©2002, J. Rabaey et al.] EE415 VLSI Design EE415 VLSI Design Dynamic Behavior Rise and fall time, Tr and Tf Delay Definitions Vin •Defines slope of the signal 50% •Defined between the 10% and 90% of the signal t t swing V out t pHL pLH 90% Propagation delay and rise and fall times affected by 50% the fan-out due to larger capacitance loads 10% tf EE415 VLSI Design t tr EE415 VLSI Design The Ring Oscillator •A standard method is needed to measure the gate Ring Oscillator v0 v1 v2 v3 v4 v5 delay •It is based on the ring oscillator v0 v1 v5 •2Nt p >> tf + tr for proper operation T = 2 × tp × N EE415 VLSI Design EE415 VLSI Design 1 Power Dissipation •Power consumption determines heat dissipation and energy consumption Power Dissipation Supply-line sizing •Power influences design decisions: •packaging and cooling •width of supply lines •power-supply capacity •# of transistors integrated on a single chip Battery drain, cooling Power requirements make high density bipolar ICs impossible (feasibility, cost, reliability) EE415 VLSI Design EE415 VLSI Design Power Dissipation •P peak = static power + dynamic power •Dynamic power: Power Dissipation •Propagation delay is related to power consumption •tp determined by speed of charge transfer •(dis)charging capacitors •fast charge transfer => fast gate •temporary paths from VDD to VSS •proportional to switching frequency •Static power: •fast gate => more power consumption •Power-delay product (PDP) •quality measure for switching device •static conductive paths between rails •PDP = energy consumed /gate / switching event •leakage •measured using ring oscillator •increases with temperature EE415 VLSI Design EE415 VLSI Design Power Dissipation Supply-line sizing CMOS Inverter: Steady State Response •CMOS technology: •No path exists between VDD and VSS in steady state •No static power consumption! (ideally) •Main reason why CMOS replaced NMOS in early 80’s Battery drain, cooling Energy consumed /gate /switching event •NMOS technology: •Has NMOS pull -up device that is always ON •Creates voltage divider when pull-down is ON •Power consumption puts upper bound on (# devices / chip) EE415 VLSI Design EE415 VLSI Design 2 CMOS Inverter Load Characteristics Voltage Transfer Characteristic V G V DD S D in V C out L D G S EE415 VLSI Design EE415 VLSI Design CMOS Inverter Load Lines PMOS Load Lines V DD IDn G V in = V DD+VGSp IDn = - IDp V out = V DD+VDSp S D V in D V out CL G IDp S IDn IDn (A) V out IDn V in=0 Vin =0 V in=3 V DSp V in = V DD+VGSp IDn = - IDp Vout = V Vin = 2.5V Vin = 0.5V 1.5 Vin = 2.0V 1 Vin = 1.0V 0.5 Vin = 1.5V Vin = 2.0V 0 Vin = 2.5V 0 Vout V GSp=-2 V GSp=-5 NMOS Vin = 0V 2 Vin = 2V Vin =3 V DSp PMOS2.5 X 10-4 Vin = 1V Vin = 1.5V Vin = 0.5V Vin = 1.5V Vin = 1.0V Vin = 0.5V 0.5 DD+VDSp 1 1.5 2 2.5 Vin = 0V Vout (V) 0.25um, W/Ln = 1.5, W/Lp = 4.5, VDD = 2.5V, VTn = 0.4V, VTp = -0.4V EE415 VLSI Design EE415 VLSI Design CMOS Inverter VTC Linear Saturation pMOS Vin -VDD = VGS> VT Vin -VDD =VGS< VT Vin -Vout=VGD < VT Vin -VDD =VGS> VT Vin -Vout=VGD >VT nMOS Vin = VGS< VT Vin =VGS> VT Vin -Vout =VGD > VT Vin =VGS> VT Vin -Vout =VGD < VT NMOS off PMOS res 2.5 2 1.5 1 0.5 0 Vout (V) NMOS sat PMOS res NMOS sat PMOS sat NMOS res PMOS sat 0 EE415 VLSI Design Cutoff 0.5 1 1.5 Vin (V) 2 VDD NMOS res PMOS off Regions of operations For nMOS and pMOS In CMOS inverter G S D V in Vout D 2.5 CL G S EE415 VLSI Design 3 CMOS Inverter Load Characteristics •For valid dc operating points: •current through NMOS = current through PMOS •=> dc operating points are the intersection of load lines •All operating points located at high or low output levels Voltage Transfer Characteristic •=> VTC has narrow transition zone •high gain of transistors during switching •transistors in saturation •high transconductance (gm) •high output resistance (voltage controlled current source) EE415 VLSI Design EE415 VLSI Design Switching Threshold Switch Threshold Example l l l l VM where V in = Vout (both PMOS and NMOS in saturation since VDS = VGS) VM ≈ rVD D/(1 + r) where r = k pVDSATp/k nV DSATn Switching threshold set by the ratio r, which compares the relative driving strengths of the PMOS and NMOS transistors minimum size NMOS ((W/L)n of 1.5) NMOS PMOS x -30 x 10-6 -1.0 λ(V-1) 0.06 -0.1 x (1.25 – 0.4 – 1.0/2) = 3.5 Noise Margins Determining VIH and VIL 1.3 1.2 1.1 1 q Increasing the width of the PMOS moves V M towards VDD 0.9 0.8 1 (W/L) p/(W/L) n Note: x- axis is semilog ~3.4 10 By definition, VIH and V IL are where dVout/dVin = -1 (= gain) VOH = V DD 2 Vout is relatively insensitive to variations in device ratio l setting the ratio to 3, 2.5 and 2 gives VM’s of 1.22V, 1.18V, and 1.13V EE415 VLSI Design k’(A/V2) 115 x 10-6 -30 x 10-6 (W/L)p = 3.5 x 1.5 = 5.25 for a VM of 1.25V 3 q VM 0 .1 VDSAT(V) 0.63 -1 EE415 VLSI Design 1.4 VM (V) γ(V0.5 ) 0.4 -0.4 = (W/L)n Simulated Inverter VM 1.5 VT0(V) 0.43 -0.4 (W/L)p 115 x 10-6 0.63 (1.25 – 0.43 – 0.63/2) Want VM = VDD/2 (to have comparable high and low noise margins), so want r ≈ 1 (W/L)p = k n’VDSATn(VM- VTn-V DSATn/2) (W/L)n k p’VDSATp(VD D-VM +VTp +VDSATp/2) EE415 VLSI Design In 0.25 µm CMOS process, using parameters from table, VDD = 2.5V, and VM 1 VOL = GND0 VIL Vin VIH A piece-wise linear approximation of VTC NM H = VDD - VIH NM L = VIL - GND Approximating: VIH = VM - VM /g VIL = VM + (VDD - VM )/g So high gain in the transition region is very desirable EE415 VLSI Design 4 Gain Determinates Vin 0.25um, (W/L) p/(W/L) n = 3.4 (W/L) n = 1.5 (min size) VDD = 2.5V 2.5 2 1.5 1 0.5 0 0 0.5 1 1.5 Gain is a strong function of the slopes of the currents in the saturation region, for Vin = VM 2 0 -2 VM ≈ 1.25V, g = -27.5 -4 (1+r) g ≈ ---------------------------------(VM-VTn-VDSATn/2)(λn - λp ) VIL = 1.2V, VIH = 1.3V NM L = NMH = 1.2 (actual values are VIL = 1.03V, VIH = 1.45V NM L = 1.03V & NMH = 1.05V) 0 0.5 1 1.5 2 2.5 gain -6 üDetermined by technology parameters, especially λ. -12 -14 üOnly designer influence through supply voltage and VM (transistor sizing ). -16 Output resistance low-output = 2.4kΩ high-output = 3.3kΩ Vin (V) -8 -10 -18 EE415 VLSI Design EE415 VLSI Design Impact of Process Variation 2,5 0,2 Good PMOS Bad NMOS 2 0,15 Vout (V) 2.5 2 1.5 1 0.5 0 Scaling the Supply Voltage 1,5 Vout (V) Vout (V) Vout (V) CMOS Inverter VTC from Simulation Nominal Bad PMOS Good NMOS 1 0,05 0,5 0 0.5 1 1.5 2 2.5 Vin (V) process variations (mostly) cause a shift in the switching threshold EE415 VLSI Design 0,1 Gain=-1 0 0 0 0 0,5 1 Vin (V) 1,5 2 Device threshold voltages are kept (virtually) constant EE415 VLSI Design 0,05 2,5 0,1 0,15 0,2 Vin (V) Device threshold voltages are kept (virtually) constant Switch Model of Dynamic Behavior VDD VDD Propagation Delay Rp Vin = 0 EE415 VLSI Design Vout Vout CL CL Rn Vin = V DD Gate response time is determined by the time to charge CL through R (discharge CL through Rn) p EE415 VLSI Design 5 What is the Inverter Driving? VDD VDD M2 Cdb 2 Cgd 12 Vin CMOS Inverter Propagation Delay Approach 1 M1 tpHL = C L Vswing /2 M4 Cg4 Vout Cdb 1 VDD Vout Cw Cg3 I av 2 M3 CL Vout ~ Interconnect I av CL kn VDD Fanout V in Simplified Model Vout CL Vin = VD D EE415 VLSI Design EE415 VLSI Design CMOS Inverter Propagation Delay Approach 2 VDD CMOS Inverter: Transient Response How can the designer build a fast gate? •tpHL = f(Ron * CL ) tpHL = f(R on.CL) •Keep output capacitance, CL , small = 0.69 RonC L •low fan-out V out Vout CL 1 Ron V DD •keep interconnections short (floor -plan your layout!) ln(0.5) Vout = VOH e − t /( R onC L ) 0.5 •Decrease on-resistance of transistor •increase W/L ratio •make good contacts (slight effect) 0.36 V in = V DD t R onC L EE415 VLSI Design EE415 VLSI Design MOS Transistor Small Signal Model G D + v gs Determining VIH and VIL gm vgs ro - Define S VIH and VIL are based on derivative of VTC equal to -1 EE415 VLSI Design EE415 VLSI Design 6 Transient Response Inverter Transient Response ? 3 3 2.5 tpLH tpHL 1.5 1.5 Vout (V) V o u t(V) 2 tp = 0.69 CL ( Reqn+Reqp)/2 2 VDD =2.5V 0.25µm W/Ln = 1.5 W/Lp = 4.5 Reqn= 13 kΩ (÷ 1.5) Reqp= 31 kΩ (÷ 4.5) Vin 2.5 tpHL tf 1 tr tpLH 1 0.5 tpHL = 36 psec 0.5 0 tpLH = 29 psec -0.5 so -0.5 0 0 0 0.5 1 1.5 2 t (sec) 0.5 1 1.5 2.5 From simulation: tpHL = 39.9 psec and x 10 -10 tp = 32.5 psec x 10 -10 t (sec) 2.5 EE415 VLSI Design tpLH = 31.7 psec EE415 VLSI Design Delay as a function of VDD Sizing Impacts on Delay x 3.8 5.5 10 -11 for a fixed load 3.6 5 The majority of the improvement is already obtained for S = 5. Sizing factors larger than 10 barely yield any extra gain (and cost significantly more area). 3.4 4.5 3.2 3 tp(sec) 4 2.8 3.5 2.6 3 2.4 p t (normalized) 2 2.5 2.2 2 2 1 1.5 1 0.8 3 5 7 9 11 13 15 S 1 1.2 1.4 1.6 V DD 1.8 2 2.2 self-loading effect (intrinsic capacitance dominates) 2.4 (V) EE415 VLSI Design EE415 VLSI Design PMOS/NMOS Ratio Effects Input Signal Rise/Fall Time x 10 -11 x 10 -11 tpLH tp(sec) 4,5 β of 2.4 (= 31 kΩ/13 kΩ) gives symmetrical response tpHL 4 5.4 l β of 1.6 to 1.9 gives optimal performance tp In reality, the input signal changes gradually (and both PMOS and NMOS conduct for a brief time). This affects the current available for charging/discharging CL and impacts propagation delay. 5.2 5 4.8 4.6 tp(sec) 5 4.4 4.2 4 3,5 l l 3 1 2 3 β = (W/Lp)/(W/Ln) EE415 VLSI Design 4 tp increases linearly with increasing input rise time, tr , once tr > tp tr is due to the limited driving capability of the preceding gate 5 3.8 3.6 0 2 4 ts (sec)6 8 x 10 -11 for a minimum -size inverter with a fan-out of a single gate EE415 VLSI Design 7 CMOS Inverter: Four Views Inverter Sizing V dd V in V out V in V out Gnd Logic Transistor Layout EE415 VLSI Design EE415 VLSI Design CMOS Inverter Sizing Out Inverter Delay • Minimum length devices, L=0.25µm • Assume that for WP = 2WN =2 W • same pull-up and pull-down currents • approx. equal resistances R N = R P • approx. equal rise t pLH and fall t pHL delays • Analyze as an RC network In metal1-poly via polysilicon metal1 metal2 V DD pdiff W RP = Runit P Wunit PMOS (4/.24 = 16/1) NMOS (2/.24 = 8/1) metal1-diff via ndiff −1 W ≈ Runit N Wunit Delay (D): t pHL = (ln 2) R NCL GND metal2-metal1 via Load for the next stage: EE415 VLSI Design 2W W −1 = RN = RW t pLH = (ln 2) R P CL C gin = 3 EE415 VLSI Design Inverter with Load W Cunit Wunit Inverter with Load CP = 2Cunit Delay Delay 2W RW W CL RW Load (CL ) t p = k R WC L k is a constant, equal to 0.69 Assumptions: no load -> zero delay EE415 VLSI Design Physical Wunit = 1 CN = C unit Cint CL Load Delay = kRW (Cint + CL) = kRW Cint + kRW C L = kRW Cint (1+ CL /Cint ) = Delay (Internal) + Delay (Load) EE415 VLSI Design 8 Delay Formula Inverter Chain l Real goal is to minimize the delay through an inverter chain Delay ~ RW (C int + C L ) In t p = kRW C int (1 + C L / Cint ) = t p 0 (1 + f / γ Out Cg,1 ) 1 2 N CL the delay of the j-th inverter stage is tp,j = tp0 (1 + Cg,j+1/(γCg,j)) = tp0(1 + fj/ γ) and tp = tp1 + tp2 + . . . + tpN Cint = γCgin with γ ≈ 1 f = CL/Cgin - effective fanout R = R unit /W ; Cint =WC unit t p0 = 0.69Runit Cunit so l EE415 VLSI Design tp = ∑tp,j = tp0 ∑ (1 + C g,j+1/(γCg,j)) If CL is given » How should the inverters be sized? » How many stages are needed to minimize the delay? EE415 VLSI Design Optimum Delay and Number of Stages Apply to Inverter Chain In Out When each stage is sized by f and has same eff. fanout f: f N = F = C L / Cgin ,1 1 2 N CL Effective fanout of each stage: t p = t p1 + t p2 + …+ t pN f=NF Cgin, j +1 t pj ~ RunitCunit1 + γCgin, j N N Cgin, j +1 , Cgin, N +1 = CL t p = ∑ t p, j = t p0 ∑ 1 + γCgin, j j =1 i =1 Minimum path delay EE415 VLSI Design ) EE415 VLSI Design Example Optimal Number of Inverters l In Out 1 C1 f f2 CL = 8 C1 CL/ C1 has to be evenly distributed across N = 3 stages: l 3 f = 8=2 l EE415 VLSI Design ( t p = Nt p0 1 + N F / γ What is the optimal value for N given F (=f N) ? » if the number of stages is too large, the intrinsic delay dominates » if the number of stages is too small, the effective fanout dominates The optimum N is found by differentiating the minimum delay divided by the number of stages and setting the result to 0, For γ = 0 (ignoring self -loading) N = ln (F) and the effective-fan out becomes f = e = 2.71828 EE415 VLSI Design 9 Optimum Effective Fan-Out Optimum Number of Stages 2.5 l f = exp(1 + γ f ) 1 Cg,1 = 1 Cg,1 = 1 CL = 64 Cg,1 2.8 Cg,1 = 1 4 3 2 1 0.5 1 1.5 γ 2 2.5 3 1 1.5 2 2.5 f 3 3.5 4 4.5 5 Choosing f larger than optimum has little effect on delay and reduces the number of stages (and area). » Common practice to use f = 4 (for γ = 1) » But too manystages has a substantial negative impact on delay f tp 1 64 65 2 8 Impact of Buffer Staging for Large CL F (γ = 1) 18 16 Cg,1 = 1 1 N CL = 64 Cg,1 8 1 5 EE415 VLSI Design Example of Inverter (Buffer) Staging 4 6 0 0 EE415 VLSI Design 1 t Fop ) For γ = 0, f = e, N = lnF 3.5 3 t p 0 ln F f γ t p = Nt p 0 F / γ + 1 = ln f + ln f γ ∂ t p t p 0 ln F ln f −1 − γ f = ⋅ =0 ∂f γ ln 2 f ( 4.5 4 ln F C L = F ⋅ Cin = f N Cin with N = ln f 1/ N 7 normalized delay 5 For a given load, CL and given input capacitance Cin Find optimal sizing f CL = 64 Cg,1 8 22.6 3 4 15 4 2.8 15.3 l CL = 64 Cg,1 EE415 VLSI Design Unbuffered 10 11 Two Stage Chain 8.3 Opt. Inverter Chain 8.3 100 101 22 16.5 1,000 1001 65 24.8 10,000 10,001 202 33.1 Impressive speed-ups with optimized cascaded inverter chain for very large capacitive loads. EE415 VLSI Design Design Challenge l Keep signal rise times smaller than or equal to the gate propagation delays. » good for performance » good for power consumption l Keeping rise and fall times of the signals small and of approximately equal values is one of the major challenges in high-performance designs slope engineering. EE415 VLSI Design Power Dissipation EE415 VLSI Design 10 Dynamic Power Dissipation Modification for Circuits with Reduced Swing V dd Vdd V dd Vin V dd -Vt Vout CL CL Energy/transition = CL * Vdd 2 E0 Power = Energy/transition * f = CL * Vdd 2 * f Not a function of transistor sizes! Need to reduce CL , Vdd , and f to reduce power. EE415 VLSI Design →1 = C L • Vd d • ( Vd d – V t ) Can exploit reduced swing to lower power (e.g., reduced bit-line swing in memory) EE415 VLSI Design Node Transition Activity and Power Short Circuit Currents Vdd Consider switching a CMOS gate for N clock cycles E N = CL • Vd d2 • n (N ) Vin Vout EN : the energy consumed for N clock cycles CL n(N ): the number of 0->1 transition in N clock cycles EN n (N ) 2 lim -------- • fc l k = lim -----------C V f N → ∞ N • L • dd • clk N →∞ N α0 → 1 = EE415 VLSI Design 0.15 n (N ) lim -----------N→∞ N P avg = α 0 C V 2 f → 1 • L • dd • clk How to keep ShortShort -Circuit Currents Low? 0.10 IVDD (mA ) P avg = 0.05 0.0 1.0 2.0 3.0 Vi n (V) 4.0 5.0 EE415 VLSI Design Minimizing ShortShort-Circuit Power 8 7 Vdd =3.3 6 5 Vdd =2.5 4 norm P 3 2 Vdd =1.5 1 0 0 1 2 3 4 5 t sin/tsout Short circuit current goes to zero if t fall >> t rise , but can’t do this for cascade logic, so ... EE415 VLSI Design EE415 VLSI Design 11 Leakage Reverse--Biased Diode Leakage Reverse Vdd GATE p+ Vout p+ N Reverse Leakage Current Drain Junction Leakage + Vdd - Sub-Threshold Current I DL = JS × A Sub-threshold current one of most compelling issues in low-energy circuit design! EE415 VLSI Design Subthreshold Leakage Component JS = 10-100 pA/µ m2 at 25 deg C for 0.25µ m CMOS JS doubles for every 9 deg C! EE415 VLSI Design Static Power Consumption Vdd Istat Vout V in =5V CL Pstat = P(In=1) .V dd . Istat Wasted energy … Should be avoided in almost all cases, but could help reducing energy in others (e.g. sense amps) EE415 VLSI Design EE415 VLSI Design Principles for Power Reduction l Prime choice: Reduce voltage! Impact of Technology Scaling » Recent years have seen an acceleration in supply voltage reduction » Design at very low voltages still open question (0.6 … 0.9 V by 2010!) l l Reduce switching activity Reduce physical capacitance » Device Sizing: for F=20 – fopt(energy)=3.53, fopt(performance)=4.47 EE415 VLSI Design EE415 VLSI Design 12 Goals of Technology Scaling l Make things cheaper: » Want to sell more functions (transistors) per chip for the same money » Build same products cheaper, sell the same part for less money » Price of a transistor has to be reduced l But also want to be faster, smaller, lower power EE415 VLSI Design Technology Generations Technology Scaling l Goals of scaling the dimensions by 30%: » Reduce gate delay by 30% (increase operating frequency by 43%) » Double transistor density » Reduce energy per transition by 65% (50% power savings @ 43% increase in frequency l l Die size used to increase by 14% per generation Technology generation spans 2-3 years EE415 VLSI Design Technology Evolution (2000 data) International Technology Roadmap for Semiconductors Year of Introduction 1999 2000 2001 2004 130 90 Technology node [nm] 180 Supply [V] 1.5-1.8 Wiring levels 6-7 6-7 7 Max frequency [GHz],Local-Global 1.2 1.6-1.4 2.1-1.6 Max µ P power [W] 90 106 130 Bat. power [W] 1.4 1.7 2.0 1.5-1.8 2008 2011 2014 60 40 30 0.6-0.9 0.5-0.6 0.3-0.6 8 9 9-10 10 3.5-2 7.1-2.5 11-3 14.9 -3.6 160 171 177 186 2.4 2.1 2.3 2.5 1.2-1.5 0.9-1.2 Node years: 2007/65nm, 2010/45nm, 2013/33nm, 2016/23nm EE415 VLSI Design Technology Evolution (1999) EE415 VLSI Design EE415 VLSI Design ITRS Technology Roadmap Acceleration Continues EE415 VLSI Design 13 Technology Scaling (1) Minimum Feature Size (micron) 10 Technology Scaling (2) 2 1 10 0 10 10 -1 -2 10 1960 1970 1980 1990 2000 2010 Year EE415 VLSI Design Number of components per chip Minimum Feature Size EE415 VLSI Design Technology Scaling (3) Technology Scaling Models • Full Scaling (Constant Electrical Field) tp decreases by 13%/year 50% every 5 years! ideal model — dimensions and voltage scale together by the same factor S • Fixed Voltage Scaling most common model until recently — only dimensions scale, voltages remain constant • General Scaling most realistic for todays situation — voltages and dimensions scale with different factors Propagation Delay EE415 VLSI Design Scaling Relationships for Long Channel Devices EE415 VLSI Design EE415 VLSI Design Transistor Scaling (velocity-saturated devices) EE415 VLSI Design 14 Dilbert Dilbert EE415 VLSI Design EE415 VLSI Design Dilbert EE415 VLSI Design Dilbert EE415 VLSI Design Dilbert EE415 VLSI Design 15