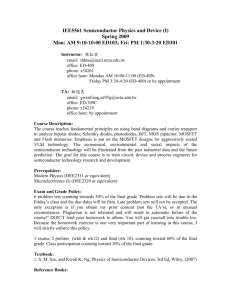

MOSFETs (A. Schwab)

advertisement

Metal oxide semiconductor - field effect transistors MOS-FET Alexander Schwarb 3th of March 2014 Introduction ● What is a MOSFET? ● Motivation ● History ● Theory ● Design ● Outlook 2 What is a MOSFET? ● Metal oxide semiconductor field effect transistor Metal n-type MOSFET Semiconductor Nature.com (May 2010), S.Sze, Physics of Semiconductor Devices 3 Motivation: MOSFETs are the backbone of todays electronics ...Household, Industry, Computers, Medicine, Communication, Transportation, Gadgets... Today, (almost) all electronic devices have MOSFETs integrated! No other human artifact has been fabricated in larger numbers. “…some consider it one of the most important technological breakthroughs in human history…” Colourbox.com 4 History ● ● First patents: 1925 J. E. Lilienfeld (MESFET) and 1934 O. Heil (MOSFET) 1947 Bipolar Junction Transistors (BJT) as a replacement for vacuum tubes, made of Ge later replaced by Si ● 1960 First MOSFET produced by Atalla & Khang, Bell Labs ● 1968 Poly-Si gate Faggin & Klein, Fairchild ● 1971 Full CPU in one chip, Intel i4004, Fraggin, Intel ● 1974 Scalling Theory, Gänsslen & Dennard, IBM ● 1978 Use of Ion implanter ● 1984 Scalling Theory <0.25 µm, Baccarani, U. Bologna ● 1986 0.1µm Si MOSFET, Sai-Halasz, IBM ● 2007 Non- SiO2 (HfO2 based) MOSFET, Intel 5 History 1935 Heil’s patent 1947 First Transistor : Bardeen, Shockley, Brattain ,Bell Labs S.Sze, Physics of Semiconductor Devices 6 History 1960: Atalla’s MOSFET 1971: Intel i4004, 2250 Transistors, 10µm technology Wikipedia, Intel.com 7 History The transistors are getting smaller, and more transistors are integrated on one chip. ... 1971: Intel i4004, 2250 Transistors, 10µm technology 1981: Intel 8008, 29000 transistors, 3µm technology 2010: Intel Core 2nd Gen. , 1.16 billion transistors, 32nm technology Intel.com 2012: Intel Core 3th Gen. , 1.4 billion transistors, 22nm technology 8 Moore's law Gordon Moore 1965: Cost vs time Moore's law is the observation that, over the history of computing hardware, the number of transistors on integrated circuits doubles approximately every two years while the cost per transistor decreases. → exponential increase of transistor count per chip S.Sze, Physics of Semiconductor Devices 9 Moore's law Number of transistors & gate size vs time ITRS: International Technology Roadmap for Semiconductors (interpolating future targets according to Moores law) Nature.com (May 2010) 10 More historical trends Efficiency also follows Moore's law Interestingly the rule is also apropriate for other electric devices such as pixel count on digital cameras and disk storage volume etc. J. Armstrong (ca.1989) 11 Technological History CPUs Feature size: Problems arise with down scalling: ● 1975: 20 μm -SiO2 growth and instability ● 1980: 10 μm ● 1985: 5 μm ● 1990: 1 μm ● 1995: 0.35 μm ● 2000: 0.18 μm ● 2005: 65 nm ● 2010: 32 nm ● 2012: 22 nm -”Short-channel effects” (SCE): “hot electron effect”, “velocity saturation”, “impact ionization” and so forth -Leakage Intel.com 12 Theory 13 . p and n doped semiconductors Consider a n-semiconductor Donator level . and a p-semiconductor Acceptor level Coma script C.Schöneberger 14 pn-junction If we join both semiconductor, the free charge carriers near the junction will equilibrate. hole e - optique-ingenieur.org 15 pn-junction The two seperate band diagrams form a new continuos banddiagram, while the Fermi energy level is now the median of both semiconductors. The zone around the junction in which the free charge carriers cancel each other out, is called the depleted region. Coma script C.Schöneberger 16 MOS-Diode If we add the corresponding charge carriers to the doped semiconductors the depletion zone decreases. → high conductance If we subtract the corresponding charge carriers from the doped semiconductors the depletion zone increases. → low conductance Coma script C.Schöneberger 17 Structure of a n-type MOSFET S.Sze, Physics of Semiconductor Devices 18 Structure of a n-type MOSFET Important parameters: charge carrier mobility µ, Threshhold Voltage Vth, On-/Off-current Ion/Ioff S.Sze, Physics of Semiconductor Devices 19 MOS-structure under equilibrium and non-equilibrium condition S.Sze, Physics of Semiconductor Devices 20 Drain-current characteristics of a MOSFET device VD < VG − VTH. The MOSFET operates similar to a resistor in this mode with a linear relation between voltage and current. Saturation occurs when VG > VTH and VD > VG − VTH. In this mode the „switch“ is on and conducting, however since drain voltage is higher than the gate voltage, part of the channel is turned off. The VD for which this happens, is called the pinch-off voltage. Pinch-off occurs when the MOSFET stops operating in the linear region and saturation occurs. Infineon.com 21 Drain-current characteristics of a MOSFET device Drain current ID vs. Drain voltage VD for different Gate voltages VG S.Sze, Physics of Semiconductor Devices 22 Current characteristics of a MOSFET device Starting from the current density: J =−qn (x) v d =−qn ( x) µ n E y q: charge n(x): electron concentration vd: drift velocity µn: mobility E: electric field . . . . . Current equation: ∂V I D = WQ I µn E =−WQ I µ n ∂y x . W: channel width Inversion layer charge: x1 Q I =− ∫ 0 qn ( x) dx S.Sze, Physics of Semiconductor Devices 23 Current characteristics of a MOSFET device Current continuity for each distance dy: y V I D ∫ 0 dy =−Wµn ∫ 0 Q I ( y) dV y Depletion approximation to calculate inversion charge Qi: Q I ( y)= Q S ( y)− Q D ( y) =−C i [V G − 2 ψ S ( y)] − Q D ( y) x Qs: semiconductor charge Qd: depletion charge Ci: insulator capacitance in inversion Vg: gate voltage ψs ( y): band bending . . . . . S.Sze, Physics of Semiconductor Devices 24 Current characteristics of a MOSFET device Band bending tight to strong inversion condition: ψ s ( y) = 2 ϕ F + V ( y) y Depletion charge on depleted area: Q D =− qN A w m =− √ 2 ϵ s qN A [2 ϕ + V ( y)] x S.Sze, Physics of Semiconductor Devices 25 Current characteristics of a MOSFET device Putting the last two expressions in the formula of Qi: Q I ( y)=−C i [V G − 2 ϕ F − V ( y)]− √ 2 ϵ s qN A [2 ϕ + V ( y)] y and integrate current continuity until drain (y=L; V=Vd) results in a complex equation. Simplifying this equation by approximating (gradual channel approximation): Vd smaller than two times Fermi potential gives . VD W I D = µ n C i (V G − V T − ) V D L 2 S.Sze, Physics of Semiconductor Devices 26 Current characteristics of a MOSFET device The threshhold voltage Vt is given by V T =2 ϕ F y 2 ϵ s qN A 2 ϕ F √ + Ci Band bending term Potential across dielectric induced by depletion charge S.Sze, Physics of Semiconductor Devices 27 Current characteristics of a MOSFET device The threshhold voltage Vt is given by V T =2 ϕ F 2 ϵ s qN A 2 ϕ F √ + Ci Nature.com (May 2010), S.Sze, Physics of Semiconductor Devices 28 Current characteristics of a MOSFET device The threshhold voltage Vt is given by V T =2 ϕ F y 2 ϵ s qN A 2 ϕ F √ + =2 ϕ Ci F + K √ϕ t 2 ϕ F The factor K (characteristic ratio of semiconductor and insulator capacitance) is given by: K= √ 2 ϵ / L D √ 2 ϵ qN A / ϕ t Ci = Ci The current equation can be understood then as follows: An average Qi across the channel at an average potential Vd/2 VD W I D = µ n C i (V G − V T − ) V D L 2 Factor Vd/L is the average electric field S.Sze, Physics of Semiconductor Devices 29 Current characteristics of a MOSFET device The drain current characteristic of MOSFET's: V Dsat Saturation region Linear region VD W I D = µ n C i (V G − V T − ) V D L 2 Id increases linearly with Vd until it levels of at Vdsat: V Dsat = V G − V T The saturated drain current then reads: 2 (V G − V T ) W I Dsat = µ n C i L 2 S.Sze, Physics of Semiconductor Devices 30 Current characteristics of a MOSFET device The drain current characteristic of MOSFET's: V Dsat Saturation region Linear region VD W I D = µ n C i (V G − V T − ) V D L 2 Id increases linearly with Vd until it levels of at Vdsat: V Dsat = V G − V T The saturated drain current then reads: 2 (V G − V T ) W I Dsat = µ n C i L 2 The central message of transistor physics: The figure of merit of the performace of a transistor is the drain current. The higher the drain current, the quicker the load of the circuit is dis-/charged. High speed electronics relies on transistors with high drain current S.Sze, Physics of Semiconductor Devices 31 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 1: Keep supply voltage high Drawbacks: → lower power for mobile devices → electric breakdown of highly scaled electronics S.Sze, Physics of Semiconductor Devices 32 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 2: reduce channel length L → Primary means of microelectronic engineers. The Philosophy in microelectronic industry relies on engineering and not on the integration of new materials. S.Sze, Physics of Semiconductor Devices 33 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 2: reduce channel length L However, further down scaling requires integration of new materials. Reason: Scaling reduces transistor area A and therefore the insulator capacitance KA C i= d Historically this was counteracted by reducing the insulator thickness d. Also, short channel effects start being a problem. S.Sze, Physics of Semiconductor Devices 34 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 2: reduce channel length L Further thickness reduction of the insulator results in high leakage currents due to quantum mechanic tunneling effect. S.Sze, Physics of Semiconductor Devices 35 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 2: reduce channel length L Replace SiO2 with „high-K“ material. KA C i= d S.Sze, Physics of Semiconductor Devices 36 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 3: Integrate high-K gate oxides to raise Ci. Alternative dielectrics discussed in literature: Amorphous: ZrO2 Al2O3 TiO2 HfO2 HF-Silicates Pr-Silicates Etc. Epitaxial: SrTiO3 Y2O3 Pr2O3 Etc. Polycrystalline: none S.Sze, Physics of Semiconductor Devices 37 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 3: Integrate high-K gate oxides to raise CI. Important requirements for high-K dielectrics: -Reasonable K-value: about 15 ~ 30 -Low leakage currents: Band offset of at least 1 eV -Good breakdown characteristics: time dependent breakdown S.Sze, Physics of Semiconductor Devices 38 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 3: Integrate high-K gate oxides to raise Ci. Important requirements for high-K dielectrics. Problems: -Coulomb scattering due to fixed charges in the dielectric and ionized atoms in depletion layer. - Quantization of inversion charge results in lower effective electric fields - Surface roughness, phonon scattering, interface traps. S.Sze, Physics of Semiconductor Devices 39 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 4: Raise channel width Drawback: → In conventional planar MOSFET technology this approach is not useful as it costs chip area. → New promising device concept: different gate architecture, multiple gates S.Sze, Physics of Semiconductor Devices 40 FinFETs Dielectric 32nm Planar transistors FinFET 22nm Tri-gate transistors Fin Intel.com 41 How to raise the drain current of the MOSFET device VD W I D = µ n C i (V G − V T − ) V D L 2 Strategy 5: Raise the carrier mobility µ → New materials and techniques, such as Strained Si technique (layering of Si(1-x)Gex), Graphene?, MoS2, WS2, CNT, NW etc. S.Sze, Physics of Semiconductor Devices 42 How to raise the drain current of the MOSFET device Another strategy: Replace Silicon for a different channel material. Prominent example: Development of Graphene FETs is improving fast: 43 Nature.com (May 2010)