Differential Amplifier Offset Causes of dc voltage and current offset

advertisement

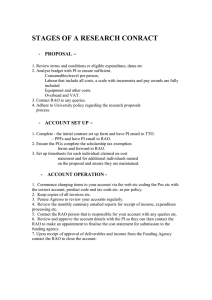

ESE319 Introduction to Microelectronics Differential Amplifier Offset ● ● Causes of dc voltage and current offset Modeling dc offset ● ● ● ● RC mismatch IS mismatch transistor mismatch β mismatch dc offsets in differential amplifiers due to component mismatch can be modeled as differential phenomena Kenneth R. Laker update KRL25Oct13 1 ESE319 Introduction to Microelectronics IC1 VCC IC2 VCC VOdm - V + RC1 RC2 O Q1 Q2 1. Let the ac sources be zero, i.e. the bases of matched Q1 & Q2 are connected to ground. 2. To further simplify, let there be no external base RB and emitter resistors RE. 3. Let the mismatch be in RC where RC1 ≠ RC2. II VEE Since Q1=Q2 and I is fixed, currents are matched i.e. I C1=I C2= I I = 2 1 2 Kenneth R. Laker update KRL25Oct13 V Odm=V C2−V C1= RC1 I C1−RC2 I C2 If V Odm=0⇒ RC1 I C1=R C2 I C2 I I C1= I C2= ⇒ RC1= RC2 2 2 ESE319 Introduction to Microelectronics Let: RC1≠ RC2 s.t. RC2 RC1 Split the mismatch between both collector resistors, and decompose into common and differential components: VOdm I 2 I 2 I RC2 RC1 (common) RC = 2 RC = RC2− RC1 (differential - mismatch) Solving for RC1 & RC2: VEE v id /2 RC 1 RC RC2 =RC =RC 1 2 2 RC v Assume matched currents: ic I −v id /2 RC 1 RC I C1= I C2= RC1= RC − = RC 1− 2 2 2 RC Kenneth R. Laker update KRL25Oct13 3 ESE319 Introduction to Microelectronics Hence : RC RC V Odm= RC I C2− RC − I C1 2 2 VOdm I 2 I 2 I Recall: V Odm=RC2 I C2−R C1 I C1 I I C1= I C2= RC1≠ RC2 2 Kenneth R. Laker update KRL25Oct13 RC RC I I V Odm= RC − RC − 2 2 2 2 or: VEE random variable (rv) I V Odm= RC output offset voltage 2 Iff balanced, RC1 = RC2: V Odm=0V 4 VEE ESE319 Introduction to Microelectronics Collector-collector voltage due to resistor mismatch: VOdm I 2 I 2 I VEE 0V -VOS I 2 I 2 I VEE Kenneth R. Laker update KRL25Oct13 I V Odm= RC 2 Define the input offset voltage as that input voltage that will cancel VOdm. If the amplifier differential gain is Avdm: V Odm VOS is highly variable, V OS ≡ rv & can be + or Avdm Input offset voltage is the output offset voltage referred to the input due to mismatch RC . 5 ESE319 Introduction to Microelectronics I RC 2 V OS = g m RC 0V -VOS I 2 I 2 IC I 1 g m = = VT 2 VT I Input referred offset due to ΔRC V mismatch: random RC variable I V OS R =V T V Odm = RC RC 2 where EE V Odm V OS = A vdm C Avdm=g m R C Kenneth R. Laker update KRL25Oct13 6 ESE319 Introduction to Microelectronics Offset Voltage From Transistor Mismatch Perfect balance requires: V Odm =0⇒ RC1 I C1=RC2 I C2 RC V+Odm - RC I VEE Kenneth R. Laker update KRL25Oct13 Previous case considered RC1 ≠ RC2 & Q1 = Q2 => IC1 = IC2. Consider now Q1 ≠ Q2 => IC1 ≠ IC2. ASSUME: 1. RC1 = RC2 = RC 2. VBE1 = VBE2 3. VT1=VT2 Only difference is in the saturation currents of the transistors, i.e. I S1≠ I S2 7 ESE319 Introduction to Microelectronics Again using common and differential mode concepts: + - V Odm I S2 I S1 I S= 2 I S = I S2− I S1 I VEE Kenneth R. Laker update KRL25Oct13 The two transistor saturation currents are: v ic v id /2 IS I S2= I S 2 −v id /2 IS I S1= I S − 2 8 ESE319 Introduction to Microelectronics I C≈ I S e ICdm/2 I C2 I C1≈ I S1 e V BE VT I C2≈ I S2 e IS = I S− e 2 V BE VT V BE VT V BE IS V = I S e 2 Kenneth R. Laker update KRL25Oct13 ICdm/2 I C1 V BE /V T IS e V BE /V T IS V e 2 − I S V e 2 IS e BE BE /V T /VT Vee V BE /V T T 9 ESE319 Introduction to Microelectronics IS e ICdm/2 V BE /V T IS V e 2 I C2 ICdm/2 − I S V e 2 IS e I C1 I C1≈ I S1 e V BE /V T I C2≈ I S2 e V BE /V T BE Large signal Model: I C1≈ I S e BE V BE VT /VT V BE /V T Kenneth R. Laker update KRL25Oct13 IS I C1≈ I S − e 2 /V T Vee also V BE VT IS − e 2 V BE IS V I C2≈ I S e 2 V BE VT V BE VT T V BE VT IS I C2≈ I S e e 2 The parallel current sources are illustrated in the schematic. 10 ESE319 Introduction to Microelectronics Note: differential IC components cause current flow in opposite directions through the RC's resulting in an offset voltage. The common IC components cause no offset voltage. I C≈ I S e I C2≈ I S e V BE VT V BE VT ≈ IS e 2 IS I I C2≈ 1 2 2IS IS I I C1≈ 1− 2 2IS I 2 V BE VT ≈IS e Kenneth R. Laker update KRL25Oct13 V BE VT IS 1 2IS I IS V Odm=R C I C2−RC I C1≈ RC 2 IS 11 ESE319 Introduction to Microelectronics I IS V Odm≈ RC 2 IS I VT IS V Odm≈ RC 2 VT IS IS V Odm≈ g m V T RC IS V OS I Recall: IC I 1 g m= ≈ VT 2 VT Kenneth R. Laker update KRL25Oct13 S V Odm V Odm IS = ≈V T = Avdm g m RC IS V OS I S IS ≈V T IS random variable 12 ESE319 Introduction to Microelectronics Offset Voltage Summary 1. We considered two sources of offset voltage: a. Unbalanced collector resistors b. Unbalanced saturation currents i. Due to mismatched transistor geometries 2. We ignored base or emitter circuit unbalance 3. Since the relationship between resistor and current unbalances are random and assumed independent, we combine their effect as an rms quantity: 2 2 V OS rms= V OS − R V OS − I =V T Kenneth R. Laker update KRL25Oct13 C S 2 RC IS RC IS 2 13 ESE319 Introduction to Microelectronics Average & Offset Base (input) Bias Currents Consider the case where the base currents differ IB1 ≠ IB2. Since IB1 & IB2 are related to bias current I, I B2 I B1 I I E2 = 2 I I E1 = 2 VEE Kenneth R. Laker update KRL25Oct13 their mismatch may be due to β1 ≠ β2. Let's represent β1 & β2 in terms of differential & common components: v i−cm 1 = 2 2=− 2 v id /2 −v id /2 14 ESE319 Introduction to Microelectronics Using this notation, the two base currents are: 1 I 1 1 = 2 1 2 2 I 1 I 1 I 1 1 I B2≈ = = 2 2 2 2 − 1− 2 2 I B1≈ I 1 I = 2 1 2 nonlinear f(Δβ) For x << 1 we can expand the fraction as the series: 1 =1− x x 2 −x 3 ...≈1−x 1x where x≈ ± 2 Kenneth R. Laker update KRL25Oct13 15 ESE319 Introduction to Microelectronics Using the expansion and approximating 1≈: I 1 1 I B1≈ 1− 2 2 I 1 1 I B2≈ 1 2 2 ∣ ∣ I I OS ≡∣I B1− I B2∣= 2 ¿ (input offset current) I B1 I B2 I Since the input bias current IB is defined as: I B = = 2 2 The base or input offset current can also be written as: I OS = I B Kenneth R. Laker update KRL25Oct13 ∣ ∣ 16 ESE319 Introduction to Microelectronics DC Offset Voltage & Current Summary 1. DC offset voltage and current occur due to mismatches in the BJT differential amplifier external resistors and transistor parameters (Is and β). 2. These mismatches are imperfections that are inherent to all differential amplifiers and their applications (e.g. op amps). 3. DC offset voltage and current are statistical quantities, i.e. no two differential amplifiers will have the same offset voltage and current. 4. MOS differential amplifiers have zero input offset current. Kenneth R. Laker update KRL25Oct13 17