SR latch SR latch behavior

advertisement

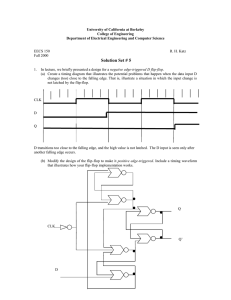

Lecture 14 Memory storage elements Example from last time Latches Flip-flops Door combination lock State Diagrams Inputs: Sequence of numbers, reset, new Outputs: Door open/close Memory: Must remember combination Memory: Must remember current state 1 How do we store information? 2 How do we store information? Feedback Example: Two inverters can hold a bit (as long as power is applied) Storing a new memory Temporarily break the feedback path "remember" "1" "0" "data" "stored bit" "load" "stored bit" What is missing? How do we change the stored bit? 3 SR latch 4 SR latch behavior Cross-coupled NOR gates Can set (S=1, R=0) or reset (R=1, S=0) the output R Q S Q' Reset R Q Set S Q S 0 0 1 1 R 0 1 0 1 R Q S Q' Reset Q hold 0 1 disallow Hold Set S 0 0 1 1 R 0 1 0 1 Q hold 0 1 disallow Reset Set 100 Race R S Q Q' 5 6 SR latch is glitch sensitive State diagrams Static 0 glitches can set/reset latch How do we characterize logic circuits? Glitch on S input sets latch Glitch on R input resets latch First draw the states R 0 Q S States ≡ Unique circuit configurations Second draw the transitions between states Q' 0 Combinational circuits: Truth tables Sequential circuits: State diagrams Transitions ≡ Changes in state caused by inputs 7 Example: SR latch 8 Observed SR latch behavior SR=10 R Q Q Q' 0 1 Q' S S 0 0 1 1 SR=00 SR=01 R 0 1 0 1 Q hold 0 1 disallow SR=01 SR=01 SR=10 SR=11 SR=11 Q Q' 0 0 SR=00 The 1–1 state is transitory Either R or S “gets ahead” Latch settles to 0–1 or 1–0 state ambiguously Race condition → non-deterministic transition SR=11 SR=00 SR=11 SR=10 SR=01 possible oscillation between states 00 and 11 (when SR=00) SR=00 SR=10 Q Q' 1 0 Disallow (R,S) = (1,1) SR=10 SR=00 SR=01 Q Q' 0 1 Q Q' 1 1 Q Q' 1 0 SR=01 9 D ("data") latch Output depends on clock SR=00 SR=10 10 Making a D latch Input Clock high: Input passes to output Clock low: Latch holds its output D Q Q CLK D CLK CLK D R Q S Q D Qlatch 11 12 D flip-flop Input sampled at clock edge Input D Q Q Rising edge: Input passes to output Otherwise: Flip-flop holds its output Master-slave D-type flip-flop Master D latch Slave D latch X D Input CLK Flip-flops can be rising-edge triggered or falling-edge triggered Q D Q Output CLK CLK D Qff 13 Latches versus flip-flops D Q How to make into negative edgetriggered D-type flip-flop? 14 Terminology and notation Rising-edge triggered D flip-flop CLK Input Q D D Q Output Q Output Positive D latch Input D Q Output Q Output CLK D Q Q CLK Qlatch Falling-edge triggered D flip-flop Input D CLK behavior is the same unless input changes while the clock is high 15 How to make a D flip-flop? Label the internal nodes Draw a timing diagram Start with Clk=1 Output Q Output Negative D latch Input CLK D Q Output Q Output CLK 16 Falling edge-triggered flip-flop If Clk=1 then X=Y=0 and SR latch block holds previous values of Q,Q’, also Z=D’ and W=Z’=D. W X Q Clk Q’ Y D Q How to make a D flip flop? Edge triggering is difficult CLK Qff Z 17 W X Q When Clk→ → 0 then Y (set for SR latch block) becomes Z’=D and X (reset for SR latch Clk block) becomes W’=D’ so Q becomes D. Q’ Y While Clk=0, if D switches then Z becomes 0 (because inputs to Z are D and D') and X and D W hold their previous values and Y=X’=D as before. Z 18 T ("toggle") flip-flop Output toggles when input is asserted If T=1, then Q → Q' when CLK ↑ If T=0, then Q → Q when CLK ↑ Input T Q > CLK Q Input(t) 0 0 1 1 Q(t) 0 1 0 1 Q(t + ∆t) 0 1 1 0 19