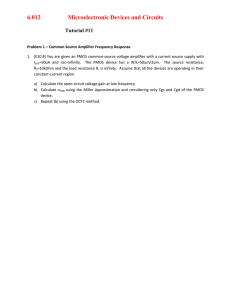

7. Complementary MOS (CMOS) Logic Design

advertisement

7. Complementary MOS (CMOS) Logic Design Institute of Microelectronic Systems Basic CMOS Logic Gate Structure VDD • PMOS and NMOS switching networks are complementary ⇒Either the PMOS or the NMOS network is on while the other is off PMOS Switching Network Logic Inputs Y NMOS Switching Network ⇒No static power dissipation 7: CMOS Logic Institute of Microelectronic Systems 2 CMOS NOR Gate VDD = 5 V VDD = 5 V 10 1 MP v 5 1 I 10 1 vo MN 2 1 Z A 2 1 B AB 2 1 7: CMOS Logic NOR Gate Truth Table 0 0 1 1 0 1 0 1 Z=A+B 1 0 0 0 Institute of Microelectronic Systems 3 Transistor Sizing for CMOS Gates: Review Goal: To maintain the delay times equal the reference inverter design under the worst-case input conditions Example: 2 input CMOS NOR gate - Each transistor of the NMOS network is capable of discharging individually the load capacitance C ⇒ Same size as NMOS transistor of reference inverter - PMOS network conducts only when AB = 00 (Transistors in serie) ⇒ Each PMOS must be twice larger ( On-resistance proportional to (W/L)-1 ) 7: CMOS Logic Institute of Microelectronic Systems 4 CMOS NAND Gate NAND Gate Truth Table V =5V DD AB 5 1 5 1 DD 5 1 M 4 1 P v A 0 0 1 1 V =5V Z v I M 4 1 0 1 0 1 Z = AB 1 1 1 0 O 2 1 N B Institute of Microelectronic Systems 7: CMOS Logic 5 Multi-Input NAND Gate V 5 1 5 1 =5V DD Y= ABCDE 5 1 5 1 5 1 Y Y 10 1 C A 10 1 Why should one prefer a NAND gate rather than a NOR gate? B 10 1 C 10 1 10 1 7: CMOS Logic D E Institute of Microelectronic Systems 6 Steps in Constructing Graphs for NMOS and PMOS Networks (I) +5 V A B C D PMOS Switch Network Y MB B B (C + D) MA A MC C MD D C+D Y = A + B (C + D) A + B (C + D) Institute of Microelectronic Systems 7: CMOS Logic 7 Steps in Constructing Graphs for NMOS and PMOS Networks (II) +5 V 3 A B C D (d) Graph with PMOS Switch Network PMOS Arcs Added Y 2 (a) B 1 A MA MC C 2 1 4 A C 1 4 D 4 1 0 3 (c) NMOS Graph with New Nodes Added 2 2 B B (b) NMOS Graph 3 1 A 2 C A 4 C D 0 7: CMOS Logic 2 5 MD D 4 1 0 1 B 3 4 1 MB 2 1 2 5 D Institute of Microelectronic Systems 0 8 Steps in Constructing Graphs for NMOS and PMOS Networks (III) Final CMOS Circuit +5 V 15 1 3 A 4 Graph with PMOS Arcs Added 2 B 7.5 1 B 3 4 A C 1 15 1 C 4 2 5 15 1 D 5 2 D Y 0 B MB 1 MA A MC D 4 1 C 2 1 4 1 MD 4 1 Institute of Microelectronic Systems 7: CMOS Logic 9 Summary +5 V 15 1 A • AND - serially connected FET • OR - parallel connected FET • NMOS network implements “zeros” • PMOS network implements “ones” C 15 1 D 15 1 7.5 1 B Y • W/L ratio has to be determined as a design parameter B A MA C 2 1 7: CMOS Logic Institute of Microelectronic Systems MB MC D 4 1 4 1 MD 4 1 10 CMOS Gate Design: Minimum Size Vs. Performance (I) Considerable savings in chip area, but increased logic delay CMOS circuit with only minimum size transistors Example: Institute of Microelectronic Systems 7: CMOS Logic 11 CMOS Gate Design: Minimum Size Vs. Performance (II) (W/L) for PMOS network = 2/3 τ PLHI =τ PLH For NMOS network τ PLH ⎛5⎞ ⎜ ⎟ 1 = ⎝ ⎠ τ PLHI = 7 . 5 τ PLHI ⎛2⎞ ⎜ ⎟ ⎝3⎠ of reference inverter τ PHL = 2τ PHLI The average propagation delay of the minimum size logic gate is: τP = (τ PHL + τ PLH ) = (2 τ PHLI 2 + 7 .5 τ PLHI ) 9 .5 τ PLHI = = 4 .75 τ PLHI 2 2 Mininimum size gate will 4.75 times slower than reference inverter when driving the same load capacitance 7: CMOS Logic Institute of Microelectronic Systems 12 Power-Delay Product (PDP) The PDP is an important figure of merit for a logic technology PDP = PAV τ P For CMOS: P AV = CV 2 DD f with f = 1 T CMOS switching waveform Institute of Microelectronic Systems 7: CMOS Logic 13 Power-Delay Product (cont’d) • The period T must satisfy: T ≥ tr + ta + t f + tb • Assumptions: At high frequencies ta → 0 and tb → 0, tr and tf account for approximately 80 % of the total transition time For symmetrical inverter: T ≥ 2 t r 2 (2τ P ) = = 5τ P 0 .8 0 .8 2 2 CV DD CV DD τP = PDP ≤ 5τ P 5 7: CMOS Logic Institute of Microelectronic Systems 14