ECE 651 Advanced VLSI System Design

advertisement

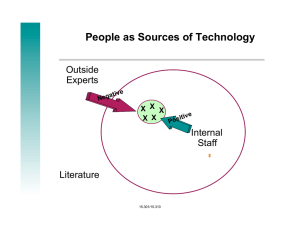

ECE 651 Advanced VLSI System Design Fall 2015 Jeremy Holleman What are we doing? • Two basic sets of topics for this class • Advanced digital VLSI techniques – How to design digital circuits to be faster, smaller, lower-­‐power, more reliable, and beMer looking • CAD Techniques – How to make a computer do all that for you – Automate other design tasks as well (simulaPon, analog layout, rouPng) Why would we do that? To make money • An adequate, competent engineer is vulnerable to layoffs, offshoring, or replacement by smarter, cheaper CAD tools – “Adequate performance gets a generous severance package.” -­‐ NeWlix HR PresentaPon • An excepPonal engineer will generally be retained and o[en be given special consideraPon • In the long run, earnings ~ producPvity – Be more producPve hMp://www.slideshare.net/reed2001/culture-­‐1798664/22-­‐ Unlike_many_companies_we_pracPce Why would we do that? To perform research here at UTK • Most complex systems include some digital components • Time and effort are limited resources. CompePPve system demonstraPons require efficiency To focus on the fun parts • Most IC designs include some tedious, repePPous, uninteresPng work – Could a computer do this for you? Increasing Chip Complexity MIXED-­‐SIGNAL APPLICATIONS ARE BEING TARGETED FOR SYSTEM-­‐ON-­‐CHIP INTEGRATION Cellular phone on PCBs becoming a software radio SOC Jan Rabaey U.C. Berkeley jan@eecs.berkeley.edu http://bwrc.eecs.berkeley.edu Increasing Chip Complexity HETEROGENEOUS RECONFIGURABLE SYSTEM-­‐ON-­‐A-­‐CHIP ARM8 Rich Brown Univ. of Michigan brown@engin.umich.edu http://www.eecs.umich.edu/~brown DESIGN FOR REUSE IS NOT FREE BUT CAN HAVE A SIGNIFICANT IMPACT Design #1 without Planned Reuse Design #2 without Planned Reuse Design # 1 WITH Planned Reuse IP are often not blocks with well-defined interfaces Design #2 WITH IP Design #3 without Planned Reuse Design #3 WITH IP but instead are patches that must be stitched together like a quilt How will we do it? • I’ll do some, you’ll do some • Most VLSI design topics will be presented in standard lecture format and covered by homework and quizzes – ExcepPons possible • Most CAD topics will be covered by you – Students will research methods and present them to the class – In class presentaPons + on-­‐line documentaPon with video or tutorial walk-­‐through • Video vs. tutorial document – Thoughts? How will we do it? • Homeworks – Varying scale, including some design work, e.g. “build an 8-­‐bit mulPplier” – Almost certainly possible. Known or nearly known soluPon • Journal paper report – Read a journal paper on a relevant topic. Present a 20-­‐minute cri$cal summary of the work • Student-­‐led invesPgaPons of CAD topics – You will learn a technique and present it to the class. – Also capture it to wiki How will we do it? • Development Projects – Some combinaPon of design work and CAD tool development – Ex: AMS/RF Cell generator (e.g. automated RF LNA generator). – Will typically involve some development risk; won’t know at outset whether it is possible. – IEEE-­‐formaMed project report + class presentaPon + documentaPon on wiki Details -­‐ Tools & Technology • Tools: Cadence, Synopsys, possibly others • Technology: You can choose the process you use for class projects and assignments, within some limits – No ITAR/export-­‐controlled processes. Other students and I will be viewing your work and we cannot accommodate ITAR or similar restricPons – A PDK based on Cadence IC6 is strongly recommended Tools & Technology, cont. • Technology, cont. – Everyone will sign MOSIS NDAs. (right now) – So MOSIS processes are OK. • IBM 8RF and 7RF are good choices • PotenPal for 7RF fabricaPon. Interest? Topics – VLSI Design High-­‐performance data path Clock Trees, SynchronizaPon issues I/O and Intra-­‐chip communicaPon Reliability Power distribuPon Low-­‐voltage/subthreshold logic AlternaPve Logic Families Asynchronous digital Systems Design of programmable logic Somewhat OpPonal Topics – CAD Techniques Synthesis w/ place and route WriPng P-­‐Cells Verilog/VHDL -­‐ coding for synthesis AutomaPc cell generaPon Mixed-­‐Signal, System-­‐level simulaPons AutomaPcally characterizing cells/libraries ScripPng simulaPon Extending Synthesizer’s Module Library EsPmaPng power Semi-­‐automated rouPng AutomaPng analog layout AutomaPc metal fill Testbench creaPon Linking to external tools At the end you should be able to • Automate analog layout • Efficiently implement and verify complex mixed-­‐signal ICs E.g. uC + SRAM + amp + ADC • Make computers do boring tasks, so you can focus on the innovaPve part of research • Learn new materials on your own and convey them to others Class Structure • Homeworks • Journal Reviews – 20-­‐minute criPcal rev