MOSFET transistor I

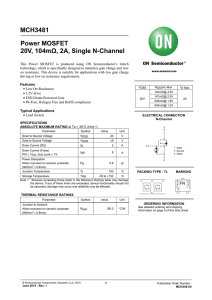

advertisement

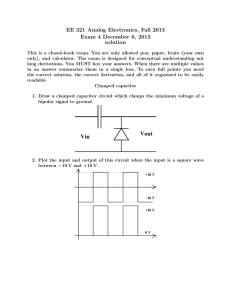

MOSFET transistor I-V characteristics K n = C ox µ n Linear region: i = K [ 2 ( v – V )v ] D GS t DS v DS « v GS – V t W K = ------K n 2L 2 Triode region: i D = K [ 2 ( v GS – V t )v DS – v DS ] v DS < v GS – V t v DS sat = v GS – V t (current) Saturation region: i = K [ ( v – V ) 2 ] ( 1 + λv ) D GS t DS v DS ≥ v GS – V t iD + v GS - + v DS - Lecture 20-1 Is the transistor in saturation region? v DS sat = v GS – V t V t = 1V V D = 3.5V V G = 4V V D = 3.5V VG = V S = 2V V S = 2V Lecture 20-2 Body Effect • The source and bulk will not be at zero volts all of the time • The p-type bulk will be connected to the lowest supply voltage for an IC • Discrete MOSFETs may have bulk tied directly to the source • But for ICs we can assume that there can be a positive VSB for NMOSFETs VS2B=0 VS1B=0 VS2>0 VS2B>0 VB VS1B=0 Lecture 20-3 Body Effect • Positive VSB for NMOSFETs tends to increase QB, hence decrease QI, for a fixed VGS VGS > Vt VDS > 0 VS>0 + n+ QI QB0 n+ VB Lecture 20-4 Body Effect • Modeled as a change in the threshold voltage as a function of VSB • The source is, by definition for NMOSFET, at a lower positive potential than the drain, which is why we use it as our reference voltage V t = V t0 + γ ( 2φ f + V SB – 2φ f ) • SPICE will calculate this variation in threshold voltage, or you can over-ride its calculation by directly specifying gamma Lecture 20-5 Temperature Variations • The threshold voltage varies with temperature due to carrier generation in the substrate --- tends to decrease with increasing temperature •~2mV for every 1ºC increase V t = V t0 + γ ( 2φ f + V SB – 2φ f ) • K also changes with temperature due to change in mobility •Tends to dominate temperature variation for large iD 2 W 1 I ∝ --- µ n C ----- ( v GS – V t ) ox L 2 • Will iD increase or decrease with temperature? T1 T2 > T1 Lecture 20-6 Where is drain, where is source? S D G B S n-channel transistor G B D p-channel transistor Lecture 20-7 PMOSFETs • All of the voltages are negative • Carrier mobility is about half of what it is for n channels S p+ G D p+ n B • The bulk is now connected to the most positive potential in the circuit • Strong inversion occurs when the channel becomes as p-type as it was n-type • The inversion layer is a positive charge that is sourced by the larger potential and drained at the smallest potential • The threshold voltage is negative for an enhancement PMOSFET •Note that the flatband voltage (which is negative) effects now tend to increase the PFET threshold while they decreased the NFET threshold Lecture 20-8 PMOS • The equations are the same, but all of the voltages are negative • Triode region: v GS ≥ V t v DS ≤ v GS – V t 2 W 1 K = --- µ n C ox ----L 2 i D = K [ 2 ( v GS – V t ) v DS – v DS ] A ------2 V • iD is also negative --- positive charge flows into the drain • Saturation expression is the same as it is for NFETs: +V dd iD 2 sat = K [ ( v GS – V t ) ] ( 1 + λ v DS ) Lecture 20-9 PMOS • Characteristic appears to be the same, except that all of the voltages are negative -5 -4 -3 -2 -1 VDS 0 10 0 IDS (µA) -10 VGS=-1.0V VGS=-1.5V -20 -30 VGS=-2.0V -40 -50 -60 W=1 micron L=1 microns V t0= -1 volt 2 K p=2e-5 (A/v ) phi =-0.6 N D=1e15 VGS=-2.5V -70 -80 -90 VGS=-3.0V -100 Lecture 20-10 PMOS • But it is generally displayed as: -VDS 0 1 2 3 4 5 100 90 VGS=-3.0V -IDS (µA) 80 70 60 VGS=-2.5V 50 40 30 VGS=-2.0V W=1 micron L=1 microns V t0= -1 volt 2 K p=2e-5 (A/v ) phi =-0.6 N D=1e15 20 10 0 VGS=-1.5V VGS=-1.0V -10 Lecture 20-11 Depletion Mode NMOSFET • Depletion mode FETs have a channel implanted such that there is conduction with VGS=0 • The operation is the same as the enhancement mode FET, but the threshold voltage is shifted •Vt is negative for depletion NMOS, and positive for depletion PMOS VGS VDS VS n+ n+ n+ p Lecture 20-12 Depletion Mode NMOSFET • Negative gate voltage is required to turn the channel off 0 1 2 3 4 VDS 5 IDS (mA) 0.4 VGS=2.0V VGS=1.0V 0.2 W=1 micron L=1 microns V t0= -2 volt 2 K p=2e-5 (A/v ) VGS=0.0V VGS=-1.0V 0.0 VGS=-2.0V Lecture 20-13 Depletion Mode NMOSFET • The iDS vs. vGS characteristic is still quadratic in saturation VGS -4 -3 -2 -1 0 1 2 3 4 5 IDS (mA) 2 W=1 micron L=1 microns V t0= -2 volt 2 K p=2e-5 (A/v ) 1 0 Lecture 20-14 Examples • Find the largest value that RD can have before the transistor fails to operate in saturation 5V V t = 2V RD K n = 20µ A ⁄ V 2 L = 10µm W = 400µm λ = 0 5kΩ -5V Lecture 20-15 Examples • Find the drain currents and voltages for both transistors 10V 10kΩ 10V 15kΩ V t = 2V K n = 20µ A ⁄ V 2 L = 10µm M2 M1 W = 100µm λ = 0 Lecture 20-16 Examples • What is the effective resistance of the transistor in the triode region? 10V 24.8kΩ V t = 1V K = 0.5m A ⁄ V 2 Lecture 20-17 Examples • Select the R’s so that the gate voltage is 4V, the drain voltage is 4V and the current is 1mA. 10V 10V V t = 2V RG1 RD K = 1m A ⁄ V 2 λ = 0 RG2 RS Lecture 20-18 Examples • Select the R’s so that the transistor is in saturation with a drain current of 1.0mA and a drain voltage of 5V 10V RG1 V t = –1 V K = 0.5m A ⁄ V 2 λ = 0 RG2 RD Lecture 20-19 Examples • Solve for the drain current and voltage 20V 32kΩ V t = –2 V K = 1m A ⁄ V 2 λ = 0 10MΩ 4kΩ Lecture 20-20