Incremental Elaboration of Scenario

advertisement

Incremental Elaboration of Scenario-Based

Specifications and Behavior Models Using

Implied Scenarios

SEBASTIAN UCHITEL, JEFF KRAMER, and JEFF MAGEE

Department of Computing, Imperial College

Behavior modeling has proved to be successful in helping uncover design flaws of concurrent and

distributed systems. Nevertheless, it has not had a widespread impact on practitioners because

model construction remains a difficult task and because the benefits of behavior analysis appear

at the end of the model construction effort. In contrast, scenario-based specifications have a wide

acceptance in industry and are well suited for developing first approximations of intended behavior;

however, they are still maturing with respect to rigorous semantics and analysis tools.

This article proposes a process for elaborating system behavior that exploits the potential benefits of behavior modeling and scenario-based specifications yet ameliorates their shortcomings. The

concept that drives the elaboration process is that of implied scenarios. Implied scenarios identify

gaps in scenario-based specifications that arise from specifying the global behavior of a system that

will be implemented component-wise. They are the result of a mismatch between the behavioral

and architectural aspects of scenario-based specifications. Due to the partial nature of scenariobased specifications, implied scenarios need to be validated as desired or undesired behavior. The

scenario specifications are then updated accordingly with new positive or negative scenarios. By

iteratively detecting and validating implied scenarios, it is possible to incrementally elaborate the

behavior described both in the scenario-based specification and models. The proposed elaboration

process starts with a message sequence chart (MSC) specification that includes basic, high-level

and negative MSCs. Implied scenario detection is performed by synthesis and automated analysis of behavior models. The final outcome consists of four artifacts: (1) an MSC specification that

has been evolved from its original form to cover important aspects of the concurrent nature of the

system that were under-specified or absent in the original specification, (2) a behavior model that

captures the component structure of the system that, combined with (3) a constraint model and (4)

a property model that provides the basis for modeling and reasoning about system design.

Categories and Subject Descriptors: D.2.1 [Software Engineering]: Requirements/Specifications—elicitation methods; D.2.2 [Software Engineering]: Design Tools and Techniques—state

diagrams; D.2.4 [Software Engineering]: Software/Program Verification—model checking, validation; F.3.1 [Logics and Meaning of Programs]: specifying and Verifying and Reasoning about

Programs—mechanical verification, specification techniques

This research was supported by the European Union under grant STATUS (1ST-2001-32298) and

EPSRC under grant READS GR/S03270/01.

Authors’ address: Department of Computing, Imperial College, 180 Queen’s Gate, London, SW7

2BZ, UK; email: {s.uchitel,jnm,jk}@doc.ic.ac.uk.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is

granted without fee provided that copies are not made or distributed for profit or direct commercial

advantage and that copies show this notice on the first page or initial screen of a display along

with the full citation. Copyrights for components of this work owned by others than ACM must be

honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers,

to redistribute to lists, or to use any component of this work in other works requires prior specific

permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 1515

Broadway, New York, NY 10036 USA, fax: +1 (212) 869-0481, or permissions@acm.org.

°

C 2004 ACM 1049-331X/04/0100-0037 $5.00

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004, Pages 37–85.

38

•

S. Uchitel et al.

General Terms: Design, Documentation, Languages, Theory, Verification

Additional Key Words and Phrases: MSC, implied scenarios, negative scenarios, LTSA

1. INTRODUCTION

1.1 Motivation

The design of the concurrent and distributed software is a complex task prone

to subtle errors that can have serious consequences [Clarke and Wing 1996].

Behavior models are precise, abstract descriptions of the intended behavior of

a system that can be used to support rigorous analysis and mechanical verification of properties. Effective techniques and tools have been developed for this

purpose and have shown that behavior modeling and analysis are successful in

uncovering the design flaws [Clarke and Wing 1996; Cleaveland and Smolka

1996]. Although there is substantial benefit to be gained in using behavior

models for developing complex system, industry has been slow in assimilating

behavioral modeling and verification technologies. Practitioners are not convinced that the benefit of rigorous and automated analysis justifies the cost of

constructing such models. We believe the reasons for this are twofold. Firstly,

the construction of behavior models remains a difficult task that requires considerable expertise in behavior model notations. Secondly, and perhaps more

importantly, the benefits of behavior analysis appear at the end of the considerable effort of constructing behavior models. Behavior analysis and verification

techniques have been developed under the assumption that a comprehensive

description of the system behavior (up to some level of abstraction) has been

constructed. Thus, they are generally not well suited for providing early feedback on partial system descriptions.

Scenario-based specifications, such as message sequence charts (MSCs) [ITU

1996] and UML sequence diagrams [OMG 2002], are popular as part of requirements specifications. Scenarios describe how system components, the environment and users work concurrently and interact in order to provide system

level functionality. Their simplicity and intuitive graphical representation facilitates stakeholder involvement and makes them popular for conveying and

documenting requirements. Each scenario is a partial description that, when

combined with all other scenarios contributes to the overall system description.

Although scenarios are widely used in industry, their use is mainly informal,

with no precise semantics associated with the scenario description (e.g., [Carrol

1995; Harmon and Watson 1998; Jacobson et al. 1999]). Consequently, analysis techniques and tools have restricted applicability, often limited to syntactic

consistency checks (e.g., Rational [2002]). Of course, there has been work on providing precise semantics to scenario-based specifications (e.g., Heymer [2000],

ITU [1996], Katoen and Lambert [1998], and Reniers [1999]) and developing

semantic analysis tools (e.g., Ben-Abdhallah and Leue [1998], Holzmann et al.

[1997], and Wakahara et al. [1989]). However, the main tendency has been to

view scenario-based specifications no differently than other behavior specification languages. Yet there is a fundamental difference. Scenario specifications

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

39

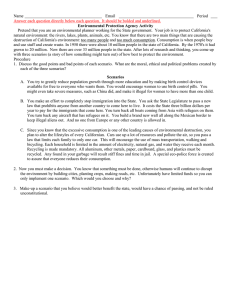

Fig. 1. A scenario for the Boiler Control system.

naturally result in partial descriptions. They depict a series of examples of

what the system is expected to do. In the best of cases, these examples cover

most common system behaviors and main exceptions. Expecting stakeholders

to produce, in one go, a set of scenarios that covers all possible system traces is

unrealistic, impractical and in general intractable. Thus, existing analysis tools

and techniques developed under the assumption of complete (or even relatively

complete) specifications cannot tackle the partial nature of such specifications.

They do not detect gaps in the specification that, if not elaborated, could result

in costly errors later on in the development process.

The main contribution of this article is a process for incremental behavior

elaboration. The process we present supports elaboration of behavior models in

conjunction with scenario-based specifications that include positive and negative scenarios. Scenario-based specifications and behavior models are complementary and provide alternative views of how system components interact.

Scenario specifications are still maturing with respect to rigorous semantics

and analysis tools, yet have a wide acceptance in industry and are well suited

for preliminary, partial descriptions of system behavior. Behavior models have

not had such a widespread impact on practitioners; nevertheless they boast

an important mathematical foundation, effective tools for behavior analysis,

and have proven success in uncovering flaws in fully developed system models.

There is a need to balance the benefits and the shortcomings.

The key concepts on which our contribution builds on are those of implied

scenarios and realizability. These concepts were first introduced by Alur et al.

[2000], and have led to a significant body of work some of which we discuss in the

Discussion section of this article. The problem underlying the notions of implied

scenarios and realizability relates to other notions such as nonlocal choice [BenAbdhallah and Leue 1997] and has been studied in settings such as procotol

synthesis [Saleh 1996]. We also discuss these relations in the Discussion section

of this article. A key assumption on which our process relies on is that the

scenario-based specifications provided by users determine regular languages.

1.2 Implied Scenarios

Scenario notations such as MSCs (see Figure 1) describe two distinct aspects

of a system. First, they depict a series of examples of what constitutes acceptable system behavior. These examples consist of sequences of messages—called

traces—that system components are expected to send each other. Second, scenario notations outline the high-level architecture of the system. Scenarios

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

40

•

S. Uchitel et al.

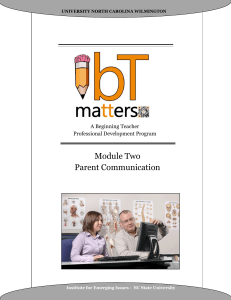

Fig. 2. The scenario and behavior model elaboration process.

depict with vertical arrows, or instances, which system components are involved

in providing the intended system behavior. They also describe component interfaces because they illustrate which messages are being sent and received by

each component. In this article, by architecture, we mean the system components and their interfaces.

Implied scenarios indicate gaps in a scenario-based specification that are

the result of specifying the behavior of a system from a global perspective yet

expecting the behavior to be provided in a local component-wise fashion by

independent entities with a local view of the system. If the specified architecture

does not provide components with a rich enough local view of what is happening

at a system level, components may not be able to enforce the intended system

behavior. Effectively, what may occur is that each component may, from its local

perspective, believe that it is behaving correctly, yet from a system perspective

the behavior may not be what is intended. Traces resulting from the inadequate

local view of components are called implied scenarios.

1.3 An Elaboration Process

Given that scenario-based specifications are partial system descriptions, it

would be erroneous to assume implied scenarios necessarily indicate incorrect

behavior. An implied scenario may simply mean that an acceptable scenario

has been overlooked and that the scenario specification needs to be completed.

Adding the implied scenario results in the partial description of system behavior

being extended. Alternatively, the implied scenario may represent unacceptable

behavior and therefore require careful documentation of the undesired situation so that it can be avoided when further elaborating the system specification

and implementation. Ultimately, the decision of whether to accept or reject

an implied scenario depends on the problem domain, and should therefore be

validated by stakeholders. Consequently, by detecting and validating implied

scenarios it is possible to drive the elaboration of scenario-based specifications.

Figure 2 depicts the elaboration process we present in this article. The bottom portion shows the validation of implied scenarios with stakeholders, while

the top portion describes how implied scenarios are detected. The left portion

of the diagram refers to the scenario language used in our approach. We use an

extended MSC language comprised of two parts: a positive part (PSpec) that

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

41

specifies the intended system behavior and a negative part (NSpec) that specifies the behaviors that the system is expected not to exhibit. The semantics of

our MSC language determines a set of traces for each part. We use L(PSpec) and

L(Nspec) to denote the sets of traces determined by the positive and negative

parts of the specification.

From the MSC specification, we synthesize three different behavior models

in the form of labeled transition systems (LTS) [Keller 1976] where transitions

are labeled with the messages that components send to each other. The first

is an architecture model, which is synthesized using the positive system traces,

L(PSpec), and architectural information of the MSC specification. The architecture model (A) is constructed as the parallel composition of components models

A1 , . . . , An where the alphabet of Ai coincides with the interface of component

i (the set of message labels that the instance can send and receive). Thus, we

have A = (A1 k · · · kAn ) where k is the LTS parallel composition operator, and

L(PSpec) ⊆ L(A) where L(A) is the set of maximal traces exhibited by LTS

A (Maximal traces correspond to infinitely long executions of A, or executions

that end in states with no outgoing transitions). In addition, A can be proven to

be the minimal model (with respect to trace inclusion) that complies with the

MSC architecture and that includes all the specified traces (L(PSpec)). Hence,

any behavior exhibited by the architecture model that has not been specified

explicitly in the MSC specification is an implied scenario (i ∈ L(A)\L(PSpec)).

The second behavior model we build is the trace model (T ). This model is

built from the set of positive system traces (L(PSpec)), ignoring the specified

architecture, such that L(T ) = L(PSpec). A key assumption on which this construction relies is that PSpec determines a regular language; more specifically,

it is a bounded [Alur and Yannakakis 1999], finitely generated MSC [Henriksen

et al. 2000]. Details on this are given in the following sections.

The third behavior model we build is the constraint model (C). This is built

from the set of negative system traces (L(NSpec)) so that it captures the complement of the traces the system should not exhibit: L(C) = L(NSpec)−1 .

We are interested in maximal traces that are exhibited by the architecture model (A), that have not been specified in the positive part of the MSC

specification (L(PSpec)) and that have not already been explicitly rejected by

stakeholders and hence included in the negative part of the MSC specification

(L(NSpec)). Thus, we are interested in the following set of implied scenarios:

(L(A)\L(NSpec))\L(PSpec). This amounts to model checking if L(AkC) ⊆ L(T )

holds, which we do using the LTSA tool [Magee and Kramer 1999]. If the

inclusion does not hold the tool produces the prefix of an implied scenario

(i ∈ (L(A)\L(NSpec))\L(PSpec)) up to the point where it deviates from specified

behavior. In fact, it produces a prefix that corresponds to an implied scenario

that deviates from L(PSpec) in the least number of messages. In accordance

with the outcome of implied scenario validation, the positive or negative part

of the scenario specification is updated.

Four artifacts are produced as a result of the incremental elaboration process.

The first is a MSC specification that has been evolved from its original form to

cover further aspects of the concurrent nature of the system being described,

including possible functional aspects. The second is the architecture model,

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

42

•

S. Uchitel et al.

which preserves the system architecture and provides the specified positive

behavior; however, it may exhibit additional unspecified behavior. The third

is the trace model, which captures precisely the traces specified as positive

behavior. The fourth is the constraint model, which captures the properties

that the architecture model should comply with if it is to avoid the negative

scenarios and provide only the specified system behavior.

The architecture model provides the basis for modeling and reasoning about

system design. In fact, it is the model that needs to be further developed through

architectural and design decisions as designers move towards implementation.

The constraint model aids the design process as it models the properties that

the architecture model must satisfy.

Note that our approach focuses on elaboration of system behavior, and in

particular in using implied scenarios to do so. Behavior elaboration could also be

driven by additional concepts such as safety and liveness properties. In addition,

we do not focus on supporting elaboration of the architecture of the system, such

as supporting changes in the system decomposition and component interfaces.

We discuss the limitations of our approach in Section 8.

1.4 Outline of the Article

In this article, we present both the theoretical and practical aspects involved

in using implied scenarios for the elaboration of scenario-based specifications

and behavior models. All aspects are first illustrated using a toy example based

on a Boiler Control system. In Section 2, we present a scenario-based specification language that includes basic and high-level MSCs. We adopt standard

partial order semantics with synchronous component communication for basic

MSCs and standard weak sequential composition for high-level MSCs. We then

discuss architecture models (Section 3), implied scenarios (Section 4) and how

to detect them (Section 5). In Section 6, we motivate and present a negative

scenario notation. With all elements of the process in place, we then present an

in-depth case study (Section 7). In Section 8, we present an extensive discussion

and evaluation that includes related work and our own previous work. Finally,

Section 9 presents the conclusion and related work.

2. MESSAGE SEQUENCE CHARTS

In this section, we describe a message sequence chart (MSC) language. We

introduce a simple example that is used to illustrate our approach. The example

is based on a Boiler Control system where a Control unit operates a Sensor

and an Actuator to control the pressure of a steam boiler. A Database is used

as a repository to buffer Sensor information while the Control unit performs

calculations and sends commands to the Actuator.

The language is a syntactic subset of the International Telecommunication

Union (ITU) standard for MSCs [ITU 1996]. A basic MSC (bMSC) describes

a finite interaction between a set of components (see Figure 1). Each vertical

arrow represents a component and is called an instance. Arrow must be horizontal and represents messages, the arrow source on one instance corresponds

to a message output and its target on a different instance corresponds to a

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

43

message input. We refer to message outputs and inputs as events. In addition,

we use the terms instance and component interchangeably. The formal definition of bMSCs is presented below. Note that a message label uniquely identifies

the sending and receiving component.

Definition 1 (Basic Message Sequence Charts). A basic message sequence

chart (bMSC) is a structure b = (E, L, I, M, instance, label, order) where: E is

a countable set of events that can be partitioned into a set of send and receive

events that we denote send(E) and receive(E). L is a set of message labels. We

use α(b) to denote L. I is a set of instance names. M : send(E) → receive(E)

is a bijection that pairs send and receive events. We refer to the pairs in M

as messages. The function instance: E → I maps every event to the instance

on which the event occurs. Given i ∈ I , we denote {e ∈ E | instance(e) = i}

as i(E). The function label: E → L maps events to labels. We require for all

(e, e0 ) ∈ M that label(e) = label(e0 ), and if (v, v0 ) ∈ M and label(e) = label(v),

then instance(e) = instance(v) and instance(e0 ) = instance(v0 ). order is a set of

total orders ≤i ⊆ i(E) × i(E) with i ∈ I and ≤i corresponding to the top-down

ordering of events on instance i.

The semantics of a bMSC is given by a set of sequences of message labels

or traces. The set of traces of a bMSC is determined by the top-down ordering of events in the chart. Contrary to the ITU interpretation of messages,

where asynchronous communication is assumed, we consider messages to be

synchronous, that is, message send and receive events are blocking. Note that

the introduction of bounded asynchronous communication can be modeled by

introducing buffer abstractions to decouple the message passing.

Definition 2 (Partial Ordering of Events). Given a bMSC (E, L, I, M, instance, label, order) where order is the set of total orders S

≤i , we define the

preorder ≺ ⊆ E × E to be the reflexive-transitive closure of i∈I ≤i ∪M ∪ M −1

and the preorder < ⊆ send(E)× send (E) to be the restriction of ≺ to elements

of send(E).

A bMSC is valid when no message arrows cross each other (this is equivalent

to requiring arrows to be horizontal in the bMSC diagram) and events are not

superimposed at the same point of an instance. This is equivalent to requiring

that the partial ordering < of a bMSC should not have different events mutually

precede each other (if e 6= e0 , then not (e0 < e and e0 < e)). In the remainder of

this article, we assume all bMSCs are valid.

As communication is considered synchronous, we can consider send and receive events of the same message to occur simultaneously. Thus, in the semantics, we can restrict the partial order to only send-events. In the case of Figure 1,

the bMSC semantics determines a set of two traces: <on, pressure, pressure,

query, data, command, pressure, off> and <on, pressure, pressure, query, data,

pressure, command, off>. Note that the difference between the two traces is

that the command message and the last pressure message appear in different

order. This is because their send events are not causally related in the scenario’s

partial ordering of events. According to the definitions, both must occur after

the sending (and receiving) of message data but before sending (and receiving)

message off.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

44

•

S. Uchitel et al.

Fig. 3. MSC specification for the Boiler Control system.

Definition 3 (Linearizations). Let b = (E, L, I, M , instance, label, order) be

a bMSC and < its partial ordering of events. A word l 1 , l 2 , . . . over the alphabet

L is a linearization of b only if there is a total ordering s1 , s2 , . . . of send(E) such

that si < s j implies i < j and label(si ) = l i for 0 ≤ i, j ≤ |send(E)|.

Definition 4 (bMSC Semantics). Given a bMSC b, we define the language

of b as a set L(b) of traces where L(b) = {w | w is a linearization of b}.

A high-level MSC (hMSC) provides the means for composing bMSCs. It is a

directed graph where nodes represent bMSCs and edges indicate their possible

continuations (see bottom right of Figure 3). hMSCs also have an initial node,

which is indicated using an arrow with a black filled circle as its tail. The ITU

standard includes hMSCs and permits hierarchies by allowing nodes to refer

to a new hMSC. To simplify this presentation, we have omitted this feature;

however, it could be introduced to our approach.

Definition 5 (High-Level Message Sequence Charts). A high-level message

sequence chart (hMSC) is a graph of the form (N , E, so ) where N is a set of

nodes, E ⊆ (N × N ) is a set of edges, and s0 ∈ N is the initial node. We say

that n is adjacent to n0 if (n, n0 ) ∈ E. A (possibly infinite) sequence of nodes

w = n0 , n1 , . . . is a path if n0 = s0 , and ni is adjacent to ni+1 for 0 ≤ i < |w|. We

say a path is maximal if it is not a proper prefix of any other path.

We can now define positive MSC specifications; we refer to them as positive

so as to distinguish them from negative scenarios, which are introduced later

in Section 6. Positive MSC specifications consist of a set of bMSCs, a hMSC

and a function that maps every node in the hMSC to a bMSC. For simplicity,

we assume that all bMSCs have the same set of instances and that messages

are used consistently throughout them. In addition, we assume the mapping

from hMSC nodes to bMSCs to be bijective. Thus, several nodes referring to the

same bMSC are represented with several copies of the same bMSC, and each

node referring to an individual copy. This allows us to simplify by referring to

bMSCs instead of the nodes that are mapped to them. All these assumptions do

not reduce the generality of our results and help to simplify our presentation.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

45

Fig. 4. Weak sequential composition of bMSCs Analysis and Register.

Definition 6 (Positive Message Sequence Chart Specifications). A positive

message sequence chart (MSC) specification is a structure PSpec = (B, H, f )

where B is a set of bMSCs, H = (N , A, s0 ) is a hMSC, and f : N → B is

a bijective function that maps hMSC nodes to bMSCs. We use α(PSpec) =

{l | ∃b ∈ B. l ∈ α(b)} to denote the alphabet of the specification.

The semantics of a positive MSC specification is given, as for bMSCs, by a

set of traces. The hMSC together with the mapping of nodes to bMSCs shows

how the system can evolve from one scenario to another. There are two possible

interpretations of this evolution. The first is to assume that all components wait

until all events of a bMSC have occurred before moving on to the next bMSC.

This implies that there is some form of implicit synchronization that components use in order to know when a scenario has been completed. As MSCs are

a notation for making explicit how components interact to provide system level

functionality, we take the position that assuming implicit synchronization is

not appropriate. We adopt the second and more accepted approach to hMSC

semantics in which components move into subsequent scenarios in an unsynchronized fashion. This interpretation is referred to as using weak sequential

composition, and is the one adopted by the ITU [1996], among others. Note

that weak sequential composition is not a cause for implied scenarios. Strong

sequential composition could also be adopted and both the concept of implied

scenarios and the elaboration process would still hold. See Section 8.1 for more

details.

Definition 7 (Weak Sequential Composition of bMSCs). The weak sequential composition of two bMSCs b = (E, L, I, M , instance, label, order) and

b0 = (E 0 , L0 , I 0 , M 0 , instance 0 , label 0 , order 0 ) with disjoint sets of events is denoted (b• b0 ) and is defined by the bMSC (E ⊕ E 0 , L ∪ L0 , I ∪ I 0 , M ∪ M 0 , instance

∪ instance0 , label ∪ label0 , order• ), where ⊕ is disjoin union, and order• is the

set of total orders ≤•i such that e ≤•i e0 if and only if e ≤i e0 or e ≤0i e0 or (e ∈ i(E)

and e0 ∈ i(E 0 )).

For example, the bMSCs Analysis • Register (see Figure 4) determines two

possible traces: <query, data, command, pressure> and <query, data, pressure,

command>. Note that, in the latter, even though pressure is from the second

bMSC of the sequential composition, it occurs before command, which is from

the first bMSC of the sequential composition. This occurs because message

pressure is independent of command, that is, there is no causal relation between

the send events of these messages in (Analysis • Register). This is not surprising

as the messages involve different components, and as there are no explicit

synchronization mechanisms to enforce a particular ordering of these messages,

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

46

•

S. Uchitel et al.

any interleaving can occur. If strong sequential composition semantics were

used, command would be forced to occur before pressure. As explained before,

we believe this interpretation would be counterproductive, as it would assume

an implicit synchronization between components.

The traces determined by a positive MSC specification are those of any sequential composition of bMSCs according to a maximal path in the specification’s hMSC.

Definition 8 (Maximal bMSCs). Let PSpec = (B, H, f ) be a positive MSC

specification. We say that b is a maximal bMSC in PSpec if there is a maximal

path n1 , n2 , . . . in H such that b = f (n1 ) • f (n2 ) • · · · .

Definition 9 (Positive MSC Specification Semantics). Let PSpec be a positive MSC specification with a set of instances I . We define the behavior or

language of PSpec as a set L(PSpec) of traces, where L(PSpec) = {w ∈ L(b) | b

is a maximal bMSC of PSpec}.

Note that the semantics we use is trace-based. This differs from many other

approaches that use state-machine-based semantics (e.g., the ITU approach

[ITU 1996]). We discuss the significance of this difference at the end of this

article.

In summary, this section has defined a scenario-based language using MSC

syntax. This language has a trace-based semantics and can be used to (possibly

partially) describe the intended behavior of a system. In later sections of this

article, we extend the MSC notation to include negative scenarios for describing

behavior that a system is expected to prohibit. In terms of the process overview

depicted in Figure 2, we have so far presented the elements PSpec and L(PSpec)

at the top left corner.

3. ARCHITECTURE MODELS

3.1 Definitions

A MSC specification not only determines a set of acceptable system traces, it

also defines the intended architecture of the system. By architecture, we refer

to the components that implement system functionality and their interfaces,

that is, the messages they can send to and receive from other components. The

architectural description can be found in bMSCs, where instances model the

system components and the messages each instance sends and receives define

the component’s interface.

Definition 10 (Interfaces and Alphabets). Let PSpec = (B, H, f ) be a positive MSC specification with instances I , and let i ∈ I be an instance. The

interface of i is the set of message labels α(i) = {l | ∃b = (E, L, I, M , instance,

label, order) ∈ B and ∃e ∈ E such that label(e) = l and instance(e) = i}. We also

refer to the interface of i as its alphabet.

The construction of a model that complies with the architecture defined by a

positive MSC specification and that provides the behavior specified by the same

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

47

specification is a relevant issue. In this section, we show how this can be done

and explain to what degree these models comply with the original specification.

Labeled transitions systems (LTS) [Keller 1976] provide a suitable formalism

to model both the components and the systems described by MSC specifications.

Specifically, transitions are labeled with bMSC message labels, LTS processes

model system components and parallel composition of LTSs (based on the k composition operator used in CSP [Hoare 1985]) is used to define a system resulting

from several interacting components. The intuition behind parallel composition

of LTSs is that it defines a system that results from composing components such

that they execute asynchronously but synchronize on all shared message labels.

The formal definitions we now present have been adapted from Cheung [1994]

and Giannakopoulou [1999].

Definition 11 (Labeled Transition Systems). Let States be the universal set

of states where state π is the error state. Let Labels be the universal set of

message labels and Labelsτ = Labels ∪ {τ } where τ denotes an internal component action that is unobservable to other components. A LTS P is a structure (S, L, 1, q) where S ⊆ States is a finite set of states, L = α(P ) ∪ {τ },

α(P ) ⊆ Labels is a set of labels that denotes the communicating alphabet of

P, 1 ⊆ (S\{π } × L × S) defines the labeled transitions between states, and

l

q ∈ S is the initial state. We use s −→ s0 to denote (s, l , s0 ) ∈ 1. In addition, we

l

l

say that a LTS P is deterministic if s −→ s1 and s −→ s2 implies s1 = s2 .

Definition 12 (Parallel Composition of LTS). Let P1 and P2 be LTSs where

Pi = (Si , Li , 1i , qi ). Their parallel composition is denoted P1 kP2 and is an LTS

(S, L, 1, q) where S = S1 × S2 ∪ {π, ε}, L = L1 ∪ L2 , q = (q1 , q2 ), and 1 is the

smallest relation in (S\{π}) × L × S that satisfies the following rules where

a

x −→i y denotes (x, a, y) ∈ 1i :

a

a

s −→1 t

a

(s, s0 ) −→ (t, s0 )

a

(a ∈

/ α(L2 ))

s −→2 t

a

(s0 , s) −→ (s0 , t)

(a ∈

/ α(L1 ))

a

s −→1 ts0 −→2 t 0

a

(s, s0 ) −→ (t, t 0 )

(a ∈ (α(L1 ) ∩ α(L2 ))\{τ }).

The only exceptions to these rules are that we use state π instead of states

(x, π) and (π, x) for all x ∈ States. These exceptions mean that the composite LTS

reaches an error state if any of the composed LTSs do so. Note that the definition

of LTS includes a special message label τ . This label models an internal action

that is not observable to other LTSs. This is why the parallel composition does

not force synchronization on transitions labeled with τ . In addition, note that

parallel composition is both commutative and associative. Consequently, we

note parallel composition of multiple LTSs as follows: P1 k · · · kPn .

Given a LTS, we wish to compare the behavior it models with the behavior

of a positive MSC specification. Thus, we introduce the notion of maximal trace

for LTSs:

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

48

•

S. Uchitel et al.

Definition 13 (Executions). Let P = (S, L, 1, q) be a LTS. An execution of

P is a sequence w = q0l 0 q1l 1 · · · of states qi and labels l i ∈ L such that q0 = q

li

and qi −→ qi+1 for all 0 ≤ i < |w/2|. An execution is maximal if it cannot be

extended to still be an execution of the LTS. We also define ex(P ) = {w | w is an

execution of P }.

Definition 14 (Projection). Let w be a word w0 w1 w2 w3 · · · and A an alphabet. The projection of w onto A, which we denote w| A , is the result of eliminating

from the word w all elements wi in A.

Definition 15 (Traces and Maximal Traces). Let P be a LTS. A word w over

the alphabet α(P ) is a (maximal) trace of P if there is an (maximal) execution e ∈

ex(P ) such that w = e|α(P ) . We use tr(e) to denote the projection of an execution

on the alphabet of a LTS. We also define tr(P ) = {w | w is a trace of P } and

L(P ) = {w | w is a maximal trace of P }.

We now introduce the notion of architecture model. As commented before,

we wish to build a model that complies with the description given by a positive

MSC specification. This means building a model that takes into account both

the architecture and the behavior described by the MSC specification. Thus,

the model should be the parallel composition of a collection of LTSs, where

each LTS models a component in the MSC specification. Furthermore, the LTS

modeling a component of the MSC specification should have its corresponding

interface, which means that the alphabet of the LTS should coincide with that

of the component it models. Finally, the composite system model should be able

to exhibit all the traces described in the MSC specification. LTS models that

preserve the component structure and component interfaces while exhibiting

all specified traces are called architecture models.

Definition 16 (Architecture Models). Let PSpec = (B, H, f ) be a positive

MSC specification with instances I , and let Ai with i ∈ I be LTSs. We say that an

LTS A is an architecture model of PSpec only if A = (A1 k · · · kAn ), α(Ai ) = α(i),

and L(PSpec) ⊆ L(A).

For the Boiler Control system of Figure 4, an architecture model is one

which is the result of composing in parallel four LTSs: One with alphabet with

{pressure, on, off} modeling the Sensor component, another with alphabet {data,

query, pressure} modeling the Database component, a third modeling the Control component with alphabet {on, off, query, data, command} and a fourth

model for the Actuator component with alphabet {command}. In addition, all

traces defined by the semantics of the MSC specification must be maximal

traces of the composition of these four LTSs.

This notion of an architecture model is weak in that it permits additional

unspecified behavior. The interpretation is consistent with the fact that scenario specifications are partial descriptions, where typically only a subset of

significant system traces has been explicitly specified. In addition, as we see

later, strengthening the condition L(PSpec) ⊆ L(A) to L(PSpec) = L(A) would

result in MSC specifications with no architecture models.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

49

Fig. 5. Behavior of Control component in bMSC Analysis.

Fig. 6. Composition of Control’s behavior in all bMSCs.

3.2 Synthesis

We now discuss how architecture models are built from MSC specifications. In

particular, we describe the algorithm for building component models, that is, a

LTS for a component specified in a positive MSC specification. If all component

models are built using this algorithm, their parallel composition can be shown

to be an architecture model of the MSC specification.

The algorithm works by translating an MSC specification into a behavior

model specification in the form of Finite Sequential Processes (FSP) [Magee and

Kramer 1999]. FSP semantics is given in terms of LTSs. In order to simplify

this presentation, rather than describing the algorithm in terms of the FSP

it builds, we describe the LTSs determined by the FSP that is synthesized.

The algorithm synthesizes one component model at a time. We illustrate it by

explaining how it builds the LTS for the Control component of Figure 3.

Given a positive MSC specification and a component to be synthesized, the

algorithm constructs a deterministic LTS that has the same traces as the projection of the MSC behavior on the alphabet of the component. First, the algorithm

builds one LTS for each bMSC in the specification. Each of these LTSs exhibits

the same behavior as exhibited by the component in the bMSC. For instance,

the algorithm builds the LTS of Figure 5 to model the behavior of the Control component in bMSC Analysis. The numbers depicted in the states have no

particular meaning; they are simply references that permit reference to states,

facilitating explanations involving the LTS.

As one LTS for each bMSC is built, the algorithm must combine all these

processes to model the behavior of the component as it traverses the hMSC.

Thus, the second step of the algorithm is to link the LTSs according to the hMSC.

LTSs are linked by adding transitions labeled with intAction. For instance, the

last state of the LTS that corresponds to bMSC Analysis is linked to the first

state of the LTS modeling the Register bMSC. The LTS resulting from linking

the LTSs for all bMSCs in which Control participates is shown in Figure 6.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

50

•

S. Uchitel et al.

Fig. 7. Component model for Control.

Fig. 8. Component model for Database.

Fig. 9. Architecture model of the Boiler Control system.

The third is to make intAction unobservable and to minimize. Making

intAction unobservable involves replacing all its appearances with the internal action τ . This is called hiding and is denoted P \A where P is a LTS and A

is the set of actions being hidden (i.e., replaced by τ ).

The last step is to make the resulting LTS deterministic and minimize it

while preserving the maximal traces that it specifies. For the Control component, the final LTS is depicted in Figure 7.

Note that the synthesis algorithm described above behaves slightly differently when processing a specification with bMSCs that have no adjacent nodes

in the hMSC. In these cases, we use the auxiliary transition label endAction

to prevent the minimization algorithm from losing maximal traces. Hence, the

final step in building the component model is to hide the label endAction.

The algorithm described above must be applied to all components appearing in the MSC specification (see another example in Figure 8). Once in LTS

for each component has been synthesized, the complete system is their parallel composition. In the case of the Boiler Control system, the final architecture model is the parallel composition of component LTSs corresponding

to Control, Sensor, Database, and Actuator The composite LTS is depicted in

Figure 9.

From the following two lemmas, it is straightforward to show that the model

synthesized from a positive MSC specification using the algorithm presented

above is an architecture model of the input specification. A detailed proof can

be found in Uchitel [2003].

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

51

LEMMA 1. Let PSpec be a positive MSC specification. If A = (A1 k · · · kAn ) is

the synthesized architecture model of PSpec, then L(PSpec)|α(i) = L(Ai ).

LEMMA 2. If P1 · · · Pn are LTSs and w|α(i) ∈ L(Pi ) for all 1 ≤ i ≤ n, then

w ∈ L(P1 k · · · kPn ).

THEOREM 1. If A is the model resulting from applying the architecture model

synthesis procedure to a positive MSC specification PSpec, then A is an architecture model of PSpec.

Furthermore, we can also show that the synthesized architecture model is

minimal with respect to trace inclusion (refer to Uchitel [2003] for proofs).

Property 1. If A is the synthesized architecture model of positive MSC specification PSpec, then for any architecture model A0 , we have tr(A) ⊆ tr(A0 ).

In summary, with reference to the process overview in Figure 2, we have

now described its top portion: the positive scenario specification PSpec, the set

of traces defined by its semantics (L(PSpec)) and the architecture it defines.

We have shown how the architecture model synthesis algorithm builds a model

A = (A1 k · · · kAn ) such that L(PSpec) ⊆ L(A) and that it is minimal with respect

to trace inclusion.

4. IMPLIED SCENARIOS

In the previous section, we introduced the notion of an architecture model. Instead of requiring architecture models to provide the traces described in the

MSC specification exactly, we required only trace inclusion (L(PSpec) ⊆ L(A)).

As mentioned before, this is a reasonable notion considering that scenario specifications are inherently partial descriptions.

It is interesting to study how close an architecture model can be to the behavior explicitly described in a positive MSC specification. Is it possible to construct

an architecture model that captures exactly the specified behavior? It turns out

that, in some cases, this is not possible; that, for some MSC specifications,

all architecture models of the specification exhibit traces that have not been

specified in the MSC specification. Moreover, as we shall see, these traces are

particularly interesting as they uncover important gaps of the partial system

description that should be elaborated. In this section, we explain why these

situations occur and define the notion of an implied scenario. Subsequently, we

show how implied scenarios can be detected.

Applying the synthesis algorithm presented above, we can construct a FSP

model for the MSC specification of Figure 3. Once the FSP specification is fed

into the LTSA tool, we can animate our model to see how it behaves. In Figure 10,

we show a trace (using the bMSC syntax for clarity), which can be executed in

our system model. The trace shows how the Control component is accessing the

Database and receiving information from a previous activation of the Sensor.

This is clearly not specified behavior; there is no trace in the language defined

by of our MSC specification that has a prefix as shown in Figure 10. The MSC

specification states that, after initializing Sensor, there must be some data

registered into the Database before any queries can be done. Note that as the

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

52

•

S. Uchitel et al.

Fig. 10. First implied scenario of the Boiler Control system.

pressure message and the query message involve the Database, the trace of

Figure 10 cannot be a result of the interleaving of messages in some maximal

bMSC determined by the high-level MSC of Figure 3.

This means that our architecture model is introducing nonspecified system

behavior. We could try to build another architecture model that does not include

this trace. However, we have shown that the synthesized model is minimal

with respect to trace inclusion. Thus, we must conclude that the unspecified

trace of Figure 10 appears in all architecture models of the MSC specification.

How is this possible? This clearly concerns the requirement that architecture

models preserve the system’s component structure and component interfaces.

If we analyze the MSC specification from an architectural point of view, we

can see that what is happening is reasonable: the Control component cannot

observe when the Sensor has registered data in the Database; thus, if it is to

query the Database after data has been registered at least once, it must rely

on the Database to enable and disable queries when appropriate. However, as

the Database cannot tell when the Sensor has been turned on or off, it cannot

distinguish a first registration of data from others. Thus, it cannot enable and

disable queries appropriately. Succinctly, components do not have enough local

information to prevent the system execution shown in Figure 10. Note that each

component is behaving correctly from its local point of view, that is, it is behaving in accordance with some valid sequence of bMSCs. The problem is that each

component is following a different sequence of bMSCs! The Sensor, Control and

Actuator are going through scenarios Initialize, Register, Terminate, Initialize,

Analysis, and Register. However, the Database is performing Initialize, Register, Analysis, and Register. We use the term implied scenario (taken from Alur

et al. [2000], see section on related work) to refer to system executions such

as the one shown in Figure 10. In the definition below, we use “*” to denote the

operation that given a set of symbols produces the set of all strings over that

set.

Definition 17 (Implied Scenarios). Given a positive MSC specification

PSpec, a trace w ∈

/ L(PSpec) is an implied scenario of Spec if for all trace y

and for all architecture model A of Pspec, w. y ∈ L(A) implies w. y ∈

/ L(PSpec).

Property 2 (Implied Scenarios). If PSpec is a positive MSC specification

and a A is a minimal architecture model of PSpec, then PSpec has implied

scenarios if and only if L(A) 6⊂ L(PSpec).

In addition, we say that MSC specification is realizable (also taken from Alur

et al. [2000]) if the specification has no implied scenarios, or in other words, that

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

53

there is an architecture model that exhibits exactly the traces defined by the

MSC.

Definition 18 (Realizability). Let PSpec be a positive MSC specification,

and A an architecture behavior model of PSpec. A is a realization of PSpec if

L(PSpec) = L(A). We say that a PSpec is realizable if there is a realization of

PSpec.

An important observation on implied scenarios is that they are not an artifact of a particular language or semantics. For instance, implied scenarios can

occur when using strong sequential composition for MSC semantics. Implied

scenarios are the result of specifying the behavior of a system from a global

perspective that is to be provided by independent, interacting components that

have restricted local views. If the system architecture does not provide components with enough local information, they may not be able to avoid unspecified

system behavior, even if the are behaving correctly in terms of local behavior.

Note that weak sequential composition of bMSCs is not a cause for implied

scenarios. We discuss the nature of implied scenarios more extensively in the

Discussion and Related Work (Section 8).

Implied scenarios are not necessarily unwanted situations. They can simply

be acceptable scenarios that have been overlooked by stakeholders. This is not

surprising as scenario-based specifications are inherently partial. It is reasonable to assume that stakeholders do not provide a complete set of examples of

how the system is expected to behave. In this case, the implied scenario should

be added to the specification in order to extend it covering a case that had not

been explicitly described in the original system description. It is also possible,

however, that the implied scenario does represent unwanted system behavior.

In this case, careful documentation is needed so as to ensure that design decisions are taken at some point to prevent the scenario from happening. We

return to this in subsequent sections.

Consequently, implied scenarios should be taken to stakeholders for validation. By doing so, the MSC specification can be iteratively elaborated. An important comment is that implied scenarios expose subtle mismatches between

the architecture and behavior. Even in a toy example such as the Boiler Control system, the implied scenario we have discussed cannot be detected trivially

by observing the specification. Thus, there is great value in automatically detecting and validating implied scenarios as they force stakeholders to address

subtle yet crucial points regarding the concurrent nature of the system they

are specifying.

This section has defined implied scenarios. In terms of the overview depicted

in Figure 2, we have introduced the arrow on the bottom right corner. However,

we have yet to discuss implied scenarios in the context of negative scenarios.

5. IMPLIED SCENARIO DETECTION

We have shown how an architecture model can be constructed from a positive

MSC specification. We have also shown that it is possible for this model to

exhibit implied scenarios, and commented on how these can help elaborate

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

54

•

S. Uchitel et al.

MSC specifications if detected and validated with stakeholders. Consequently,

detecting implied scenarios is an important issue.

Our approach to implied scenario detection is conceptually very simple. We

know how to construct an architecture model and that this model includes all

specified traces and is minimal with respect to trace inclusion. If we build a

model that captures exactly the set of traces defined by the MSC semantics—

the trace model—we could compare its traces with those of the minimal architecture model. Any trace in the latter that is not a trace of the new model would

then correspond to an implied scenario. Of course, to build a precise model of the

specified traces we would have to ignore the architectural requirements specified in the scenario. In addition, such a (finite) model would only be possible

if the MSC behavior corresponds to a regular language [Ullman and Hopcroft

1979], which is not always the case.

Definition 19 (Regular MSC Specifications). A MSC specification Spec is

said to be regular if L(Spec) is a regular language. Otherwise, Spec is said

to be nonregular.

Nonregular MSCs are not realizable: there is no finite LTS that can model

the language, thus, there can be no set of finite LTS such that their composition

models it either. Fortunately, there are decision procedures that can be used

to check if a MSC specification as defined in previous sections determines a

regular language. It can be shown that the languages determined by our MSC

specifications are finitely generated MSC languages [Henriksen et al. 2000].

Thus, from Lemma 4.2 and 4.3 of Henriksen et al. [2000], the problem of checking if our MSC specification is regular is equivalent to checking that the MSC is

bounded. The notion of bounded MSCs was introduced in Alur and Yannakakis

[1999] which is defined in terms of the communication graph of a set of bMSCs.

In our setting, a communication graph for a set of bMSCs would have a node

for each component; the set of arcs would be the transitive closure of the set of

arcs defined by the fact that two components communicate over a message in

some bMSC of the set. The boundedness condition states that for any cycle in

the hMSC, the communication graph for the bMSCs in that cycle determines

one nonempty set of fully connected components. For an example of unbounded

hMSC, see Uchitel [2003]. In the rest of this article, we assume bounded MSC

specifications. We now explain how we build a model of the intended system

behavior from such positive MSC specifications.

5.1 Trace Models

One of the difficulties of building a LTS model that captures the specified traces

of a positive MSC specification is that such model cannot be constructed compositionally from the bMSCs appearing in the MSC specification. This is because

of the weak sequential composition used in hMSC semantics. Components may

move asynchronously from one bMSC to another, thus a message from a bMSC

that appears before another bMSC in a maximal path of the hMSC is not guaranteed to occur before the messages of the latter bMSC.

Our approach is to build a set of component LTS models that extend (in

terms of architectural capabilities) those described in the MSC specification.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

55

The extension is that components must request permission to a Coordinator

component before moving from one bMSC to another. In addition, we build

a Coordinator that enables and disables component entry requests to bMSCs

guaranteeing that components do not follow different sequences of bMSCs.

It is important to note that, in this section, we define a model that is not an architecture model. First, we have added a component into the system that has not

been specified in the MSC specification: the Coordinator. Second, the LTS models for components appearing in MSC specifications have an extended alphabet

that includes labels that do not appear in the MSC specification. Note that it is

not our intention to propose a refined architecture or design solution that avoids

implied scenarios. This would be incorrect, as it would be assume that implied

scenarios are unwanted system traces. This is not necessarily so. Our intention

is to build an artifact that allows us to detect implied scenarios by comparing

its traces against those of a minimal architecture model.

The reason we choose the Coordinator approach is that it is possible to show

that all implied scenarios exhibited by an architecture model are the result of

components exhibiting behaviors described by different paths in the hMSC. In

other words, the behavior of each component is correct with respect to its local

view of what is occurring in the system.

PROPOSITION 1. If w is an implied scenario of MSC PSpec, then, for each

instance i, there is a maximal bMSC bi such that w|α(i) ∈ L(bi )|α(i) .

If w is an implied scenario of PSpec, and A = A1 k · · · kAn is an architecture

model for PSpec, then w ∈ L(A). From Lemma 1, we have L(PSpec)|α(i) = L(Ai )

for each instance i. This means that there must be a maximal bMSC bi such

that w|α(i) ∈ L(bi )|α(i) . However, because w is an implied scenario of PSpec, there

can be no maximal bMSC b such that w ∈ L(b). Hence, the following holds

w|α(i) ∈ L(bi )|α(i) for each instance i, but there are at least two maximal bMSCs

bi and bi’ that are different maximal bMSCs. In summary, the implied scenario

is the result of at least two different instances following different maximal

bMSCs.

Consequently, if we build components and coordinate them in such a way that

they all go through the same hMSC path, implied scenarios will be avoided. We

now show how this can be done.

In the previous section we presented a synthesis algorithm that builds LTS

models for each component appearing in a positive MSC specification. The LTS

models we now build are an extension of those; we call them extended component models. Instead of using an internal action for linking component behaviors corresponding to each bMSC, we use a coordination action. Coordination

actions are labeled with a component name and a bMSC name, and model the

request of the component to enter the bMSC. For component Control the coordination actions that we use are Control.Initialise, Control.Register,

Control.Analysis, Control.Terminate. Figure 11 depicts the final behavior

of the extended Control component.

It is clear that that the behavior resulting from hiding coordination actions

in an extended component Ei is trace equivalent to that of the component model

synthesized for the architecture model. Thus, the above proposition motivates

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

56

•

S. Uchitel et al.

Fig. 11. Extended Control with coordination actions.

construction of a Coordinator component Coord that synchronizes on component coordination actions and forces components to follow the same maximal

bMSC. The resulting system, (E1 k · · · kEn kCoord), restricted to the MSC alphabet does not exhibit any implied scenarios; it is an exact model of the specified

MSC traces. In summary, we use a Coordinator component that keeps track

of the path (maximal bMSC) being taken by the leading component and that

forces all other components lagging behind to follow the same path. We now

define such a Coordinator.

Intuitively, the Coordinator state space consists of states that model a path

in the hMSC and the position of each component in that path. However, there

is no need to keep track of the whole path followed by components (which is

fortunate, as the path is potentially infinite). It suffices to record the bMSCs the

leading component has gone through and which the components further behind

have not yet reached. The sequence can be thought as the destiny of the component that is furthest behind and that is being decided by the component that is

furthest in front. For example, the state (2, 2, 3, 1, Initialize.Register.Analysis)

corresponds to the Boiler Control System state where components Sensor,

Database are in bMSC Register, Control is in bMSC Analysis while Actuator

is in bMSC Initialize and has not requested the Coordinator for permission to

move into Register. In this state, the action s Sensor Register that models the

Sensor component requesting permission to enter bMSC Register would not be

enabled as Sensor must follow the leading component into bMSC Analysis. We

do not provide the formal definitions of the Coordinator or its finite version. For

a detailed discussion, refer to Uchitel [2003].

Given an MSC specification, we can construct extended components and a

finite coordinator from it, and compose them in parallel. We can then hide the

coordination actions in the composite model and obtain a model with the same

alphabet as the original MSC specification. We call this model the trace model.

Definition 20 (Trace Models). Let PSpec be a positive MSC specification,

E 1 , . . . , En the set of synthesized extended components from PSpec and H

is the set of all coordination actions. We define the trace model of PSpec as

(E1 k · · · kEn kCoordf )\H.

From the definition of extended components and that of the finite coordinator,

it can be shown that the trace model of a MSC specification has the same traces

as those defined by the MSC specification. For a proof of this result, refer to

Uchitel [2003]. In Figure 12, we depict the trace model of for the Boiler Control

system.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

57

Fig. 12. Trace model for the Boiler Control system.

Fig. 13. Implied Scenario detected by LTSA.

THEOREM 2. Let PSpec be a positive MSC specification, E1 , . . . , En the

set of synthesized extended components from PSpec and H is the set of

all coordination actions. If Coordf is a finite Coordinator of PSpec, then

L((E1 k · · · kEn kCoordf )\H) = L(PSpec).

5.2 Implied Scenario Detection Using LTSA

As discussed previously, to detect implied scenarios, we now need to check

L(A) ⊆ L((E1 k · · · kEn kCoordf )\H). We know how to build an FSP representation of both the trace model and the minimal architecture model; thus, we

can use LTSA to check trace inclusion. To do this, we declare the trace model

as a safety property and perform a safety check on the architecture model to

see if it satisfies the property. Safety properties, in LTSA, are created using

the property keyword. This extends a LTS with an error state e, and for every

state s and every label l , adds a transition labeled l from s to e if l was not

enabled in s. The safety property must then be composed in parallel with the

model to be checked. The error state is reachable from the initial state if and

only if the safety property is violated. Note that the safety check verifies that

tr(A) ⊆ tr((E 1 k · · · kEn kCoordf )\H). In addition, it is straightforward to prove

that if the model has no deadlocks, then we also have L(A) ⊆ L((E1 k · · · kEn k

Coordf )\H).

When performing a safety check, LTSA checks if the error state is reachable and also if there are deadlocks. Thus, a safety check on ImpliedScenario

Property either confirms that there are no implied scenarios or produces an

implied scenario. Furthermore, in the case of a safety violation, as opposed to

deadlock detection, the last message label of the implied scenario is the first

message that corresponds to unspecified behavior. This point in the implied

scenario is where the architecture model deviates from specified behavior.

In the Boiler Control System, the LTSA output indicating that an implied

scenario exists is shown in Figure 13. It corresponds to the implied scenario we

have been discussing in previous sections (see Figure 10).

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

58

•

S. Uchitel et al.

5.3 Coordinator State Space Reduction

In Section 5.1, we discussed how to build a model of the MSC behavior using

a Coordinator. Although the state space of the Coordinator we have defined is

finite, it can be extremely large. The size of the state space is in the order of

(CB)C where B is the number of basic MSC and C the number of components.

The size of the state space can be explained as follows: the equivalence relation

allows the elimination of a loop from the sequence of bMSCs in a state if there

is no component currently in the loop. The worst case is that the bMSCs form

one big loop of length B and components are positioned in such a way that every

component is in a different iteration of the loop. As there are C components, the

maximum length of the sequence of bMSCs is in the order of CB. In addition,

each component can be in a different position in the sequence of bMSC, thus

the resulting state space is of size (CB)C .

The size of the Coordinator state space is large, in part, due to the fact that

we are constructing the Coordinator taking into account very little information

from bMSCs. In other words, our Coordinator accepts combinations of requests

to enter bMSCs that never occur. This is because the interactions between

components in order to complete bMSCs and move on prevent certain sequences

of coordination actions from occurring. Consequently, it is possible to trim the

size of the Coordinator considerably introducing some heuristics that take into

account the dependencies between components in bMSCs.

In this article, we are concerned with showing how implied scenarios can be

used to evolve scenario-based specifications and behavior models. We therefore

do not discuss the issue of coordinator state space size and heuristics to reduce

it. The interested reader can refer to Uchitel et al. [2002b] where we present a

series of heuristics that, for some examples, can achieve up to 90% reduction

in the reachable coordinator state space.

In summary, in terms of Figure 2, we have now described the middle section

by showing how from a positive scenario specification (PSpec), using the traces

it defines (L(PSpec)), a trace model can be built (T = (E1 k · · · kE1 kCoordf )\H)

such that it describes exactly the specified traces (L(T ) = L(PSpec)). We have

also shown how to detect implied scenarios by model checking (L(A) ⊆ L(T )).

We now go on to talk about negative scenarios, constraint models and how

we can continue to validate implied scenarios in the presence of negative

scenarios.

6. NEGATIVE SCENARIOS

In this section, we create the need for documenting implied scenarios that are

deemed unacceptable system behavior by stakeholders. We introduce a negative

scenario as a notation for documenting these rejections and discuss how implied

scenarios can be detected in the presence of negative scenarios. In fact, we

provide three kinds of negative scenario. The first is a very simple notation

that allows stakeholders to rapidly reject implied scenarios, in a push button

style, and to continue checking for more implied scenarios. The other two are

more expressive notations that are needed to take the MSC specification to a

state where all implied scenarios have been validated.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

59

Fig. 14. A basic negative scenario.

6.1 Basic Negative Scenarios

Let us suppose that the implied scenario of Figure 10 is taken back to stakeholders for validation. In addition, suppose that stakeholders understand that

a query is retrieving old information from the Database because the last pressure reading is from a previous Sensor session. Consequently, they decide that

the implied scenario is unacceptable system behavior.

A first reaction could be to require stakeholders to review the MSC specification they have provided and to correct it so as to avoid the mismatch that

gives rise to the implied scenario. However, the only way to avoid the implied

scenario is through design. Stakeholders would have to contrive mechanisms,

such as additional synchronization messages and/or new components, to prevent the implied scenario from occurring. This approach is unsatisfactory for

a number of reasons. Stakeholders may lack the technical skills to make such

design decisions; taking such design decisions at an early requirement stage

may be undesirable; and finally, having to stop the process of model elaboration

to solve design issues may be inopportune.

We believe that documenting rejected implied scenarios and then producing

more feedback in terms of implied scenarios can make the elaboration process

more dynamic. In addition, it would allow explicit documentation of undesired

situations as opposed to doing so implicitly by providing a design solution.

Thus, we extend the notions discussed in previous sections to include negative

scenarios, a notation for documenting behavior that the system is expected to

prohibit. We now define a simple form of negative scenario and explain how to

detect implied scenarios when this form of negative scenarios is used.

We depict basic negative scenarios as bMSCs with three additional characteristics. The first is that the last message is crossed out; the second is that the

last message is separated from previous messages by a dashed line; the third

is the arrow on the top part of the scenario. Figure 14 shows an example of a

basic negative scenario. The part of the bMSC that is above the dashed line is

called its precondition; the message that is crossed out is called the proscribed

message. Intuitively, the meaning of basic negative scenarios is that once a

trace described by the precondition has occurred, the next message should not

be the proscribed message. The dotted line is to convey that the precondition

must occur completely before the crossed out message is proscribed (i.e., partial

orderings between the proscribed message and messages in the precondition

are not considered). Note that the precondition describes system behavior from

its initial state. To emphasize this, we have added the black dot and arrow

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

60

•

S. Uchitel et al.

(as used to indicate the initial hMSC node) above the negative scenario. The

scenario in Figure 14 specifies that the system may not exhibit traces with the

following prefix: on, pressure, off, on, query.

Definition 21 (Basic Negative Scenarios). A negative scenario n is a pair

( p, l ) where p is a bMSC, and l is a message label. We use α(n) to denote

α( p) ∪ {l }.

Formally, a basic negative scenario can be defined as a pair ( p, l ) where p

is a bMSC modeling the negative scenarios precondition, and l is the label of

the proscribed message. In terms of expressiveness, basic negative scenarios

are very limited. This is deliberate as we wish to keep this notation as simple

as possible. Our intention is to use basic negative scenarios to reject implied

scenarios in a very simple, push-button way. It is clear that moving from the

implied scenario to the negative scenario notation is trivial for whoever decides

on rejection. This is our intention. Simplicity in rejecting implied scenarios is

crucial if we are to have a dynamic elaboration process.

In the remainder of this article, given an implied scenario w = w1 lw2 , where

l is the point where the w deviates from specified behavior, we say that a negative scenario results from rejecting w if it has been constructed with a bMSC

that models w1 and proscribes message l . In practical terms, this is equivalent

to using the LTSA output to trivially build Neg1. Consequently, the negative

scenario of Figure 14 results from rejecting the implied scenario of Figure 10.

We must now define what basic negative scenarios mean in the context of

MSC specifications. We need to consider that MSC specifications comprise both

a positive and a negative part. The positive part consists of a high-level MSC

and its corresponding basic MSCs; this corresponds to our previous definition of

positive MSC specifications. The negative part consists of a set of basic negative

scenarios. Additionally, we require labels to denote messages consistently in

both positive and negative parts of a MSC specification.

Definition 22 (MSC Specifications). A MSC specification is a structure

Spec = (PSpec, NSpec) where PSpec a positive MSC specification as described

in Section 2 and NSpec is a set of negative scenarios. We use α(Spec) to denote

the union of the alphabets of the scenarios in PSpec and NSpec.

Definition 23 (Basic Negative Scenario Semantics). Let Spec = (PSpec,

NSpec) be a MSC specification, and n = ( p, l ) a basic negative scenario in

NSpec. The set of traces proscribed by n is L(n) = {w.l.w0 ∈ α(Spec)* | w ∈ L( p)}.

We also define L(NSpec) as the union of the all L(n) with n ∈ N .

An initial approach to the semantics of a MSC specification could be to consider it as the set of traces specified by the positive part that do not have a

prefix specified by the negative part of the specification. However, we actually

expect no such trace. This would signify an inconsistency in the specification as

the trace would be both described as acceptable and unacceptable. We therefore

introduce the notion of inconsistency:

Definition 24 (Inconsistent MSC Specifications). Given a MSC specification Spec = (PSpec, NSpec). The specification is said to be inconsistent if

L(PSpec) ∩ L(NSpec) 6= ®.

ACM Transactions on Software Engineering and Methodology, Vol. 13, No. 1, January 2004.

Scenario-Based Specifications and Behavior Models

•

61

The addition of a basic negative scenario to a MSC specification does not

always result in an inconsistency. In particular, this is the case if the basic

negative scenario is the result of rejecting an implied scenario. By definition,

an implied scenario is not part of the specified behavior, thus a basic negative

scenario resulting from it does not subtract traces from the positive part of

a MSC specification. In the Boiler Control system example, the behavior in

Figure 10 describes an implied scenario because no specified behavior can have

the prefix: on, pressure, off, on, query. It follows that the negative scenario of

Figure 14 does not subtract any traces from those specified in Figure 3. Thus,

we have the following property:

Property 3. Let Spec = (PSpec, NSpec) be a consistent MSC specification.

Let w be an implied scenario of PSpec and n the basic negative scenario resulting